Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

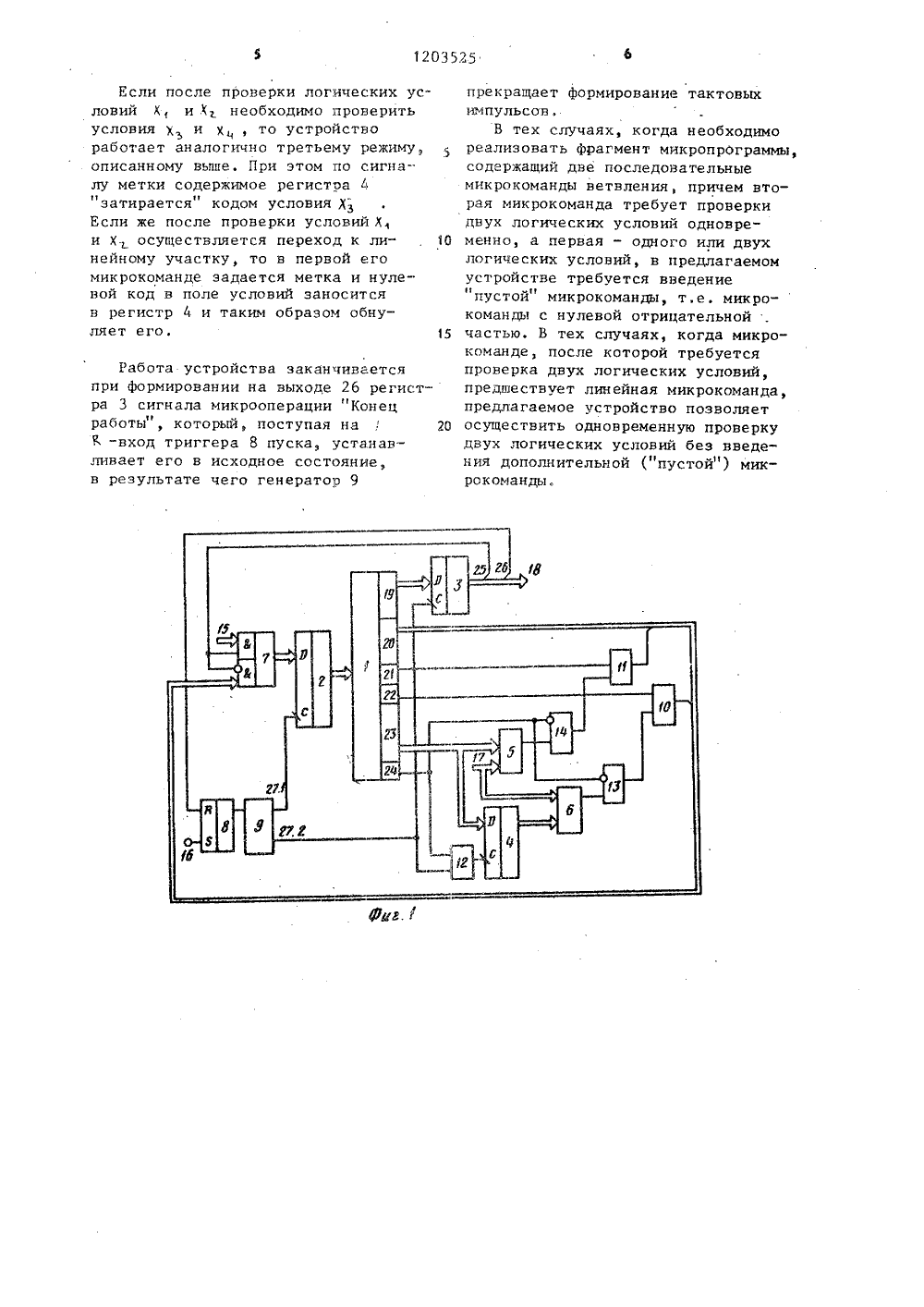

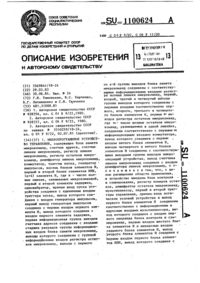

дами о с еса и ре ой выход ульсов сое ервого эле Ьйй единен с тра логи оторого сое дом второгогических с инфор- ьтиплекго и второго ицируемых разряго запоминающеман динен рым входом элеменнены с рого рых соед иной час ционного адвхо ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ 3710091/24-2411.03.8407.01,86. Бюл. У 1В.П. Супрун, В.С. Харченко,Тимонькин, В.А. Малахов,Ткаченко и К.10. Воробьев681.32(088,8)Авторское свидетельство СССР356, кл. С 06 Р 9/22, 1980.йоров С,А., Новиков Г.И.тура ЭВМ. - Л.: Машиностроение,с. 312-3 14, рис. 10.4.(54) (57) МИКРОПРОГРАММНОЕ УСТРОЙСТВОУПРАВЛЕНИЯ, содержащее постоянноезапоминающее устройство микрокоманд, регистр адреса, регистр микроопераций, коммутатор адреса, первый мультиплексор, триггер пуска игенератор тактовых импульсов, причемвход пуска устройства соединен с5- входом триггера пуска, выход которого соединен с входом генераторатактовых импульсов, выход коммутатора адреса соединен с информационным входом регистра адреса, выходкоторого соединен с адресным входомпостоянного запоминающего устройствамикрокоманд, выходы микрооперацийи немодифицируемой части адреса которого соединены соответственно с информационными входами регистра микроопераций и входами немодифицированной части адреса первого информационного входа коммутатора адреса,выход микроопераций регистра микроопераций соединен с выходом устройства, выход микрооперации "Конецработы" регистра микрооперацийсоединен с К -входом триггера пуска, выход логических условий постоянного запоминающего устройства микрокоманд и вход логических условийустройства соединены соответственно,с управляющим и информационными входами первого мультиплексора, о т -л и ч а ю щ е е с я тем, что, сцелью повышения быстродействия, оносодержит регистр логических условий,второй мультиплексор, первый, вто.рой и третий элементы И, первый ивторой элементы ИЛИ, причем входкода операции устройства соединенс вторым информационным входомкоммутатора адреса, первый и второйвыходы генератора тактовых импульсов соединены соответственсинхронизации регистрагистра микроопераций,генератора тактовых имдинен с первьв входоммента И, выход которогвходом синхронизации рческих условий, выходдинен с управляющим вхмультиплексора, вход лусловий устройства соемационным входом второ ора, вход которого соединен с пряым входом второго элемента И, выходоторого соединен с первым входомервого элемента ИЛИ, выходы пердов адреса постоянн го устройства микро соответственно с вт вого и первым входо тов ИЛИ, выходы кот входами модифициров реса первого информкоммутатора адреса, выход кодалогических условий постоянного запоминающего устройства микрокомандсоединен с инФормапионным входомрегистра логических условии, выхоц метки постоянного запоминающего устройства микрокоманд соединен с вторым входом первого и инВерсными входами второго и тре гьего 120352элементов И, выход первого мультиплексора соединен с прямым входом третьего элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, выход микрооперации Конец команды регистра микроопераций соединен с управляющим Входом коммутатора адре Изобретение относится к Явтомат".д И ВЬ"т",ИГ гит И чотл ТЕХНИ(р Имо)гет быть использовано при построении центральных и периФерийных устройств управления ЭБ 11 и вычислительных систем.,Цель изобретения - повьппениебыстродействия.Бя Фиг, 1 изображена Функциональная схема микропрограммного устройства управления, на Фиг. 2 - схемапоясняющая работу устройства.Устройство содержит постоянноезапоминающее устройство ПЗУ) 1 микрокоманд, регистры 2-4 адреса, микГоопераций и логических условийсоответственно, первый 5 и второй 6мультиплексорь, ХОммутатОр 7 адреса,триггер 8 пуска. генератор 9 тактоВьх импульсов первый 10 и второй11 элементы ИПИ первый 12, второй13 и третий 14 элементы И, входы 15.кода операции, 16 пуска и 17 логических условий устройства, выход18 устройства, выходы 19-24 микроопераций, немодиФицируемой частиадреса, второго и первого модиФицируемых разрядов ацреса кода логичес.них усий и метки постоянного запоминающего устройства микрокомандсоответственно Выходы 25 и 26 микрооперацииКонец команды" и Конецработы" соответственно, первый 27.1.и 27,2 Второй выходы генераторатактовых импульсов соответственно.Устройство работает следующимобразом. В исходном состоянии все элементы схемы находятся В нулевом состоянии, а в разряде регистра 3 микро-. Оперяцийр соответствующем микрООпе" рации "Конец команды" (Выход 25),записана ециница (цепи приведениясхемы в исходное состояние не показаны). По сигналу Пускл поступающему через вход 16 устройства на5-Вход триггера 8, последний устанавливается в единичное состояние.При этом на выходах генератора 9Возоуждаются последовательности так товых импульсов.11 О первому тактовому импульсу 1. 5поступающему на синхровход регистра2 адреса, последний открывается,При этом код операции, являющийсяадресом первой микрокоманды выполняемой микропрограммы, через коммутатор 7 поступает на инФормационныйВход регистра 2 адреса, По записанному В регистре 2 адресу в ПЗУ 1микрокоманд выбирается соответствующая микрокоманда и поступает наего выходы 19- 24, При наличиисигнала на синхровходе регистра 3микроопераций операционная частьмикрокоманды с выхода 19 поступаетна инФормационный вход регистра 3микроопераций. Сигналы микроопераций с регистра 3 микроопераций поступают на выход 18 устройства.При Формировании адреса очередной микрокоманды возможны следующиережимы работы устройства;Формирование адреса очередноймикрокоманды при выполнении линей;"15ных участков микропрограмм без проверки логических условий,Формирование адреса очеедной микрокоманды при проверке одногологического условия;30Формирование адреса очередноймикрокоманды при проверке двухлогических условий одновременно, 1203525Рассмотрим работу устройства в этих режимахПервый режим. При считыванииФмккрокоманды из ПЗУ 1 мккрокоманд адрес очередной микрокоманды формируется следующим образом. Немодифкцируемая часть адреса очередной микрокоманды с выхода 20 поступает на соответствующие входы первого информационного входа коммутатора 7 адреса. Значение модифицируемых разрядов адреса очередной микрокоманды поступает с выходов 21 и 22 через элементы ИЛИ 11 и 10 на вход коммутатора 7. Поскольку в поле 23 и ре. гистре 4 при этом записан нулевой код, то на,выходе мультиплексоров 5 и 6 и элементов И 13 и 14 присутствуют нулевые сигналы. Ввиду отсутствия сигнала микрооперации 11 Конец команды адрес очередной микрокоманды через коммутатор 7 поступает на информационный вход регистра 2 адреса. При формировании на выходе 27.1 генератора 9 очередного тактового импульса адрес мккроксманды записывается в регистр 2 адреса. Далее устройство работает в этом режиме аналогично описанному выше.Второй режим. Если при выполне, нии текущей мккрокоманды необходимо проверить значение логического условия и произвести ветвление микропрограммы, то на выходе 23 ПЗУ микрокоманд будет считан код этого логического условия. Значения логических условий с входа 17 поступают на первый мультиплексор 5. Формирование значения модкфицкруемого разряда адреса очередной микрокоманды осуществляется на втором элементе ИЛИ 11 путем реали, зации логической функции где- значение модифицируемогоразряда адреса очередноймикрокоманды на выходе21 ПЗУ 1 микрокоманд (вмикрокоманде ветвления4 =О); Х, - значение проверяемого логическогс условия, формируемого на выходе мультиплексора 5.Значение сигналапоступает на вход модифицированных разрядов адреса первого информационного входа коммутатора 7 адреса. Посколь 15 20 25 30 ч 5 40 45 50 55 ку в регистре 4 при этом сохраняетсянулевой код, тс сигнал на выходемультиплексора 6 равен нулю к модификации второго адресного разряда непроисходит.Третий режим. Если при выполнении микрокоманд необходимо реализовать проверку двух логических условий, то предлагаемое устройство работает следующим образом. При считывании микрокоманды А;, на выходе24 ПЗУ 1 микрокоманд присутствуетединичный сигнал - метка. По второму тактовому импульсупроисходит запись операционной частимикрскоманды А;в регистр 3 изапись кода логического условия врегистр 4 логических условий.Метка запрещает прохождение сигналовчерез второй 13 к третий 14 элемен"- ты И, блокируя тем самым модификацию младших адресных разрядов. Формирование адреса микрокоманды А;содержащей код второго проверяемогологического условия Х , т,е. собственно микрокоманды ветвления пролисходит по очередному импульсупосле его окончания метка пропадает, второй 13 к третий 14 элементы И открываются. По. происходитсчитывание операционной части микрокоманды А;Код логического условия Х поступает на мультиплексор 5, а кодлогического условия М - на мультиплексор 6. С входа 17 значениялогических условий подаются на информационные входы мультиплексоров5 к 6. Значения проверяемых условийК к Х с выходов мультиплексоров5 к 6 через открытые элементыИ 14 и 13 поступают на элементыИЛИ 11 и 10. Модифицированные разряды адреса очередной мккрокомандыА;+1 поступают на входы модифицированной части разрядов адреса первогоинформационного входа коммутатора7 адреса.Механизм модификации в этом режиме полностйо аналогичен описанному во втором режиме. Отличиесостоит лишь в том, что при этомна элементах ИЛИ 10 и 11 модифицируются (изменяются с нуля на единицу при единичном значении условийи) два младших разряда одновременно, что позволяет осуществлять ветвление по трем - четырем направлениям.Если после провеРки логических условий 1, и .1 необходимо проверить условия Х и у, то устройство работает аналогично третьему режиму, описанному выше. При зтом по сигналу метки содержимое регистра 4 11затирается кодом условия 3 Если же после проверки условий М и М осуществляется переход к линейному участку, то в первой его микрокоманде задается метка и нулевой код в поле условий заносится в регистр ч и таким образом обнуляет его. 10 Работа устройства заканчивается при формировании на выходе 2 б регистра 3 сигнала микрооперации "Конец работы", который, поступая на 20 1 -вход триггера 8 пуска, устанавливает его в исходное состояние, в результате чего генератор 9 прекращает формирование тактовых импульсов.В тех случаях, когда необходимо реализовать фрагмент микропрОграммы, содержащий две последовательные микрокоманды ветвления, причем вторая микрокоманда требует проверки двух логических условий одновременно, а первая - одного или двух логических условий, в предлагаемом устройстве требуется введение 13 гфпустои микрокоманды, т.е. микро- команды с нулевой отрицательной частью. В тех случаях, когда микрокоманде, после которой требуется проверка двух логических условий, предшествует линейная микрокоманда1 предлагаемое устройство позволяет осуществить одновременную проверку двух логических условий без введения дополнительной (" пустой" ) микрокоманды1203525 б ъ1с Г Составитель Техред А.Войк огачева Редактор В.П орректор И.Муска Заказ 8418/ дпнс а СС наб., д. 4 иал ПП 1 "Патент", г. Ужгород, ул, Про Тираж 7 НИИПИ Госуда по делам и 13035, Москв

СмотретьЗаявка

3710091, 11.03.1984

ПРЕДПРИЯТИЕ ПЯ А-7160

СУПРУН ВАСИЛИЙ ПЕТРОВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, МАЛАХОВ ВИКТОР АЛЕКСАНДРОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ВОРОБЬЕВ КОНСТАНТИН ЮРЬЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 07.01.1986

Код ссылки

<a href="https://patents.su/5-1203525-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство для контроля цифровых систем

Следующий патент: Устройство для контроля микропрограммного блока управления

Случайный патент: Устройство для ультразвуковойдефектоскопии