Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

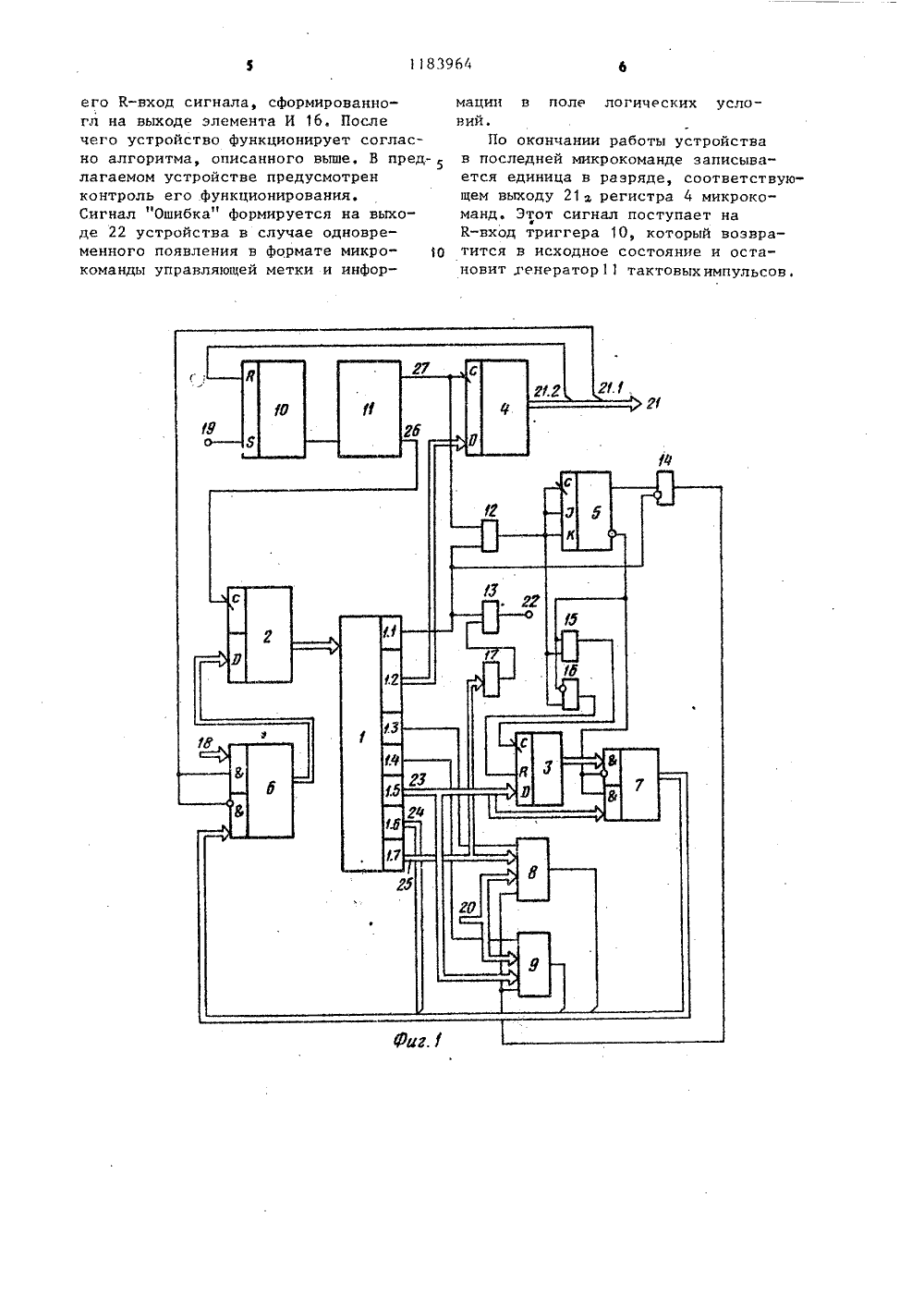

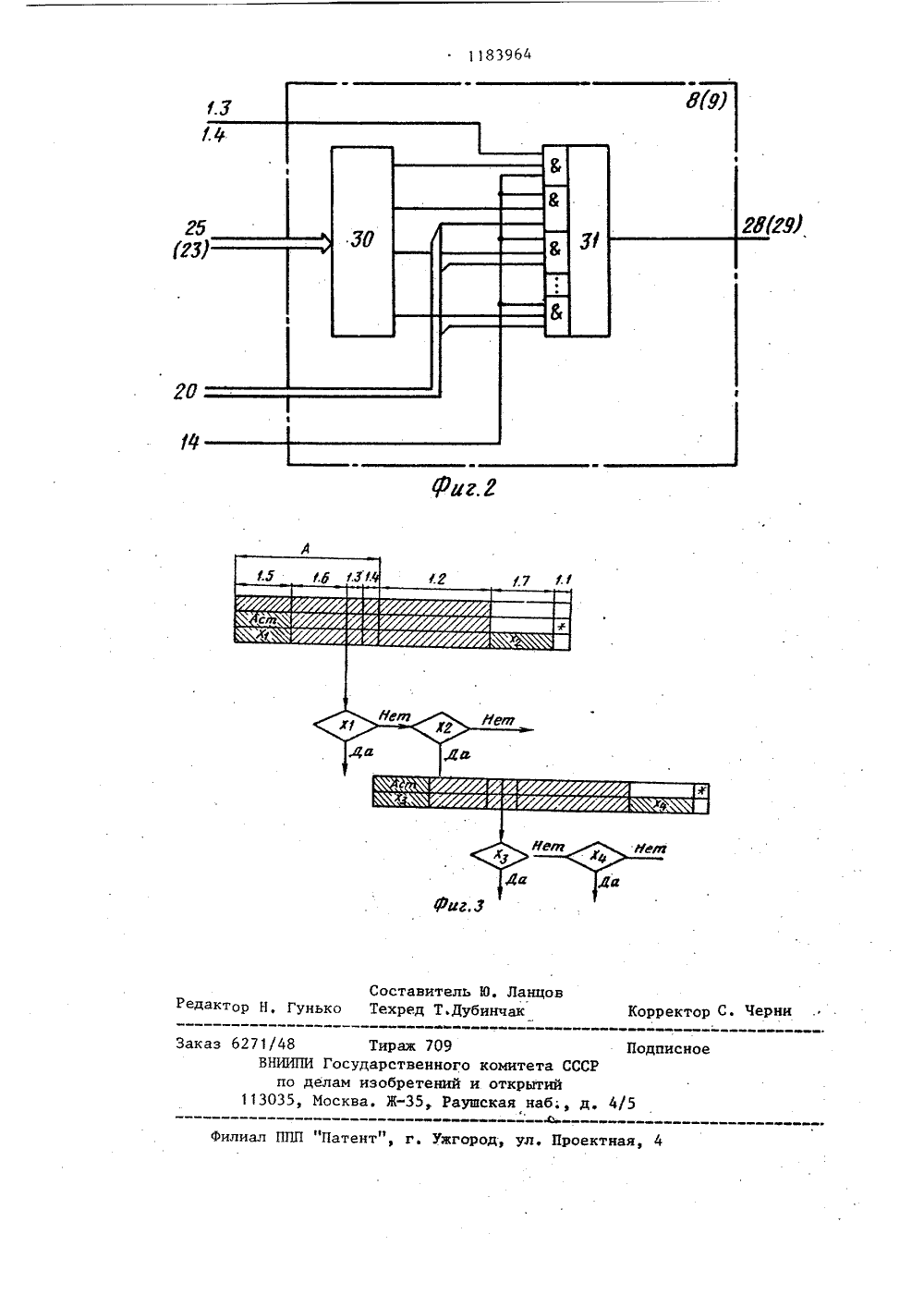

(5)4 С 06 Р 9 НИЯТ 0 РСН 0 МУ :ИД.:ТЛСТУ ких условий устройства соединен с первым информационным входом первого мультиплексора, выход которого соединен с информационным входом первого старшего разряда первой группы первого коммутатора адреса, входы младших разрядов первой группы которого соединены с выходами мпадших разрядов кода адреса блока памяти микрокоманд, выход первого коммутатора адреса соединен с информационным входом регистра адреса, выход признака конца команды регистра микрокоманд соединен с управляющим входом первого коммутатора адреса, вторая группа информационных входов которого является группой входов кода команды устройства, о т л и ч а ю щ е е с я тем, что, с целью сокращения объема оборудования за счет снижения объема блока памяти микрокоманд, оно со- держит буферный регистр, триггер условий, второй коммутатор адреса, второй мультиплексор, первый, второй, третий, четвертый и пятый эле,менты И и элемент ИЛИ, причем первый выход генератора тактовых импульсов соединен с входом синхронизации регистра микрокоманд и с первым входом первого элемен. та И, второй вход которого соединен с инверсным входом третьего элемента И, с выходом признака предшествующей ветвлению микрокоманды блока памяти микрокоманд и с первым входом второго элемента И, второй входкоторого соединен с выходом элемента ИЛИ, вход которого соединен с выходом кода логических условий блока памяти микрокоманд,ькин,ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ ОПИСАНИЕ ИЗОБР(56) Авторское свидетельство СССР У 928356, кл, С 06 Р 9/22, 1980.Хассон С. Микропрограммное управление. - М.: 1974, ч.1, с.37-42, рис. 2. 1, 2. 2.Майоров С.А., Новиков Г.И. Структура ЭВМ.-Л,: Машиностроение, 1979, с. 312 - 317, рис. 10.5. (54)(57) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок памяти микрокоманд, регистр адреса, регистр микрокоманд, первый мультиплексор, первый коммутатор адреса, триггер пуска и генератор тактовых импульсов, причем вход пуска устройства соединен с входом установки в единицу триггера пуска, выход которого соединен.с входом запуска генератора тактовых импульсов, выход регистра адреса соединен с адресным входом блока памяти микро- команд, выход кода микроопераций которого соединен с информационным входом регистра микрокоманд, выход кода микроопераций которого является управляющим выходом устройства, выход признака конца работы регистра микрокоманд соединен с входом установки в ноль триггера пуска, выход кода логических условий блока памяти микрокоманд соединен с управляющим входом первого мультиплексора, вход логичесЯ 011839641183964 выход старших разрядов кода .адресакоторого соединен с информационнымвходом буферного регистра, с первыминформационным входом второго комму"татора адреса и с управляющим вхо -дом второго мультиплексора, первыйинформационный вход которого подключен к входу логических условийустройства, выход второго мультиплексора соединен с информационнымвходом второго старшего разряца первой группы первого коммутатора адреса, информационный вход остальныхстарших разрядов первой группы которого соединен с выходом второгокоммутатора адреса, второй информационный вход которого соединен свыходом буферного регистра, вход синхронизации которого соединен с выходом четвертого элемента И, первыйвход которого соединен с инверснымвходам пятого элемента И, с управляющим входом второго коммутато 1Изобретение относится к автоматике и вычислительной технике и может бьггь использовано при построении центральных и периферийньгх устройств управления ЭВМ и вычислительных систем.Цель изобретения - снижение объема оборудования за счет уменьшения объема памяти микрокоманд.На фиг. 1 приведена функциональ- ная схема предлагаемого микропрограммного устройства управления; на фиг, 2 - функциональная схема гервого (второго) мультиплексора; на Фиг, 3 - фрагмент реализуемой 15 микропрограммы, где показано размещение информации в полях микрокоманд, предшествующих ветвлению,и поля микрокоманд ветвления (А - поле адреса, .А с - старшие разряды адре са, Х 1, Х 2, ХЗ, Х 4 - проверяемые логические условия).Микропрограммное ус-ройство управления (Фиг. 1) содержит блок 1 памяти микрокоманд, в том числе 11-1 соответственно выходы признака предшествующей ветвлению микрокора адреса и с нулевым выходом триггера условий, единичный выход которого соединен с прямым входомтретьего элемента И, выход которогосоединен со стробирующими входамипервого и второго мультиплексоров,вторые информационные входы которых соединены соответственно с выходами первого и второго модифицируемых разрядов кода адреса блокапамяти микрокоманд, вход синхронизации триггера условий соединен с3- и К-входами триггера условий,с выходом первого элемента И, свторым входом четвертого элемента Ии с прямым входом пятого элемента И,выход которого соединен с входомустановки в ноль буферного регистра, выход элемента ИЛИ являетсявыходом индикации ошибки устройства,второй выход генератора тактовыхимпульсов соединен с входом синхронизации регистра адреса. 2манды, кода микроопераций, первогои второго модифицируемых разрядовкода адреса, старших разрядов кодаадреса, младших разрядов кода адреса и кода логических условий микрокоманд, регистр 2 адреса, буферныйрегистр 3, регистр 4 микрокоманд,триггер 5. условия, первый коммутатор 6 адреса, второй коммутатор 7адреса, первый 8 и второй 9 мультиплексоры, триггер 10 пуска, генератор 11 тактовых импульсов, первый 12, второй 13, третий 14, четвертый 15, пятый 16 элементы И,элемент ИЛИ 17, входы 18 - 20 соответственно кода команды, пуска, логических условий, управляющий выход21, выход признака конца работы 21и выход признака конца команды21 регистра микрокоманд выход 22индикации ошибки, выходы 23 - 25соответственно старших разрядовацреса, младших разрядов адресакода логических условий блока памятимикрокоманд, первый 26 и второй27 выходы генератора тактовых импульсов,1183964 4торые по разрешающему сигналу с нулевого выхода триггера 5 через коммутатор 7 совместно с младшими разрядами адреса с выхода 24 и модиФицируемых разрядов с выходов мультиплексоров 8 и 9 (фиг. 2) поступаютна вход первого коммутатора 6 и последующему первому тактовому импульсу считываются в регистр 2 адре 10 са. В этом случае адрес микрокоманды формируется аналогично линейному участку микропрограммы"А = А + А +Ы 1+ 02 По сигналу "Пуск" с входа 19 устройства триггер 10 устанавливается в ециничное состояние и включает генератор 11,По первому тактовому импульсу с выхода 26 генератора 11 в регистр25 2 адреса с входа 18 через коммутатор 6 записывается код реализуемой команды, который определяет адрес первой микрокоманды соответствующей микропрограммы. С выходовЗО 24 и 23 блока памяти через коммутатор 7 считываются младшие и старшие разряды адреса следующей микро- команды соответственно.По второму тактовому импульсу 35 с выхода 26 генератора 11 код микро- команды записывается в регистр 4 микрокоманд и выдается на выход 21 устройства.По очередному тактовому импуль су работа устройства повторяется.Рассмотрим Функционирование устройства в случае реализации ряда условных переходов в микропрограмме. При этом за такт до микрокоманды вет 45 ветвления на выходе 1 формируется единичный сигнал. По тактовому импулэ. су с выхода 27 генератора 11 код микрокоманды записывается в регистр 4 микрокоманд и выдается с выходов регистра 4 на выход 21 устройства.По разрешающему значению сигнала с выхода 1 тактовым импульсом триггер 5 переводится в единичное состояние, а сформированный на выходе эле мента И 15 импульс обеспечиваетсчитывание в буферный регистр 3 старших разрядов адреса микрокоманды, ко 3Мультиплексор 8 (9) содержит(фиг. 2) выход 28 (29), дешифратор30 и коммутатор 31.Предлагаемое микропрограммноеустройство управления с контролемфункционирует следующим образом,Цепи приведения в исходное состояние на схеме условно не показаны.В исходном состоянии все элементы памяти устройства (Фиг, 1) находятся в чулевом состоянии, за исключением единичного состояния разряда регистра 4 микрокоманд, соответствующего выходу 21 регистра 4микрокоманд. Последний разрешаетпередачу через первый коммутатор 6кода команды с.входа 18 устройства для его. последующей записи в регистр 2 адреса,стгде Л - старшие разряды адреса избуферного регистра 3;млА - младшие разряды адреса.с 1, с 2 - модифицируемые разрядыадреса.В формате микрокоманды ветвления единичный сигнал на выходе 1 отсутствует. Так как триггер 5 находится в единичном состоянии, то на выходе элемента И 14 формируется сигнал, разрешающий работу мультиплексоров 8 и 9, на вход 20 которых поступает значение логических условий, а с выхода 23 и 25 поступают записанные в формате старших разрядов адреса и поля логических условий коды логических условий. Промо"юМ дифицированные разряды Ыи 2 поступают на вход коммутатора 6.В этом случае адреса очередных микрокоманд формируются какгГЪ лгдеи Ю 2 могут принимать значения(0,0); (0,1); (1, 1) , (1,0) .1Таким образом осуществляется двунаправленное ветвление, При необЯмл ходимости реализации до 2 условных переходов схема функционирует аналогично, причем, благодаря тому, что А - сопят,все микрокоманды, сформированные в этом случае, находятся в пределах одной страницы блока памяти, При необходимости перехода вновь к реализации линейного участка микропрограммы в Формате первой микрокоманды из линейной последовательности задается единичный сигнал на выходе 1, который обеспечивает по второму тактовому импульсу возвращение триггера 5 в исходное нулевое состояние и обнуление регистра 3 путем подачи наего К-вход сигнала, сформированногл на выходе элемента И 16. Послечего устройство функционирует согласно алгоритма, описанного выше, В предлагаемом устройстве предусмотренконтроль его функционирования.Сигнал "Ошибка" формируется на выходе 22 устройства в случае одновременного появления в формате микро" щкоманды управляющей метки и информации в поле логических условий.По окончании работы устройства в последней микрокоманде записывается единица в разряде, соответствующем выходу 21 а регистра 4 микрокоманд. Этот сигнал поступает на К-вход триггера 10, который возвратится в исходное состояние и остановит генератор 11 тактовыхимпульсов.одписно 13035,/5 Патент жгород, ул. Проектная, 4 илиал Тираж 709Государственного келам изобретений иМосква. Ж, Раушс митета СС ткрытийая наб;,

СмотретьЗаявка

3734408, 25.04.1984

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, МАЛАХОВ ВИКТОР АЛЕКСАНДРОВИЧ, ВОРОБЬЕВ КОНСТАНТИН ЮРЬЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 07.10.1985

Код ссылки

<a href="https://patents.su/5-1183964-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство для вычисления полярных координат

Следующий патент: Устройство для распределения заданий процессорам

Случайный патент: Упругая муфта12