Устройство для определения максимального из -двоичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1173408

Автор: Мурашко

Текст

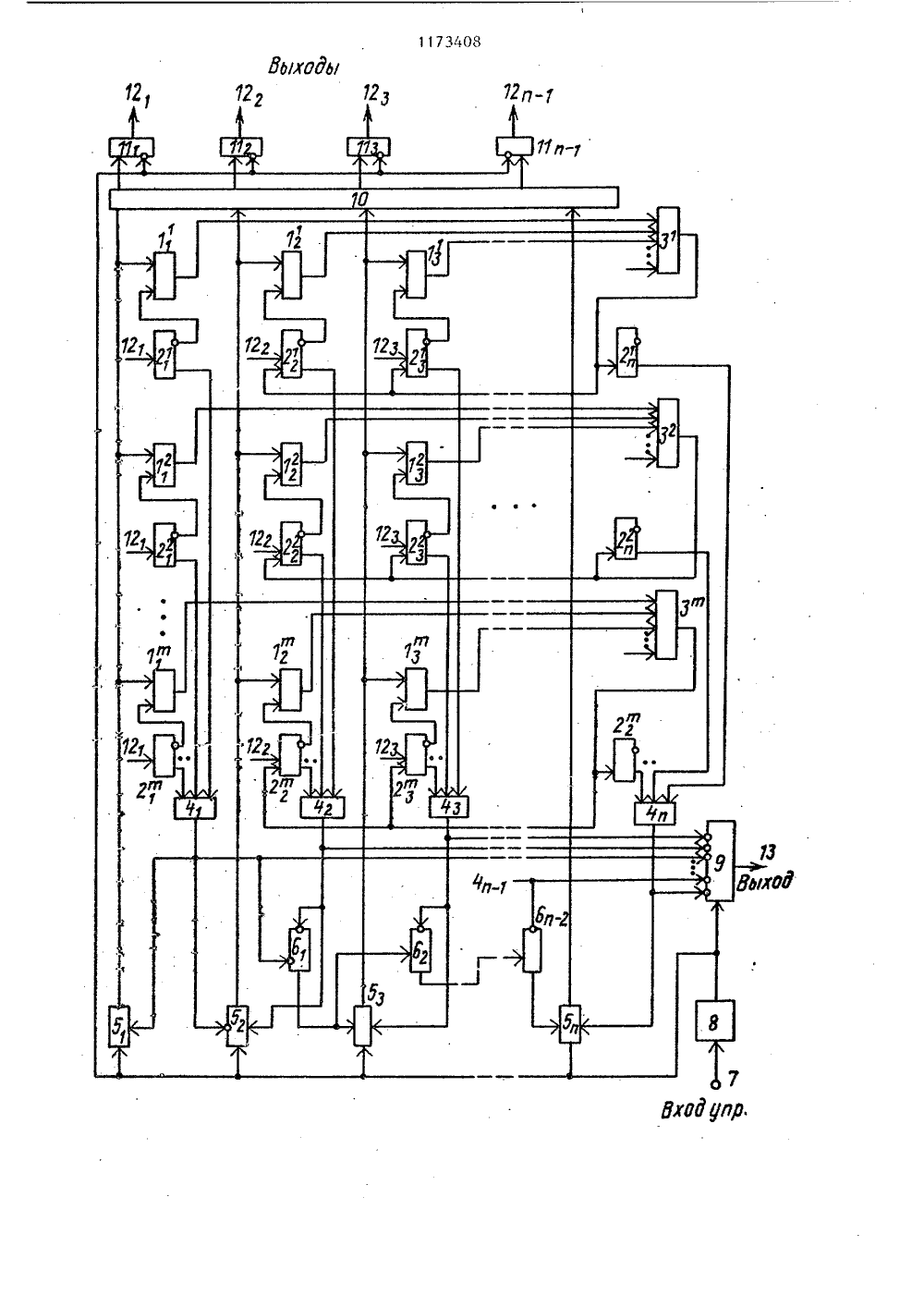

)4 С 06 Р 7/О ГОСУДАРСТВЕННЫЙ НОМИ О ДЕЛАМ ИЗОБРЕТЕНИЙ Т СССРОТНРЫТИЙ ПИСАНИЕ ИЗОБРЕТЕ Й., т ЗВдй ,ЬСТВ о СССР1973.СССР1980,К АВТОРСКОМУ СВИ(56) Авторское свидетельстУ 514291, кл. С 06 Р 7/02,Авторское свидетельствоР 875376, кл. С 06 Р 7/04,(54)(57) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯИАКСИИАЛЬНОГО ИЗ Г ДВОИЧНЫХ ЧИСЕЛ,содержащее е групп элементов И пооэлементов И в каждой группе,где и - число разрядов сравниваемыхчисел, .ь групп элементов памяти пои элементов памяти в каждой группе,и многовходовых элементов ИЛИ анализа разрядов, в элементов ИПИ обнуления, управляющие элементы И, регистр результата, причем прямойвыход каждого 1-го элемента памяти1-й группы, где 1 = 1,2п,1== 1,2, в соединен с 1 -м входом 1-го элемента ИЛИ анализа разряда, выход которого подключен кпервому входу 1-го управляющего элемента И, выход которого соединен совходом установки в единичное состояние 1-го разряда регистра резуль.тата, выход 1-го управляющего элемента И, где 1= 1,2 пподключен к первым входам 1-х элементов И всех групп, второй вход 1-гоэлемента И %-й группы подключен кинверсному выходу 1-го элементапамяти %-й группы, выход (и)-гоэлемента И 1-й группы соединен спервым входом Ь-го элемента ИЛИ обнуления, выход которого подключен к входу установки в нулевое состояние о-го элемента памяти 1-й группы, о т л и ч а ю щ е е с я тем,что, с целью повышения быстродействия, в устройство введены и -1элементов И обнуления, о -2 элементов И анализа разрядов, многовходовый элемент И и генератор импульсов, вход запуска которого подключен к входу запуска устройства, авыход соединен с вторыми входамивсех управляющих элементов И, управ яющим входом многовходового эл мента И и инверсными входами всех элементов И обнуления, прямой вход -го элемента И обнуления подключен, к выходу -го разряда регистра ре 1эультата, а выход соединен с первыми входами установки в нулевое состояние )-х элементов памяти всех групп, вторые входы установки в нулевое состояние элементов памя-ти со второго по (и)-й 1-й группы объединены и подключены к входу установки в нулевое состояние и-го элемента памяти В-й группы, выход р-го элемента И Ъ-й группы, где р =1,2о, соединен с (р+1)-м входом %-го элемента ИЛИ обнуления, выходы многовходовых элементов ИЛИ анализа разрядов подключены к инверсным входам многовходового элемента И, выход которого является выходом окончания поиска устройства, выход первого многовходового элемента ИЛИ анализа разрядов подключен к инверсному входу второго управляю- . щего элемента И, первый инверсный вход р-го элемента И анализа разрядов подключен к выходу (р+1)-го мно1173408 говходового элемента ИЛИ анализаразрядов, второй инверсный вход первого элемента И анализа разрядовподключен к выходу первого многовходового элемента ИЛИ анализа разря 1Изобретение относится к автоматике и вычислИтельной технике и можетбыть использовано в различных устройствах обработки цифровой информации, устройствах распознавания образцов, устройствах обработки спектров сложных сигналов,Целью изобретения является повышение быстродействия устройства.На чертеже представлена блок-схема предлагаемого устройства.Устройство содержит п групп эле 1 2 2ментов И 1, 11 ь 1 ю 12 П 3 ГН Ф1 , 1,1,.1 и,т - группо г15элементов памяти 2,2 2,2к и В2,22 ,2 ,.2 и, в эле 1ментов ИЛИ 3",3 ,.,3 обнуления, п- многовходовых элементов ИЛИанализа разрядов 44 4, управляющие элементы И 5,5 5 (и -2) 20элементов И анализа разрядов 6,66 , вход 7 запуска устройства, генератор 8 импульсов, многовходовый элемент И 9, регистр 10результата, (и) элементов И обнуления 11, 11 ,11 и ,(н) выходы 12, 12 12 , элементов И11 являются вторыми установкамив нулевое, состояние -ой группы элементов 2", памяти, 13 - выход окон- Зочания пойска устройства.Назначение элементов устройстваследующее. Элементы 2 памяти, где= 1,2в, = 1,2,и,юколичество анализируемых двоичныхчисел, и- количество двоичных разрядов в числе, служат для временногохранения двоичных чисел. 1 -ая груп,па элементов И 1 и В-ый элемент ИЛИ3 служат для выработки сигнала об Онуления Х-ой группы элементов 2памяти. Если при стробировании сигналом с выхода элемента И 5 первогоэлемента И 1, в соответствующем -ойгруппе разряды двоичного числа, храдов, выход р-го элемента И анализа разрядов соединен с третьим входом (+2)-го управляющего элемента И и вторым входом (р+1)-го элемента И анализа разрядов. 2нимого в соответствующей ячейке памяти, имеют нулевое значение, то всеэлементы памяти, хранящих 1-ое число,обнуляются. Элементы ИЛИ 4 формируютсигналы разрешения, например "1",если хотя бы в одном из чисел анали, 1зируемого разряда в элементах 2памяти присутствует "1".Элементы И 5;, где 1= 1,2и,и элементы И бр, где р = 1,2,у(и) служат для последовательногоанализа разрядов всех чисел и соответствующего стробирования тех разрядов, которые содержат хотя бы водном из чисел "1" в соответствуюцем разряде.Элемент И 9 служит для выработкисигнала окончания операции поискамаксимального числа на выходе 13устройства, причем сигнал на выходеэлемента И 9 появляется лишь приобнуленных состояниях всех элементов 2 йамяти, т.е. когда отсутству"ют сигналы разрешения с выходов элементов ИЛИ 4Элементы И 11 , где = 1,2,(и) служат для выработки сигналаобнуления соответствующего разряда,окончанию такта перезаписи 1 состояния в регистр 10 результата. Регистр 10 результата служат для формирования двоичного и-разрядного кода максимального из щ двоичных чисел.Генератор 8 импульсов служит для выработки тактов синхронизации, обес печивающих последовательное формирование стробирующих импульсов при анализе разрядов чисел, начиная со старших разрядов. Запуск генератора 8 происходит по сигналу, поступающему на вход 7 запуска устройства.Устройство работает следующим образом.Перед началом работы в элементы 2 . памяти заносятся п двоичных1 с1чисел, причем в первую группу элементов 21 памяти заносят все стар 1шие разряды н двоичных чисел,далее в последующие группы заносятся все разряды чисел в порядке убывания старшинства разрядов, а в группе элементов 2 памяти заносятся все младшие разряды п двоичных чи-, сел. Регистр 10 результата обнуляется.В устройство по входу 7 поступает сигнал начала операции, по которому осуществляется запуск генератора 8 импульсов. Генератор 8 импульсов вырабатывает серию импульсов стробирования для элементов И 5, элемента И 9, элементов И 11 , причем сигналом разрешения для элементов И 5,. и элемента И 9 является сам тактовый импульс, а для элементов И 11 - отсутствие тактового импульса на их первых входах.В случае 1, если хотя бы в одном из элементов 2 памяти 1-ойгруппы, где %= 1,2.,в, в старшем разряде записана "1", то сигнал через элемент ИЛИ 4 поступает на второй вход элемента И 5 , разрешая прохождение строб-импульса с генератора 8 импульсов, При этом сигнал поступает в регистр 10 результата и записывает в него "1" в этом разряде, а также этот сигнал поступает на вторые входы элементов И 1 данного разряда. Если в 1-ом числе, 1 с = 1,2.гп этот разряд установлен в "0" состояние то с инверсного выхода элемента 2 памяти снимается разрешающий потенциал, открывающий элементы И 1 и через элемент ИЛИ 3 поступает сигнал установки в нулевое состояние по первымФвходам элементов 2 памяти, в которых и хранится 1-ое число. Данное число исключается из процесса поиска максимального из в двоичных чисел. По окончанию первого импульса . генератора 8 импульсов на первом входе элемента И 11 появится сигнал разрешения, а поскольку по первому такту в старшем разряде регистра 10 уже записана "1", то срабатывает ,элемент И 11 и на его выходе 12 появляется сйгнал установки в нулевое состояние всех старших разрядовэлементов 2 памяти, т.е, проаналиЪзированные разряды элементов 2, памяти обнуляются.В случае 2, когда исследуемыечисла имеют нулевые значения в старшем разряде ( =1), то с выхода элемента ИЛИ 4 на второй вход эле 111 Нмента И 5 поступает сигнал "Запрет, 10 а на третий вход элемента И 5 этотсигнал уже разрешающий (по входуон инвертируется). При этом, еслихотя бы в одном из чисел в следующемразряде (1=2) имеется "1", то сра батывает элемент ИЛИ 4 г, разрешаятем самым прохождение первого стробимпульса с генератора 8 через второйэлемент И 5 . Срабатывает элемент И 5 и сигнал с его выходаг20 . поступает в регистр 10 результата изаписывает "1" в этом разряде, аЭтакже на вторые входы элементов И 121где 1 с= 1,2 в. Если в %-омчисле данный разряд равен нулю то 25 с инверсного выхода элемента 2 па 2мяти данного разряда снимается разрешающий потенциал, открывающийэлемент И 1 и через элемент ИПИ 32поступает сигнал установки в нулевое ЗО состояние по первым входам элемен- .тов 2 г памяти, в которых и хранится-ое число. Таким образом, уже первым строб-импульсом производитсяперезапись единичного значения последующего разряда в регистр 10 результата при наличии во всех самых старших разрядах (1=1) чисел нулевых значений. Обнуляются те элементы памяти тех чисел, которые не имели вданном стробируемом разряде "1"-ыхзначений как и в предыдущем случае.По окончании строб-импульса происходит обнуление элементов памятипростробированного разряда всех 45 чиселБ случае 3, когда и в старшеми .в последующих разрядах (1 =1, =2)во всех исследуемых числах тольконулевые значения, то с выхода эле-ментов ИЛИ 4 1 и 4 г поступает запрет на вторые входы соответствующих элементов И 5 и 5 . Эти самые2сигналы с выходов элементов ИЛИ 4и 4 г, например нулевого потенциала,уже вызывают срабатывание элемента Л 1 И 6 за счет инверсии сигналов,поступающих на его входы. Разрешающни потенциал с выхода элемен 1173408та ИЛИ б разрешает срабатывание по третьему входу элемента И 5 и по второму входу элемента И б . Далее, если хотя бы в одном из чисел следующий разряд (1=3) имеет значение "1", то срабатывает элемент ИЛИ 4 и на второй вход .элемента И 5 постуз пает сигнал разрешения. Первым строб-импульсом происходит переза- О пись "1" в соответствующий разряд регистра 10 результата, а также обнуляются все элементы памяти тех чисел, которые имели в этом (1=3) разряде нулевое значение как и в 15 предыдущих случаях. По окончанию строб-импульса с выхода 12 элемен 3 та И 11 з сигнал обнуляет, все элементы 2 ф памяти (=3). Аналогично3производится анализ и стробирование 20 последующих разрядов.Далее производится анализ и стробирование последующих 1-разрядов О чисел, запись "1" в соответствующие разряды регистра 10 результата, если 25 хотя бы у одного анализируемого -разряда исследуемых 1 чисел была "1". Если в В-ом числе данный -тый разряд имеет нулевое значение, то с инверсного выхода элемента 2" па3 мяти данного разряда поступает разрешение последовательно в соответствующем такте через элемент И 5 , первый элемент И 1 элемент ИЛИа3 " для установки в нулевое состоя- з 5% ние по первым входам элементов 2 памяти, в которых хранилось %-ое число По окончанию стробимпульса происходит обнуление элементов памяти 2" простробированного )-раэря да всех в чисел.Таким образом, осуществляется анализ значащих (ненулевых) разрядов чисел и перенос такта стробировання на первый значащий разряд,тем самым сокращается время формирования результата в регистре 10, Кроме того, в каждом такте еще выбывают из анализа все числа, имеющие в стробируемых разрядах нулевые значения, и обнуляются все проанализированные значащие разряды, Причем в каждом такте импульсов с генератора 8.импульсов производится опроссостояний всех разрядов всех чисел на "0". Если в хдде опроса элемента И 9 по его стробирующему входу поступит импульс в момент, когда выбыли из анализа все числа, а максимальное число имеет в оставшихсяразрядах нулевое значение, то на выходе элемента И 9 формируется сигнал об окончании операции. Это позволяет досрочно определить максимальное число, при этом число И тактовых импульсов меньше количества ь разрядов исследуемых чисел.В результате поиска по сигналу с выхода 13 устройства в регистре 10 сформированный двоичный код максимального из щ двоичных чисел может быть записан во внешнее устройство. Введение адаптивной к составу информации синхронизации.при опресе. разрядов чисел с учетом анализа значащих (имеющих единичное значение) разрядов чисел, обнуление соответствующих элементов памяти проанализированных разрядов всех чисел, анализ нулевых состояний элементов памяти позволяет повысить реальное .быстродействие устройства, уменьшить время поиска экстремального числа из.щ двоичных чисел.

СмотретьЗаявка

3697916, 02.12.1983

ПРЕДПРИЯТИЕ ПЯ А-3327

МУРАШКО АЛЕКСАНДР НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 7/04

Метки: двоичных, максимального, чисел

Опубликовано: 15.08.1985

Код ссылки

<a href="https://patents.su/5-1173408-ustrojjstvo-dlya-opredeleniya-maksimalnogo-iz-dvoichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для определения максимального из -двоичных чисел</a>

Предыдущий патент: Устройство для выбора экстремального числа

Следующий патент: Сумматор-умножитель

Случайный патент: Стыковое соединение железобетонных секций сваи