Устройство для вычисления элементарных функций по алгоритму волдера

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

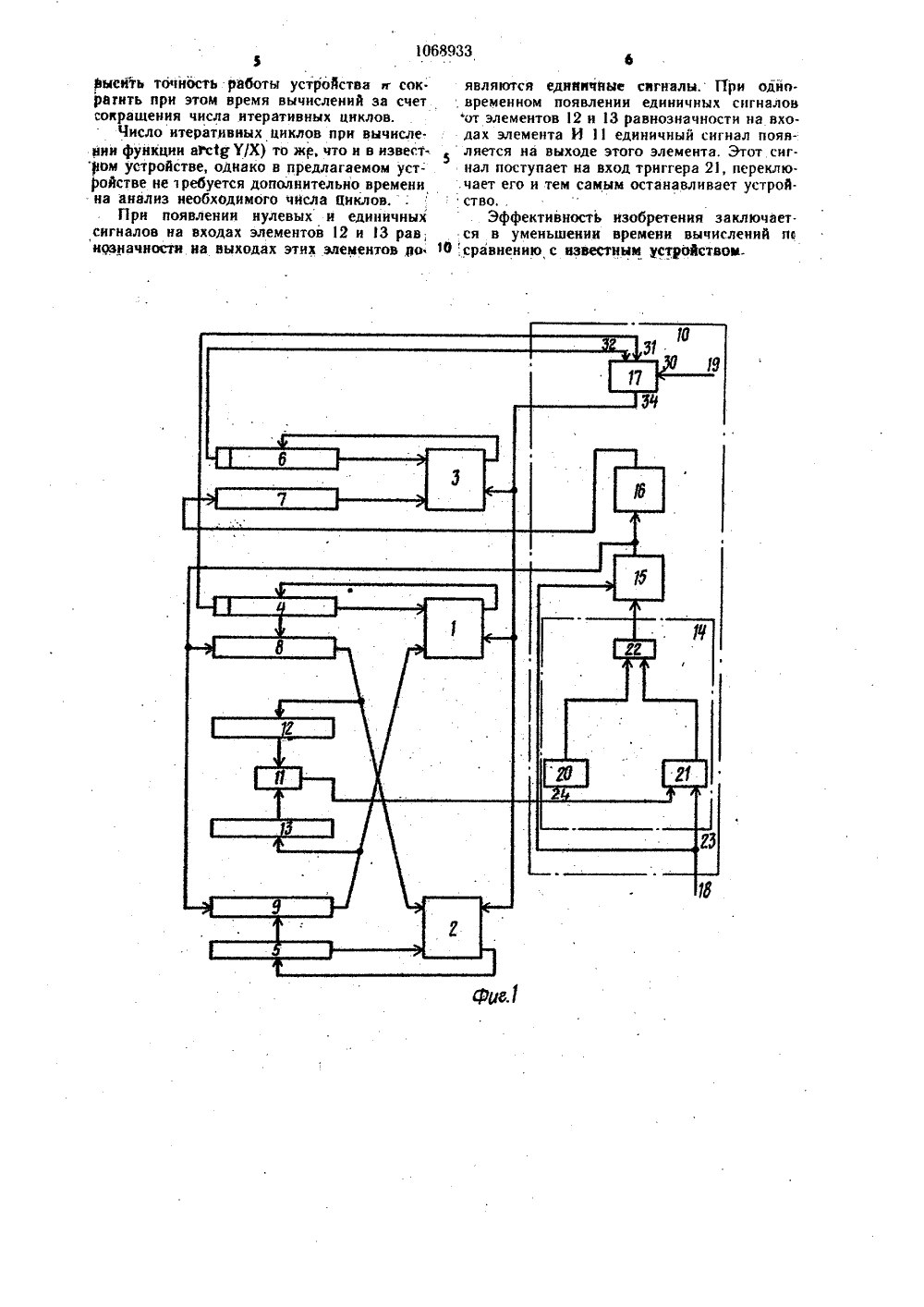

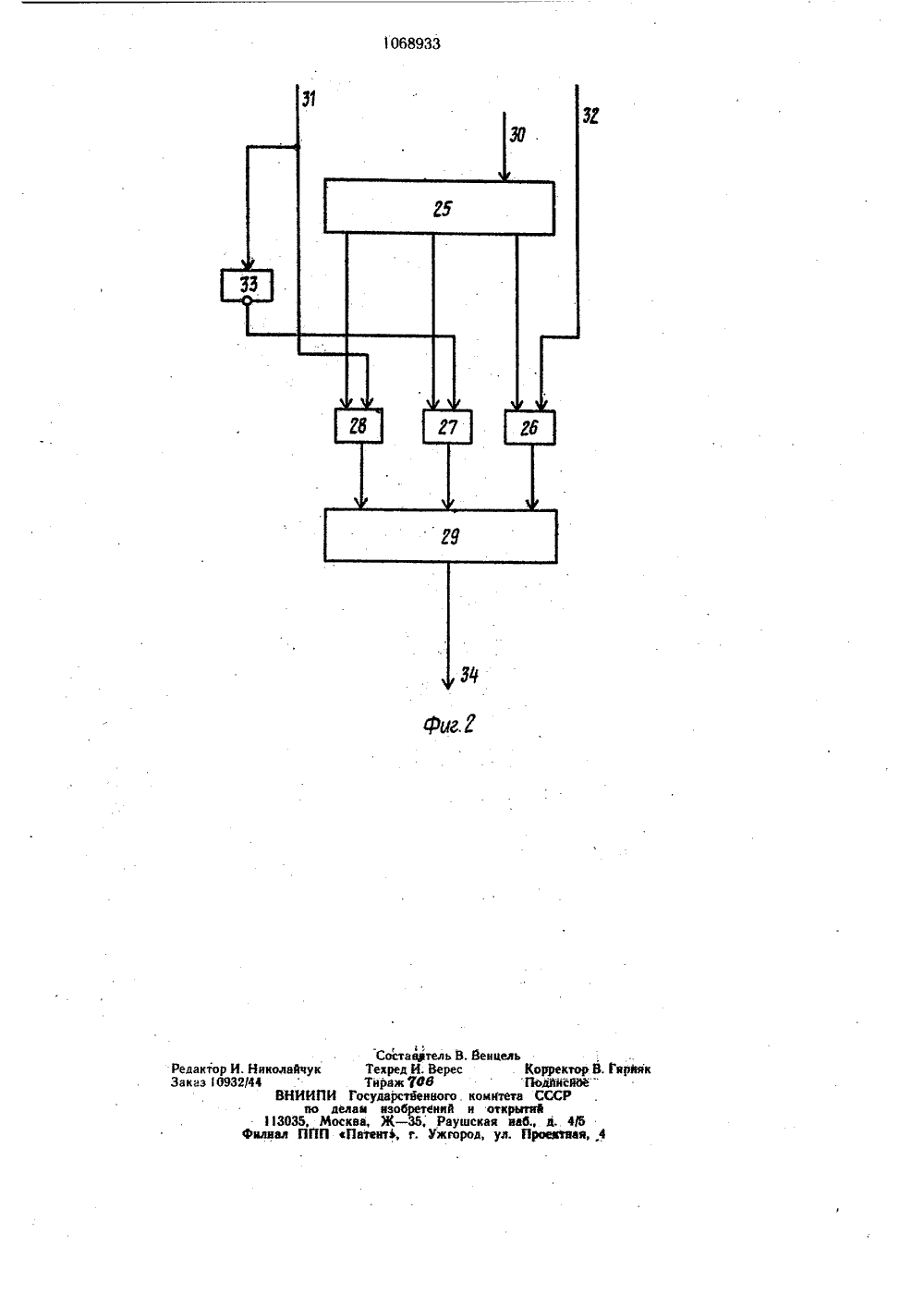

(56) 1. Авторское свидетельство СССР748418, кл. б 06 Г 7/548, 1978,2, Байков В. Д., Смолов В. Б. Аппаратурная реализация элементарных функций, в ЦВМ,Л;, изд-во ЛГУ, 1975, с. 71, рис. 21, (прототип) .(54) (67) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЭЛЕМЕНТАРНЫХ ФУНКЦИИ ПО, АЛГОРИТМУ ВОЛДЕРА, содержащее четыре регистра, три сумматора-вычитателя, два сдвигателя и блок управления, причем выходы первого и второго регистров соединены с первыми информационными входами соответствующих сумматоров-вычитателей ,и информационными входами соответствующих сдвигателей, выходы первого и второго сдвигателей соединены с вторыми информа-, ционными входами второго. и первого сум маторов-вычитателей соответственно, вы", ходы первого и второго сумматоров-вычи дателей соединены с входами соответствую.- щих регистров, входы третьего и четверто. го и четвертого регистров соединены с ин; формационными входами третьего суммато-. ра-вычитателя, выход которого подключен к входу третьего регистра, выходы знаковых разрядов первого и третьего регистров сое-, динены с первым и вторым входами блока,рого соединен с пятым входом блока управ- .,ления, при этом в блоке управления входы запуска и останова управляемого генератора импульсов соеаииеиы с третьим и пятый й входами блока управления, а выход под. ключен к счетному входу счетчика, вход ф обнуления которого подключен к третьему входу блока управления, а выход соединен с первым выходом блока управления и вхо- дом блока постоянной памяти, выход кото- рого является третьим выходом блока упраления и подключен к входу четвертого ре-, гистра, входы узла формирования знака соединены с первым, вторым и четвертью входами блока управления, выход узла фор-, мирования знака является вторым выходом, блока управления. ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙОПИСАНИЕ ИЗО управления, третий и четвертый входь 1 кото рого соединены с входом запуска устроист ва и входом кода операции устройства, пер вый вход блока управления соединен с уп.павляющимн входами первого и второго "двигателей, второй выход блока управле-, кия подключен к управляющим входам первого, второго и третьего сумматоров-вычи., тателей, отличающееся тем, что, с целью сок-, ращения времени вычислений, в него введены два элемента равнозначности и элемент И, а блок управления содержит управляемый генератор импульсов, счетчик, узел фор.мирования знака и блок постоянной памяти,1 причем входы первого и второго элементов равнозначности соединень 1 с выходами соответствующих сдвигателей, а выходы под- ключены к входам элемента И, выход котод1Изобретение относится к вычислительной 1 ехннке и может быть использовано для вычисления значений элементарных функ ций, отображенных с помощью итерационных алгоритмов Волдера.ИзЬестно устройство для вычисления эле. ментарных функций, реализующее алгоритм Волдера и содержащее комбинационные сумматоры-вычислители, регистры памяти и узлы управления 1.Недостатком этого устройства является независимость числа итераций от величин аргументов, что приводит к снижению быстродействия этих устройств,Наиболее близким по технической сущности к предложенному является устройство для вычисления функций агс 1 содержащее регистры, сумматоры-вычитатели, шифратор и блок управления 2.Недостатками устройства являются ог. раниченные функциональные возможности и недостаточ ное быстродействие.Цель изобретения - сокращение времени вычислений.Поставленная цель достигается тем, что в устройство для вычисленияэлементарных функций по алгоритму Волдера, содержащее четыре регистра, три сумматора-вычитателя, два сдвигателя и блок управления, причем выходы первого и второго регистров соединены с. первыми информационными входами соответствующих сумматоров-вычитателей и информационными входами соответствующих сдвигателей, выходы первого и второго сдвигателей соединены с вторыми информационными входами второго и пер. вого сумматоров-вычитателей соответственно, выходы первого и второго сумматороввычитателей соединены с входами соответсгвующих регистров, выходы третьего и четвертого регистров соединены с информационными входами третьего сумматора-вычитателя, выход которого подключен к входу третьего регистра, выходы знаковых разрядов .первого и третьего регистров соединены с первым и вторым входами блока управления, третий и четвертый входы которого соединены с входом запуска устройства и входом кода операции устройства, первый выход ,блока управления соединен с управляющими входами первого и второго сдвигателей, второй выход блока управления подключен к управляющим входам первого, второго и третьего сумматоров-вычитателей, введены два элемента равнозначности и элемент И а блок управления содержит управляемый генератор импульсов, счетчик, узел форми рования знака и блок постоянной памяти, причем входы первого и второго элементов равнозначности соединены с выходами соответствующих сдвигателей, а выходы подключены к входам элемента И, выход кото рого соединен с пятым входом блока управления,.при этом в блоке управления входы запуска и останова управляемого генерато.ра импульсов соединены с третьим и пятыК входами блока управления, а выход под ключен к счетному входу счетчика, вход обнуления которого подключен к третьему входу блока управления, а выход соединей с первым выходом блока управления и входом блока постоянной памяти выход кото. рого является третьим выходом блока управления и подключен к в;оду четвертогО регистра, входы узла формирования знака соединены с первым, вторым и четвертым 5 1 О 40 Сигнал запуска устройства поступает по входу 18, устанавливаеттриггер 21 в состояние 1 и сбрасывает в нулевое состояние счетчик 15. Сигналвыхода триггера 21 поступает на вход элемента И 22, после чего импульсы от генератора 20 импульсов поступают на вход счетчика 15, который вырабатывает в процессе счета коды величины 1 - номеров итераций. входами блока управления, выход узла формирования знака является вторым выходомблока управления.На фиг, 1 представлена структурная схема устройства; на фиг, 2 - структурнаясхема формирователя знака операций.Устройство содержит сумматоры-вычита.тели 1 - 3, регистры 4 - 7, сдвигатели 8 и 9,блок 10 управления, элемент И 11, элементы 12 и 13 равнозначности, управляемыйгенератор 14 импульсов, счетчик 15, блок 16постоянной памяти, узел 17 формированиязнака, вход 18 запуска устройства и вход 19кода операций,Управляемый генератор 14 импульсовсодержит генератор 20 импульсов, триггер 2125 и элемент И 22. Входы 23 и 24 запуска иостанова управляемого генератора 14 являются входами триггера 21.Узел 17 формирования знака содержитдешифратор 25, элементы И 26 - 28, эле.мент ИЛИ 29, вход 30 записи кода операции, входы 31 и 32 для записи знаков операндов У;, Я;, элемент НЕ 33,: выход 34для выдачи значенияУстройство. работает следующим обра- зом.,Вычисляют элементарные функции путеМреализации алгоритма Волдера:.,01+ = Я - .,агс 1 д 2н 1 = 1+ фХ 1 2Х 1+ -- Х - ф;Ъ;. 2 ; (1)где- номер инерации;Ц-П -вырабатывается в зависимостиот вычисляемой функции по известным соотношениям для величин з 1 фЛ;, з 19 пЯ 1," .,оУоЯо -исходные данные для вычисления по алгоритму Волдера;45 ХЯ, Я 1-текущие значения вычисляемых величин,Исходные: данные для вычислений - величины Уо, Хо, Я - записываются в регист,ры 4 - 6.1068933 4 Сумматоры-вычитатели 1 - 3 выполняют операцию сложения или вычитания в зави. симости от кода 1, поступающего на третья входы сумматоров-вычитателей из блока 7 фррмирователя знака операций. На входы 5 блока7 поступают коды знаков величин Я и Ъ. На вход записи кода этой схемы пес тупает код операции, которую необходимо выполнить.Вид операции Код операции япХ, сояХ, ехрХя Ь, с Ь 1 г 00 01-яяп у 1 10 я дп У; На входы элементов 12 и 13 равнознач;.ности поступают сигналы с выходов сдвигателей 8 и 9. На выходе каждого из элементов 12 и 13 равнозначности формируется едй ЗО ничный сигнал при наличии всех нулевых или всех единичных сигналов на входах этого элемента. Наличие всех нулевых сигналов сдвигателей 8 и 9 означает, что все значащие цифры двоичных кодов сигналов, поступающих из регистров 4 и 5 на входы сдви гателей 8 и 9,. остаются левее-входа младШего разряда соответствующего сумматоравычитателя 1 или 2. ИифорМация на выходах сдвигателей 8 и 9 прн последующих итерациях не меняется, так как при сложении кодов, находящихся в регистрах 4 и 5, с ко-. дом 00 или 1 результаты на выходах сумматоров-вычФтателей 1 и 2, поступакь щие в регистры 4 и 5, могут измениться не более чем на единицу младшего разряда по величине, а значит, число значащих цифр 45 результатов изменяется не более чем на единицу, При этом на выходы сдвигателей 8 и 9 поступают на последующей итерации дво ичные коды, сдвинутые на число разрядов на единицу большее, чем на том цикле вычислений, когда уже получены все нулевые или 50 все едйничные коды.Таким образом, при появлении таких сигналов на выходах сдвигателей 8 и 9 дру ля информация на этих выходах при последующих итерациях появиться.уже не может, Следовательно, разрядность двоичных ко. . дов сигналов, используемых для вычислений Ь устройствах для реализации алгоритма 3Величина Х в процессе вычислений со.- держится в регистре 5, У; - регистре 4, Я - в регистре 6.Операции сложения и вычитания производятся ча сумматорах-вычитателях 1 - 3, операции сдвига на 1 разрядов кодов величии Х; н У на итерации, соответствующие умножению на 2 - на сдвигателях 8 и 9.Регистр 7 служит для хранения величин агс 1 д 2 на 1-й итерации, Коды этих величин поступают в регистриз блока 16 постоянной памяти, на вход которого постуиает код номера итерации 1 из счетчика 15. агеева У/Х,Х +Кагс т,7У/Х) На выходе узла 17 формируется сйгнал ф в соответствии с выражением (1) и та 6- лицей. Волдера, позволяет производить вычисле-. ния только конечное меньшее или равно 6 разрядности и двоичных кодов) число ите. ративных циклов, после чего на выходаМ сдвигателей 8 и 9 появляются все нулевые или все единичные сигналы и дальнейшие вычисления не привед; т к уточнению результатов. Более того, добавление к содержимому регистров 4 и 5 двоичного кода 11 изменяет содержимое этих регистров на еди-. ницу на каждом цикле вычислений, что при водит к значительному увеличению погрешности результатов.При вычислении функций агс 1 д УГ). агсй (У/Х), ехр Х результат формируется на регистре 6. Для этих выч ислений необходимы знаки результатов, находящихся в регистре 4.При появлении на выходах сдвигателей 8 и 9. кодов 00 и 11 информация на регистрах 4 и 5 либо перестает изменяться, либо изменяется на единицу в любую с 1 оро ну.Знаки результатов на регистре 4 перестают при этом соответствовать требуемым по алгоритму Волдера.Если устройство, реализующее алгоритм. Волдера, не остановлено в момент появления нулевых и единичных сигналов на выхо дах сдвигателей 8 и 9, ошибка на регист. ре 6 начинает расти,Таким образом, при выполнении любых вычислений по алгоритму Волдера остановка устройства при появлении указанных ну. левых и единичных сигналов позвОляет по 10689335выеить точность работы устройства г сок. являются единичные сигналы. При однорагнть при этом время вычислений за счет временном появлении единичных сигналов сокрашения числа итеративных циклов, от элементов 2 и 13 равнозначности на вхоЧисло итеративных циклов при вычисле- дах элемента И 11 единичный сигнал появнии функции а 1 сФдУХ) то жр, что и в извегт-ляется на выходе этого элемента, Этот сигфом устройстве, однако в предлагаемом уст- нал поступает на вход триггера 21, переклюройстве не 1 ребуется дополнительно времени .чает его и тем самым останавливает устройна анализ необходимого числа цикловство.,При появлении нулевых и единичных Эффективность изобретения заключает. сигналов иа входах элементов 12 и 13 рав; ся в уменьшении времени вычислений п нозначностн.на выходах этих элементов по 16 ,сравнению с известным устройством.лайчНИ Редактор И. Нн Заказ0932(44 орректор В. ГнрйяПодййсйое"СССР 13035,алкал П б., д,. 45Проектная, .4 г 4Составитель В. Венцельк Техред И. ВересТираж 766ПИ Государстйенаого. коннтетано делан изобретений н открытийМосква, Ж - 35, Раушская наПП ПатентФ, г. Ужгород, ул,

СмотретьЗаявка

3418682, 07.04.1982

ПРЕДПРИЯТИЕ ПЯ В-8690

ВАЛЬШОНОК ЕФИМ САМУИЛОВИЧ, ВАВИЛОВ ВЛАДИМИР НИКОЛАЕВИЧ, МИТИН ВЕНИАМИН ДМИТРИЕВИЧ, ПИНЕВСКИЙ НИКОЛАЙ МИХАЙЛОВИЧ, СИГАЛОВ АЛЕКСАНДР СЕМЕНОВИЧ

МПК / Метки

МПК: G06F 7/544

Метки: алгоритму, волдера, вычисления, функций, элементарных

Опубликовано: 23.01.1984

Код ссылки

<a href="https://patents.su/5-1068933-ustrojjstvo-dlya-vychisleniya-ehlementarnykh-funkcijj-po-algoritmu-voldera.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления элементарных функций по алгоритму волдера</a>

Предыдущий патент: Устройство для суммирования одноразрядных двоичных чисел

Следующий патент: Генератор случайных чисел

Случайный патент: Горелка для дуговой сварки неплавящимся электродом в среде защитных газов