Система отладки микропроцессорных устройств

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

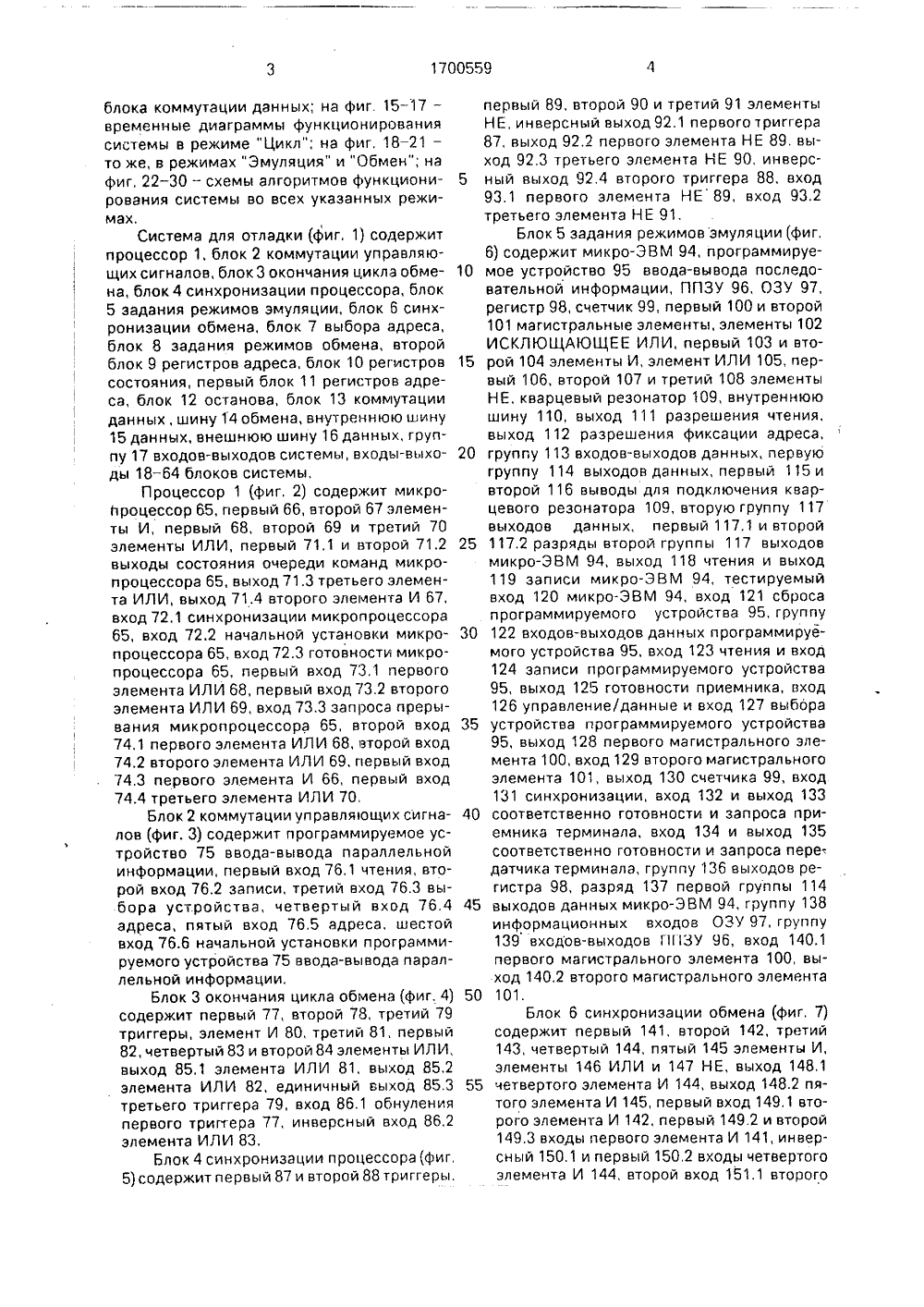

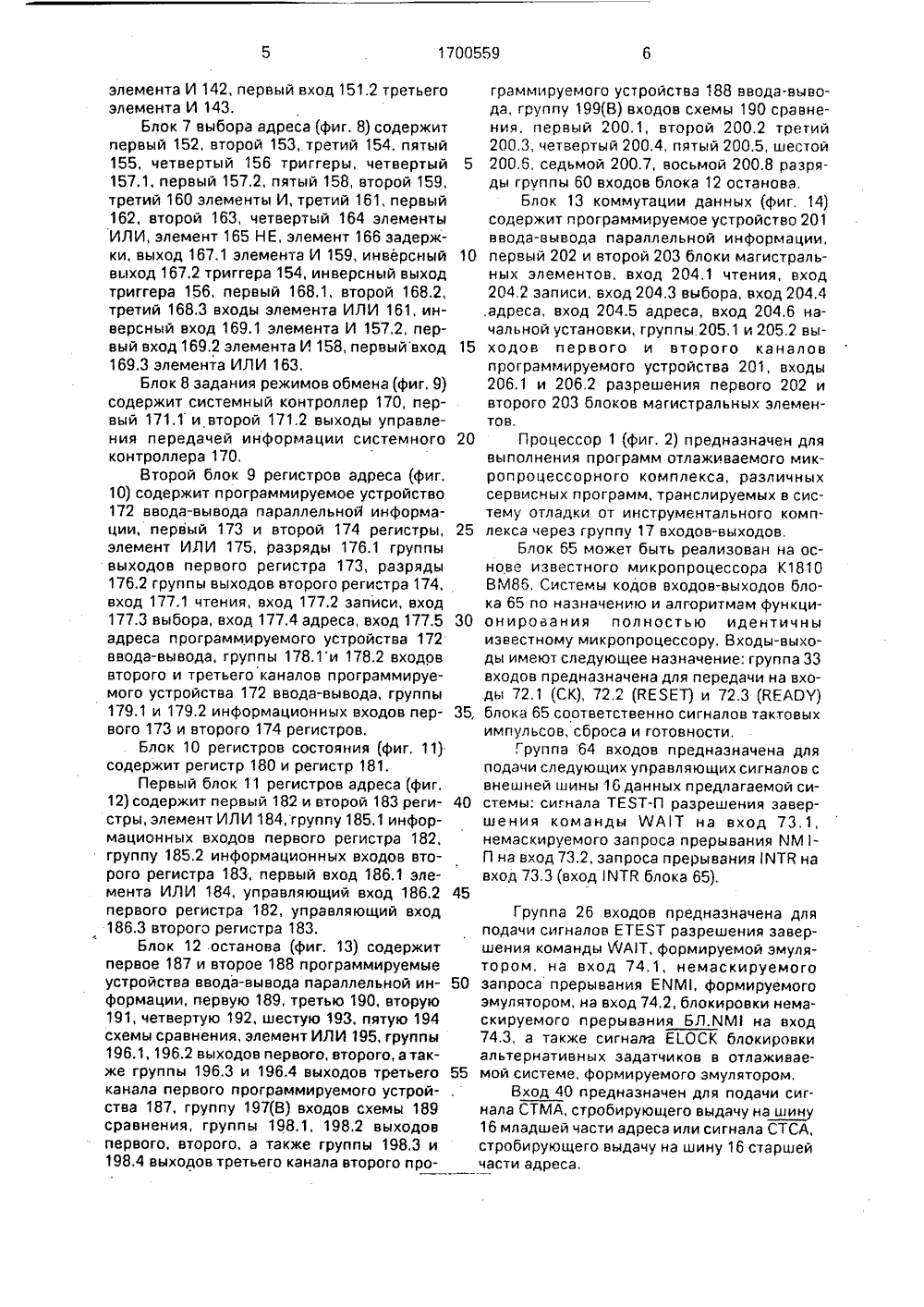

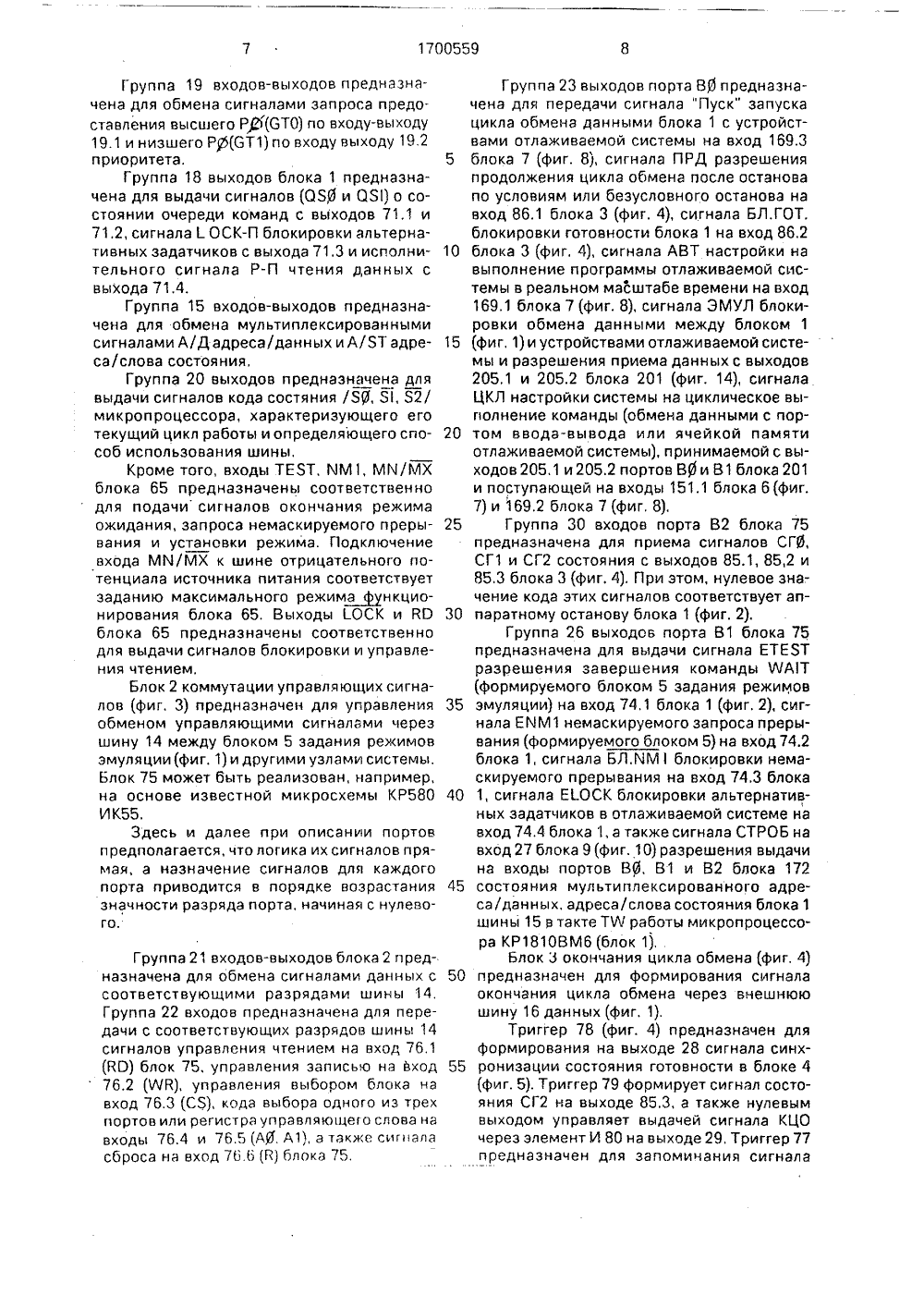

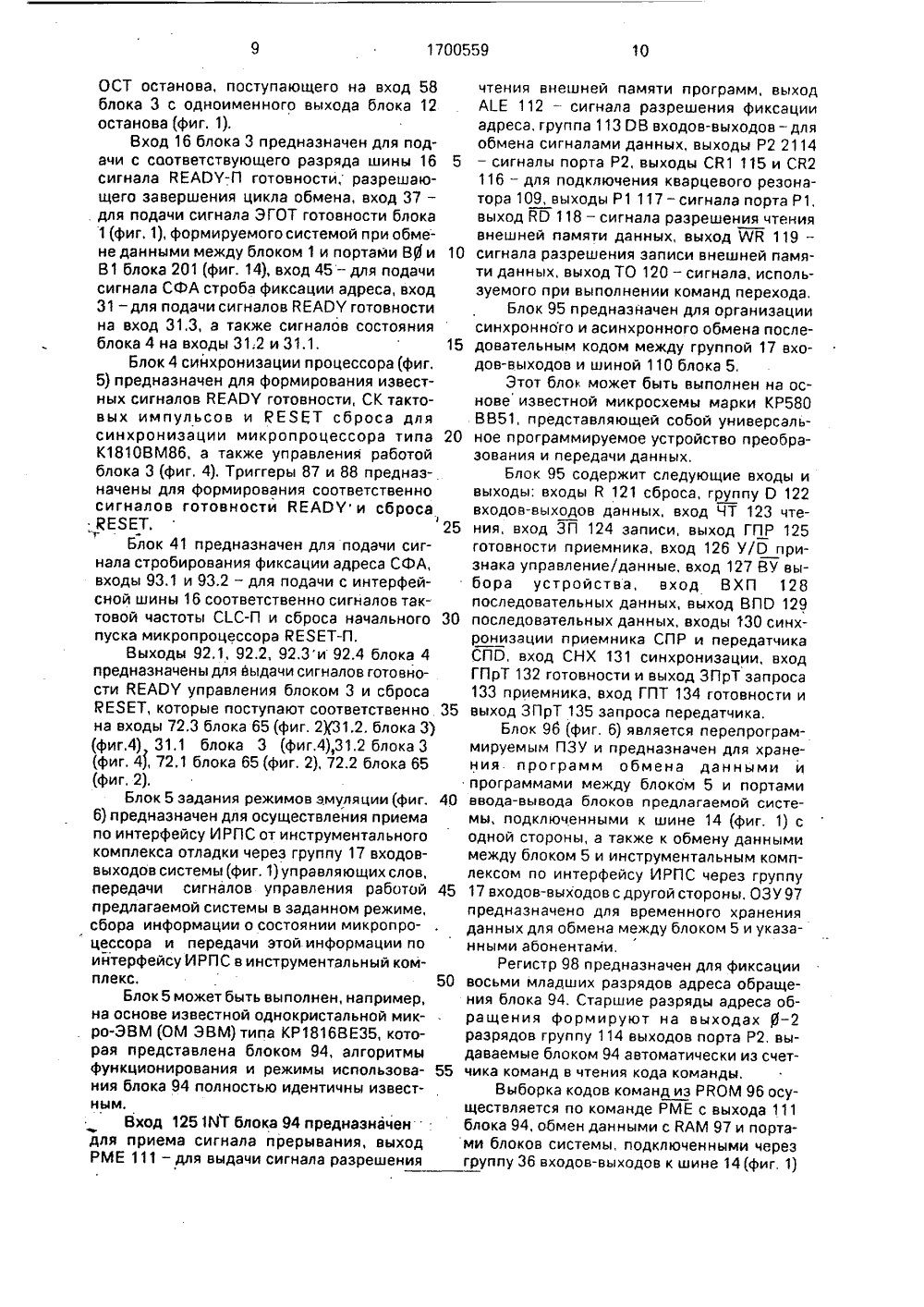

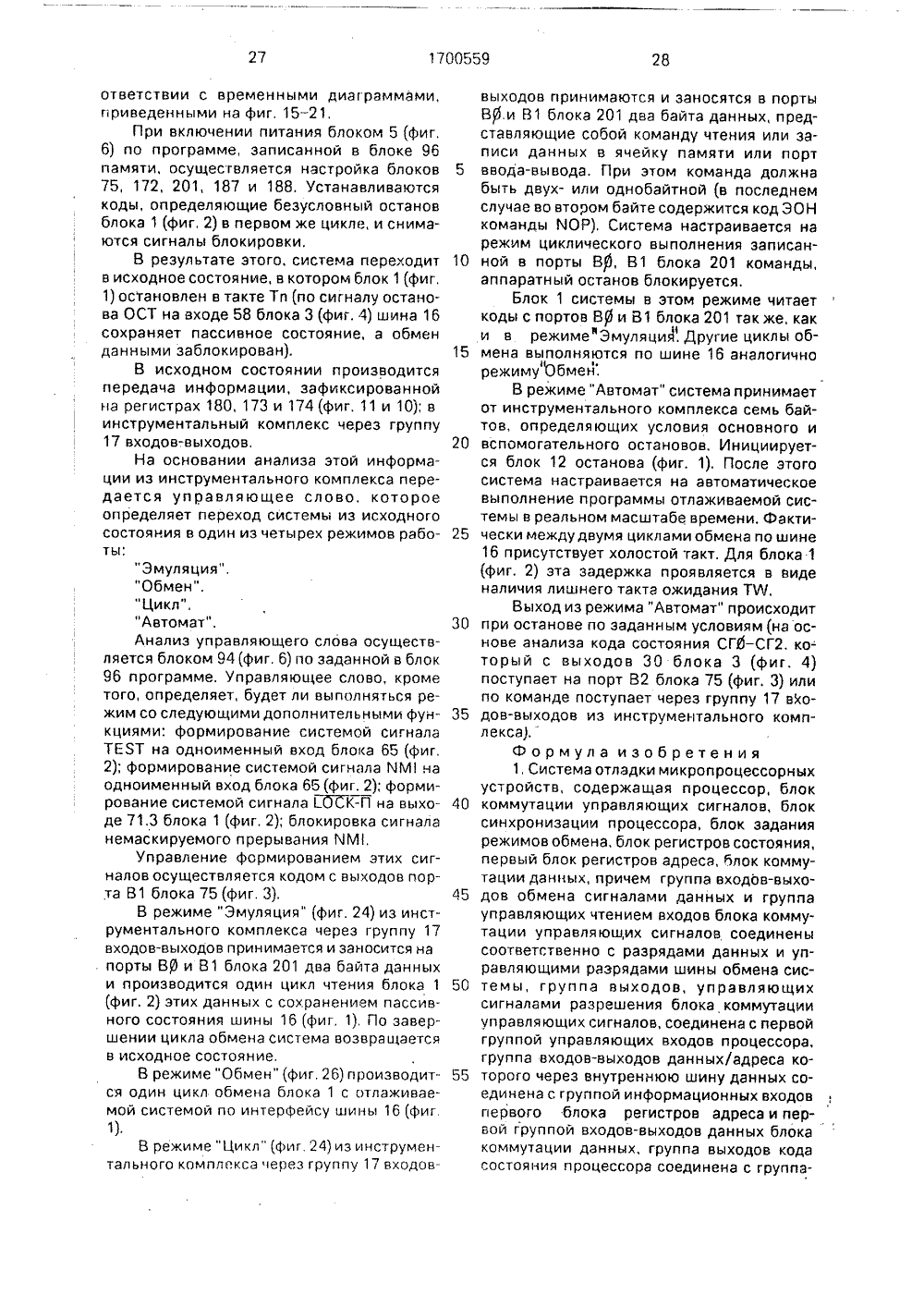

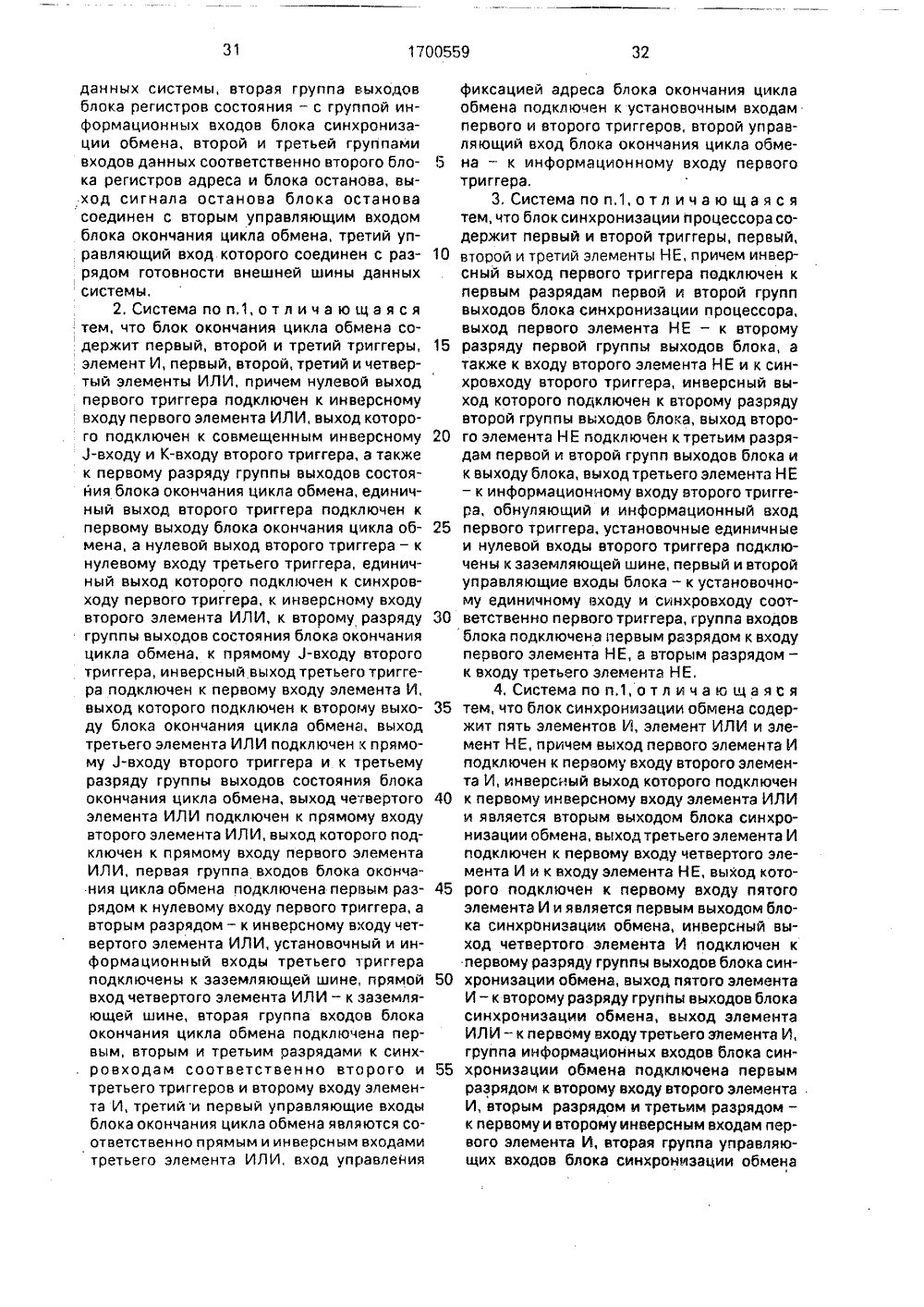

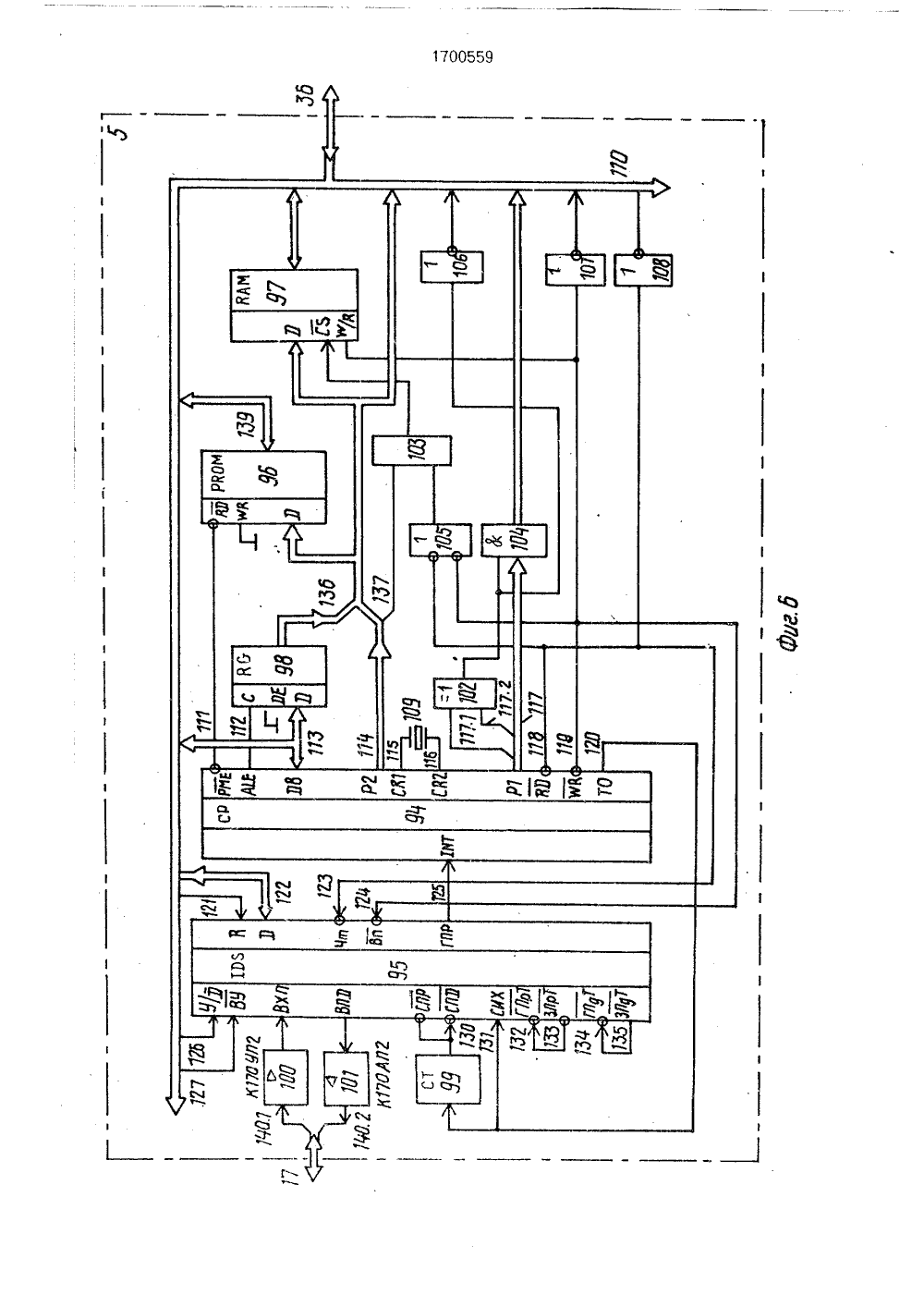

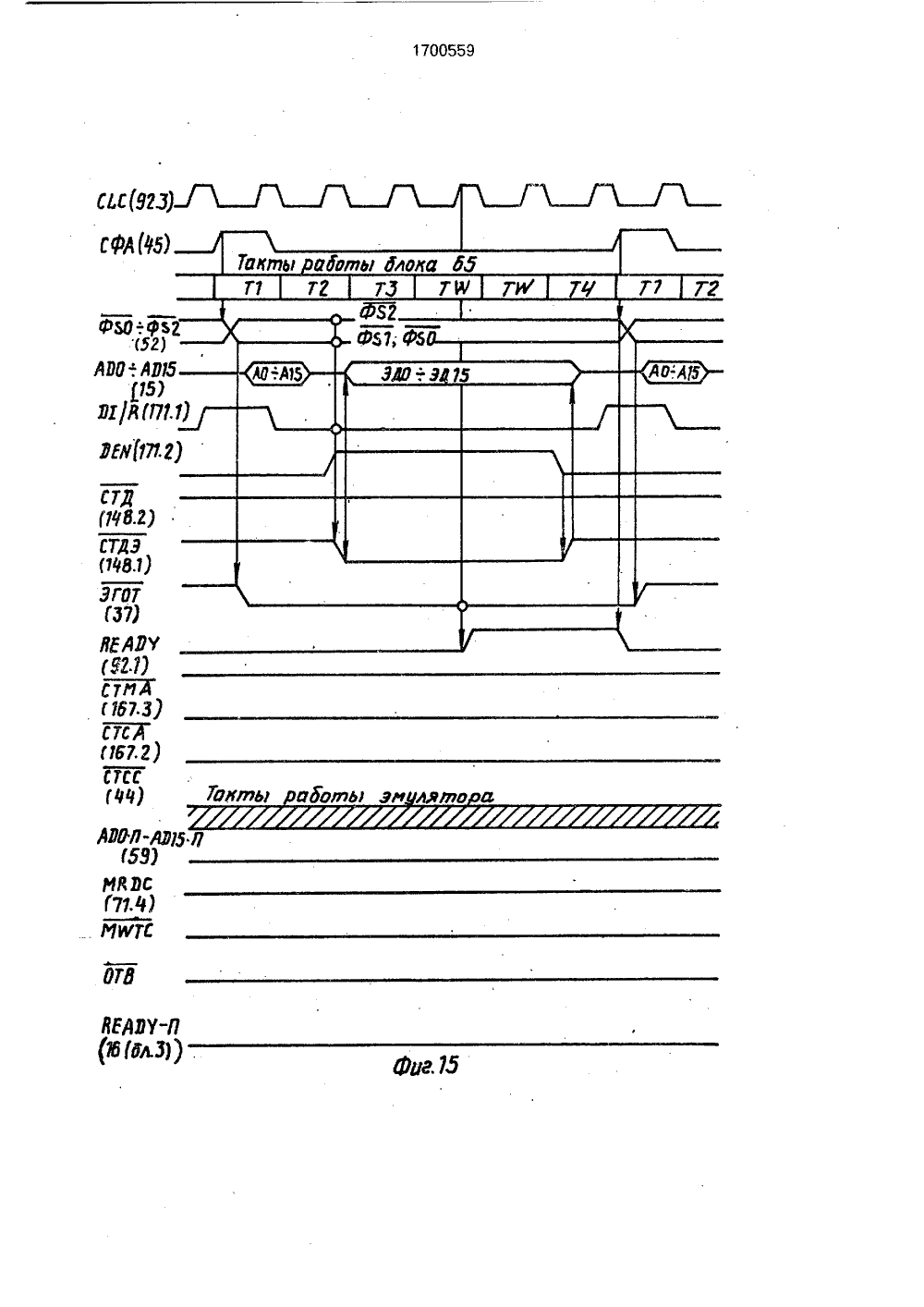

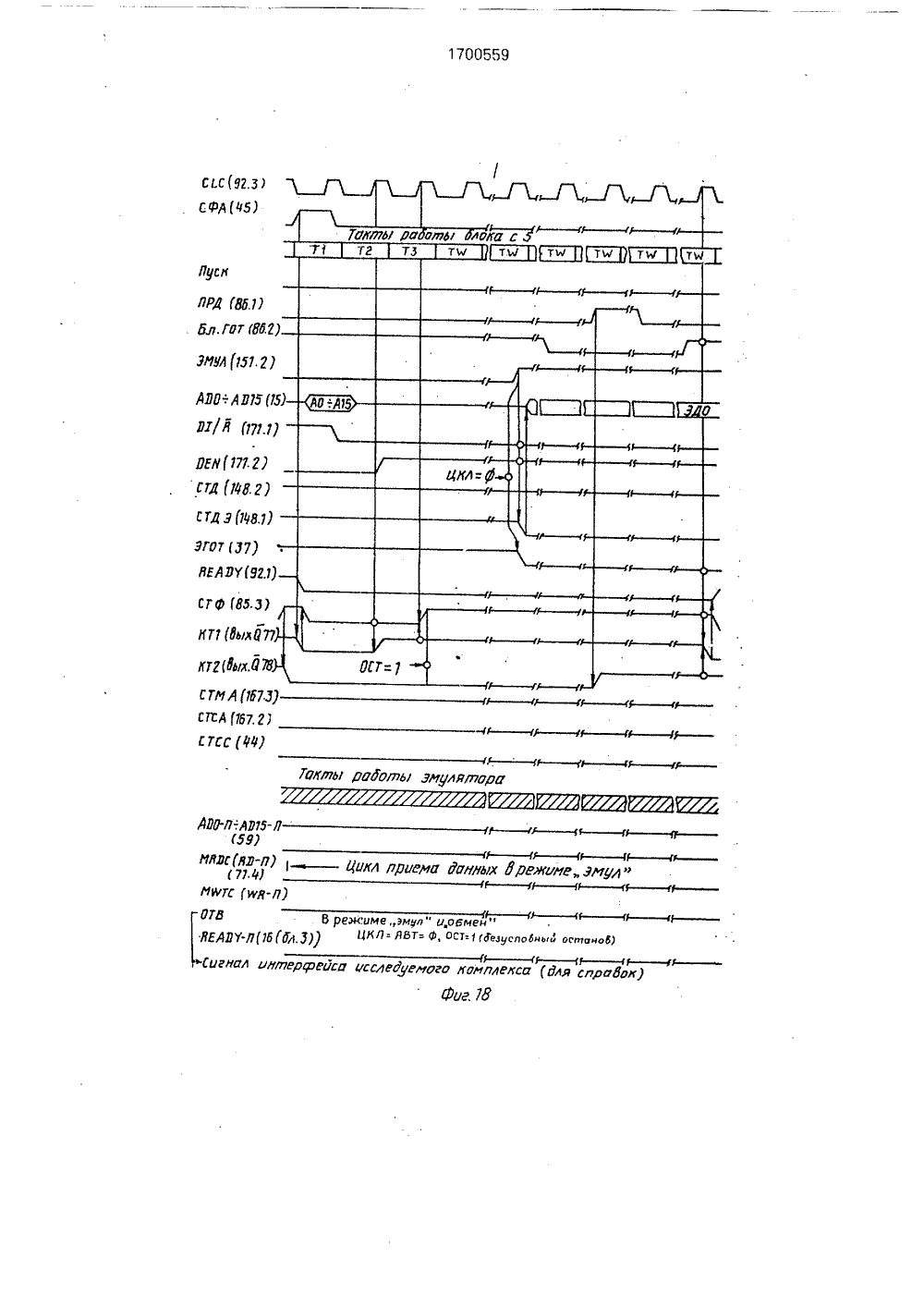

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 700559 9) П ) ц 5 0 06 Р ИЗ ЕТЕНИ САН ЕТЕЛЬС У К АВТОРСКОМУ Изобретение от ной технике.и может отладке программн микропроцессорных рисхемной эмуляцииЦелью изобрете ние быстродействияНа фиг, 1 привед системы; на фиг. 2-1 лока комв, блока хронизарежимов обмена, ия режиров адрепервого ста нова,ния является и работы системы ена структурная 4 - соответствен вышеем фу ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯПРИ ГКНТ СССР(71) Харьковское научно-производственное объединение по системам автоматизированного управления(56) Циделко В,Д. и др, Проектирование микропроцессорных измерительных приборов и систем. - К.: Техника, 1984, с.156, рис,83.Домнин С.Б. и др, Средства комплексной отладки микропроцессорных устройств. М.: Энергоатомиздат, 1988, с.86, 96., рис.2.7. (54) СИСТЕМА ОТЛАДКИ МИКРОПРОЦЕССОРНЫХ УСТРОЙСТВ(57) Изобретение относится к вычислительной технике и может быть использовано при отладке программно-аппаратных средств микропроцессорных систем методом внутрисхемной эмуляции. Цель изобретения - повышение быстродействия системы за счет возможности реализации сложных логических условий остановов при отладке, а также обращений к отдельным заданным носится к вычислитель- быть использовано при о-аппаратных средств систем методом внутячейкам памяти, а не к массивам, Удобство отладки повышается за счет отказа от жесткого распределения памяти, а также "прозрачности" средств эмуляции для пользователя, Для достижения цели в систему введены следующие блоки с соответствующими связями: блок окончания цикла обмена, позволяющий инициировать очередной цикл обмена в системе; блок задания режимов эмуляции, позволяющий осуществлять связь с инструментальным комплексом; блок синхронизации обмена, формирующий необходимые для обеспечения работы системы управляющие сигналы; блоки выбора адреса и регистров адреса, позволяющие формировать сигналы управления выбором адреса, а также осуществлять обмен между шиной обмена и внутренней шиной данных; блок останова, формирующий сигналы останова при различных логических условиях, задаваемых пользователем. Система также содержит процессор, блок коммутации управляющих сигналов, блок синхронизации процессора, блок задания режимов обмена, блок регистров состояния, блок регистров адреса, блок коммутации данных, 5 з,п,ф-лы, 30 ил. 3 табл. кциональные схемы процессора, б мутации управляющих сигнал окончания цикла обмена, Слока си ции процессора, блока задания эмуляции, блока синхронизации блока выбора адреса, блока зада мов обмена, второго блока регист са, блока регистров. состояния блока регистров адреса, блокана группу 63 выходов, При значении СТДЭ = 1 передача данных блокируется, При значении СТД =разрешается обмен данными между входами-выходами 59 и 63 в зависимости от значения сигнала на входе 47,Вход 47 блока 13 предназначен для управления блоком 203 сигналом с выхода 171.1 блока 6 (фиг, 7). При значении сигнала ОТ/В = 1/ф/ данные передаются с шины 63 (59) на выходы 59 (63), Порты Вф, В 1 и В 2 блока 201 предназначены для выдачи на выходах 205,1, 205,2 и 60 соответственно кодов ЭОО-ЭО 7 младшего байта данных (кода инструкции), подставленного блоку 1 для чтения в режимах "Эмуляция" (" Цикл" ), ЭО 8-ЭО 15 - старшего байта данных в указанных режимах, У 01 - У 08 кода сигналов управления остановом,Предлагаемая система обеспечивает обмен информацией с устройством отлаживаемого микропроцессорного комплекса, адресуемый в двадцатиразрядном двоичном адресном пространстве в соответствии с процедурами, предусмотренными, например, для микропроцессора марки КМ 1810 В М 86,С помощью системы отладки, выполняющей функции внутрисхемного эмулятора, под управлением инструментального комплекса возможна реализация следующих функций: выполнение программы пользователя в реальном масштабе времени с оста- новом по заданным условиям; по адресу, типу цикла обмена, используемому сегментному регистру или по сочетанию условий; пуск отлаживаемой систе ы с заданной команды; выполнение программы отлаживаемой системы, по шагам с анализом адреса/данных, слова состояния, используемого сегментного регистра процессора в каждом цикле обмена; анализ и изменение состояния памяти, портов ввода-вывода, внутренних регистров микропроцессора отлаживаемой системы; выполнение циклической записи чтения/данных в заданную ячейку запоминающего устройства или порт ввода-вы вода.Для реализации этих функций система может функционировать в четырех режимах; "Автомат", "Обмен", "Эмуляция" и "Цикл",Управление системой осуществляет инструментальный комплекс более высокого уровня, подключаемый к входам-выходам 17 через интерфейс ИРПС, Обмен между инструментальным комплексом и узлами системы осуществляется посредством блока 5.На фиг,.1 - 14 цепи блокировки работы системы в интервале времени от включения питания до завершения его инициализацииусловно не показаны,Выполнение программ отлаживаемойсистемы, которая подключается к внешней5 шине 16 данных, а также сервисных программ, транслируемых в систему через блок5 инструментальным комплексом осуществляется процессором 1 (фиг. 1).В основе функционирования системы10 отладки лежит предварительное демультиплексирование и параллельная фиксация сигналов микропроцессора в начале каждогоцикла обмена на регистрах 180, 173, 174 и181, 182, 183 с одновременной блокировкой15 готовности процессора 1 блока 65.Сигналы на выходах регистров 180, 173и 174 являются информационными, они поступают на соответствующие порты вводавывода для последующей передачи, если20 это предусмотрено, в инструментальныйкомплекс через группу 17 входов-выходов.Сигналы, выдаваемые процессором 1,фиксируются на регистрах 181, 182 и 183 ипо команде начала цикла обмена мульти 25 плексируются и выдаются на шину 16 (фиг.1) под управлением блоков 3, 4, 6 и 7 всоответствии с временными диаграммами,приведенными на фиг. 16.Одновременно снимается блокировка30 готовности с соответствующего входа 86.2блока 3 (выход соответствующего разрядагруппы 23 выходов блока 2), При этом возникает возможность синхронизировать завершение цикла обмена блоком 1 с шиной35 16. Данные поступают на шину 16 с мультиплексированной шины 15 адреса/данных(фиг. 2) блока 65,В обратном направлении данные поступают с шины 16 на группу 59 входов-вцхо 40 дов блока 13 (фиг, 14), далее через блок 203магистральных элементов - на группу 63входов-выходов блока 13 и, наконец, на шину 15 системы,45 П редлагаемая система позволяет использовать альтернативные источники команд и данных для блока 1(фиг. 2), С одной стороны команды и данные могут поступать с шины 16 системы, С другой стороны эта 50 информация может поступать с шины 14обмена через порты Вб и В 1 блока 201(фиг.14) и блок 202 магистральных элемен, тов,Сигналы, используемые для управления55 и обмена в системе, подразделяются на следующие группы: сигналы микропроцессора, сигналы внутреннего интерфейса ввода-выхода, сигналы портов ввода-вывода, сигналы синхронизации и начальной установки (сигналы извесного микропроцессораКМ 1810 ВМ 86). Для их обозначения признаки-Пи не используется,В примере конкретного выполненияблоков предлагаемой системы рассматривается случай функционирования микропроцессора КМ 1810 ВМ 86 в максимальномрежиме, В этом случае работой микропроцессора управляет контроллер 170 блока 8(фиг. 9), При этом сигналом перехода к началу цикла обмена контроллера 170 (фиг. 9) 10является переход кода состояния 1112 в любое другое на группе 20 выходов блока 65(фиг,.21. Обоатный переход кода на выходе20 в состояние 1112 является сигналом для .блока 170 (фиг. 9) к переходу на завершение 15цикла обмена.Таким образом, до тех пор, пока кодсостояния Я 2, Я 1. Я сохраняет значение.1112, система, выполняющая функции процессора отлаживаемой (проектируемой) системы, с точки зрения последней находитсяв пассивном состоянии, С другой стороны, сточки зрения блока 1 (фиг. 1) системы изменения кода Я 2, Я 1, ф блока 1 изсостояния111 в любое другое являются признаком начала цикла обмена.Для обеспечения синхронизации фиксации сигналов ф-Я 2, А. - А 19, ВНЕ дляпоследующей выдачи их на шину 16 (фиг. 1)или анализа в инструментальном комплексе, подключаемом к группе 17 входов-выходов, в системе используется блок 170,В начале цикла обмена блок 170 формирует на выходе А Е 45 (фиг. 9) импульсныйсигнал СФА(фиг, 18-21), используемый для 35фиксации сигналов Я - Я 2 в регистрах 180(фиг. 11) и 173 (фиг. 10),При этом код адреса А( - А 15 фиксируется в регистрах 174 (фиг. 10) и 183 (фиг. 12),разряды адреса А 16 - А 19 и сигнал ВНЕ (разрешение старшего байта на шине) - в регистрах 173 (фиг, 10) и 182 (фиг. 12),Кроме того, код адреса и слова состояния Щ - Я 2, коды ФА 1 - ФА 19, ФЯ 2 - ФЯЮ свыходов регистров 173 (фиг. 10), 174 и 180 45(фиг. 11) соответственно поступают на блокисравнения 189 - 194 блока 12 (фиг.13).Далее выполнение цикла обмена осуществляется под управлением блоков 3 и 4,которые синхронизируют формирование 50сигнала готовности, а также блоков 6 и 7,которые формируют управляющие сигналыдля процесса эмуляции.При этом, благодаря соответствующейконструкции укаэанных блоков, на входы 55блока 1 (фиг, 1) обеспечивается подача сле- .дующих сигналов (фиг. 18-21): сигнала С.Сна вход 72.1 в течение всего времени существования сигнала СС -П на выходе 93.1блока 4 (фиг,5); синхронная подача сигнала сброса ЯЕЯЕТ на вход 72.2 (фиг. 2) при наличии сигнала РЕЯЕТ-П на входе 93.2 блока 4 (фиг. 5), а также в интервале времени от момента включения питания до завершения инициализации системы; синхронная подача сигнала готовности ВЕАОУ на вход 72,3 (фиг,2), согласованная с временной диаграммой (фиг. 18 - 21) цикла обмена системы при наличии сигналов ЯЕАОУ -П или .ЛЪТ на входе 16 блока 3 окончания цикла обмена; блокировка сигнала готовности КЕАОУ на входе 72,3 блока 1 (фиг, 2), выхода 92,1 .блока 4 (фиг. 5) при наличии сигнала блокировки БЛ,ГОТ на входе 86,2 блока 3 (фиг, 4), который через элементы ИЛИ 83, 84 и 82 устанавливает триггер 78 в единичное состояние; блокировка сигнала готовности РЕАОУ прй наличии в такте ТЗ (фиг. 18-21) сигнала (аппаратного останова по условиям или безусловного) ОСТ с выхода 58 блока 12 (фиг. 1); продолжение цикла обмена после аппаратного останова по сигналу управления передачей ПРД на входе 86.1 (фиг. 4), куда он поступает с выхода соответствующего разряда группы 23 выходов блока 2 (фиг. 3).Блоки б и 7 совместно выполняют функцию управления посредством описанных выше сигналов СТДЭ, СТД, СТМА, СТСС. СФС и ЭГОТ завершением цикла обмена данными между блоком 1 (фиг. 1) с отлаживаемой системой через шину 16 либо с инструментальным комплексом через порты В( и В 1 блока 201 (фиг, 14).Согласование работы блоков б и 7 с временной диаграммой работы блока 1 обеспечивается посредством сигналов С С, КЦО, ОЕК, ОТ/й, СФА, ФЯИ - ФЯ 2 и ПУСК, формируемых соответственно на выходах 92.3 блока 4 (фиг. 5), 29 блока 3 (фиг. 4), 171,2 блока 8 (фиг, 9), 171.1 блока 8 (фиг, 9), 52 блока 10 (фиг. 11), 41 блока 7 (фиг. 8).Кроме того, особенностями согласования функционирования узлов системы является следующее, Сигнал чтения данных (исполнительный) ЯО-П с выхода 71.4 блока 1 (фиг. 2) выдается неранее начала такта Т 2 цикла обмена системы (фиг, 18 - 21). Выдача информационного сигнала блокировки алвтернативных эадатчиков ЕОСК -П с выхода 71.3 блока 1 осуществляется по сигналу блока 65 (фиг. 2) ЮСК, а также по сигналу Е ОСК блокировки альтернативных задатчиков в отлаживаемой системе, формируемому системой на входе 74,4 блока 1. Прием блоком 1 (фиг. 2) сигналов ТЕЯТ и ММ 1 осуществляется как с шины 16 системы, так и с выходов порта В 1 блока 201 (фиг, 14),Блокировка немаскируемых прерыва. ний осуществляется сигналом БЛ.ИМ 1 повходу 74.3 блока 1 (фиг, 2), который поступает с выхода соответствующего разряда порта В 1 блока 75.Сигнал фиксации адреса или состояния, формируемый на выходе элемента ИЛИ 184 (фиг. 12), обеспечивает фиксацию в регистре 182 кода адреса А 16-А 19, ВНЕ в начале цикла обмена блока 1 (фиг, 2) (по сигналу СФА на входе 45 блока 11 (фиг. 12 и фиксацию кода состояния ЯТЗ-ЯТ 7 автоматически в такте Т 2 цикла обмена системы (фиг.18 - 21).Сигнал с выхода элемента ИЛИ 175 (фиг, 10) обеспечивает функции в регистрах 173 и 174 кода адреса А 16 - А 19, ВНЕ в начале цикла обмена блока 1 по сигналу на входе 45 СФА и (или) фиксацию на регистре 173 кода слова состояния процессора ЯТЗ - ЯТ 7, а на регистре 174 состояния мультиплексируемой шины блока 1 АОф-А 015, а также ТИ/ цикла обмена процессора 1 (фиг. 18-21) по сигналу СТРОБ порта В 1 блока 75,Цикл работы системы начинается с установки в нулевое состояние триггеров 78 блока 3 (фиг. 4), триггера готовности 87 блока 4 (фиг, 5) и триггера 77 останова блока 3 (фиг, 4) по установочным входам Я сигналом с входа 45, поступающим с соответствующего выхода блока 8 (фиг. 9). При этом триггер 79 устанавливается в нулевое состояние по единичному выходу сигналом с инверсного выхода триггера 78 (фиг. 4), Наличие на первом 1-входе триггера 78 сигнала нулевого уровня, а на К-входе уровня "Лог, 1" подготавливает переключение этого триггера по первому тактовому сигналу (С С) с выхода 92,3 блока 4 (фиг. 3) в единичное состояние по инверсному выходу в конце такта Т 2 цикла обмена блока 1 (фиг. 15 - 21). В результате этого к такту ТЗ цикла обмена блока 1 на первом,3-входе триггера 78 (фиг. 4) формируется уровень "Лог, 1". Таким образом, по любому импульсу с выхода 92,3 блока 4 (фиг.5), начиная с такта ТЗ цикла обмена блока 1, триггер 78 может переключаться в единичное состояние и формировать сигналы готовности КЕАОУ на выходе 92,1 блока 4 (фиг, 5) и окончания цикла обмена КЦО на выходе 29 блока 3 (фиг, 4) при условии, что на втором и третьем 3-входах триггера 78 к этому моменту времени будут сформированы сигналы единичного уровня, а на К-входе - уровень "Лог, 0",Сигналы уровня "Лог, 0" на К-входе триггера 78 и "Лог, 1" на третьем 3-входе этого триггера формируются при отсутствии сигнала блокировки готовности БЛ.ГОТ на входе 86,2 (фиг, 4), если триггер 77 останова установлен в единичное состояние по нулевому выходу, С другой стороны состояние триггера 77 останова определяется уровнемсигнала останова ОСТ на входе 58 (фиг. 4),который формируется блоком 12 (фиг. 13 кмоменту установки триггера 79 (фиг,4) в5 единичное состояние в конце такта ТЗ циклаобмена блока 1, а также уровнем сигналаПРД на входе 86,1 блока 3.К такту ТЗ все сигналы, определяющиеусловия останова, сформированы и подают 10 ся на схемы 189 - 194 сравнения (фиг. 13),Таким образом, сигнал "Лог. 1" на нулевом выходе триггера 77 останова (фиг, 4)формируется в конце такта ТЗ цикла обмена,если условия останова не сформировались,15 т,е, сигнал ОСТ на входе 58 имеет нулевоезначение или сигнал ПРД на входе 86,1 имеет уровень "Лог. 1",Наличие сигнала высокого уровня натретьем )-входе триггера 78 определяется20 наличием сигнала готовности ВЕАОУ-П высокого уровня на входе 16 блока 3 (фиг, 4) вцикле обмена данными блока 1 с отлаживаемой системой или сигнала готовностиЭГОТ на входе 57 в цикле обмена блока 1 с25 поотами В) и В 1 блока 201 (фиг, 14). Код8992 разрядов СГ 2 - СГ на выходах 85.185.3 определяет состояние, когда блок 1 находится в стадии выполнения такта ТВ/,присутствует сигнал готовности ВЕАОУ-П30 высокого урощя на входе 16 (фиг. 4) илисигнала ЭГОТ на входе 37 низкого уровня.При этом сигнал готовности КЕАОУ на выходе 92.1 не сформирован, поскольку триггер 77 останова установлен в нулевое35 состояние по нулевому выходу, или присутствует сигнал блокировки БЛ.ГОТ низкогоуровня.Сигнал сброса ЯЕЯЕТ формируется навыходе 92,4 триггера 88 благодаря строби 40 рованию сигнала ВЕЯЕТ-П на входе 98,2тактовой частотой С С с выхода элементаНЕ 89,Рассмотрим процесс синхронизацииуправления процессом эмуляции впредла 45 гаемой системе. Начало этого процесса определяется переходом триггера 153 блока 7(фиг. 8) по переднему фронту тактового сигнала С С с входа 32 в нулевое состояние поинверсному выходу, При этом формируется50 начало фронта сигнала низкого уровняСТСС на выходе 44 блока 7, который открывает выходные ключи регистра 181 блока 10(фиг, 11), Это, в свою очередь, приводит кпоявлению на шине 16 (фиг. 1) сигналов кода55 состояния Я 2-П - Яф-П с входов 51 блока 10(фиг. 11).Сигналом СТСС с нулевого выхода триггера 153 (фиг, 8) по Я-входам устанавливаются в нулевое состояние по инверснымвыходам триггеры 1,54 и 156, При этом формируется начало сигналов ОТСА и СТМА навыходах 167,2 и 167.3 соответственно, Указанными сигналами с входов 186,2 и 186.3открываются выходные ключи регистров182 и 183 соответственно, что приводит к 5выдаче на выходах 53 и 54 блока 11 адресных сигналов Аф-П - А 19-П, ВНЕ-П.По переднему фронту очередного импульса СЕС с входа 32 блока 7 (фиг. 8) триггер 156 через триггер 155, выполняющий 10функцию задержки переднего фронта сигнала С.С, устанавливается в нулевое состояние. По заднему фронту сигнала СТМА свыхода 163.3 блока 7 закрываются выходные ключи регистра 183, тем самым завершается выдача сигналов адреса Аф-П - А 15-Пна шину 16 (фиг. 1).В дальнейшем обмен данными междушиной 15 (фиг. 1) АОф - АО 15 и шиной 16системы осуществляется через магистральный элемент 203 (фиг, 14), а обмен междушиной 15 и портами Вф, В 1 блока 201 осуществляется через блок 202 (фиг. 14).Окончание выдачи сигнала СТМА на выходе 167.3 приводит к формированию на 25выходе 167.1 переднего фронта сигналафиксации состояния СФС, который поступает на вход 186,1 блока 11 (фиг, 12). В ыходным сигналом высокого, уровня с элементаИЛИ 184 (фиг. 12) происходит фиксация в 30регистре 152 (при открытых сигналом с входа 186,2 выходных ключах блока 182) состояния шины 15 (фиг. 1) кодом А 16/ЯТЗ -А 19/ЯТ 6, ВНЕ/ЯТ 7 блока 1 (фиг. 2),Поскольку к рассматриваемому моменту времени на шине 15 блоком 1 устанавливается код слова состояния блока 1, то нашине 16 формируется код состояния ЯТЗ-П - .ЯТ 7-П. Одновременно с этим формируетсясигнал СТМА Ч СТСА на выходе 40 блока 7 40(фиг. 8), который поступает на одноименныйвход элемента И 67 (фиг, 2) и разрешаетвыдачу на шину 16 (фиг. 1) сигнала чтенияКО-П с выхода 71,4 группы 18 выходов блока1 (фиг, 2), Кроме того, сигналом с выхода 42 45блока 7 разрешается формирование элементом И 145 блока 6 (фиг, 7) сигнала СТДна выходе 148.2 блока 6.Завершение сигналов СТСС и СТС навыходах 44 и 167.1 блока 7 (фиг. 8) соответственно определяется поступлением сигнала окончания цикла обмена КЦО на вход 29блока 7, сформированного таким образом,чтобы переход сигналов процессора 1 (фиг,2) Я 2 - Яф нэ выходах 20 в состояние 1112 и 55завершение сигнала СТСС на выходе 44 .блока 7 (фиг. 8) произошли в одном тактецикла обмена. Это гарантирует синхронноезавершение цикла обмена процессора и отлаживаемой системы. Завершение сигналов СТСА на выходе167.2 (СТМА Ч СТСА) на выходе 40 происходит по сигналу СФА с входа 45, формируемому в начале следующего цикла обменаблока 1 (фиг, 2) контроллером 170 (фиг, 9),Начало цикла обмена данными блока 1(фиг, 1) с отлаживаемой системой обеспечивается подачей нэ О-вход триггера 153(фиг,8) сигнала уровня "Лог. 1". Изменение этогосостояния О-входа триггера 153 на нулевоевозможно лишь в последнем такте ТЮ циклаобмена (фиг, 15 - 21). При этом подача сигна,ла высокого уровня на О-вход триггера 153может осуществляться тремя способами;программной установкой единичного сигнала ПУСК на входе 169,3 (при нулевом значении сигнала АВТ с входа 169.1); изменениемсостояния Я 2 - ЯИ на выходах 20 (фиг. 2) созначения 1112 на любое другое (при единичном значении сигнала АВТ); кадом типа цикла обмена ФЯ 2 - ФЯ на выходах регистра180, оличающимся от кода 1112 (пассивноесостояние) и от кода 1 ф 2 (код чтения команды) при наличии единичного сигнала ЦКЛ по./завершении сигнала СФА на выходе 41 блока 7(фиг. 8),Сигнал ЭГОТ готовности формируетсяна выходе 37 блока б (фиг. 7) при наличиисигнала ЭМУЛ на входе 151,2 блока б, нулевом значении сигнала ЦКЛ на входе 151,1, атакже в любом цикле обмена, кроме циклачтения кода команды, при единичном значении сигнала ЦКЛ. При этом же условии разрешается формирование сигнала СТДЭ навыходе 148,1 блока б (фиг, 7) и блокируетсявыдача сигнала СТД на выходе 148,2, Формирование сигналов СТДи СТДЭ стробируется действующим единичным значениемсигнала ОЕЙ с входа 150.2 блока 6, которыйформируется на выходе 171.2 блока 8 (фиг.91.Дополнительным условием формирования сигнала СТДЭ является нулевое значение сигнала ОТ/Я с выхода 171.1 блока 8,который поступает на вход 150.1 блока 6(фиг.7). Условие . формирования сигналаСТД определяется, кроме того, нулевымзначением сигнала СТМА Ч СТСА на выходе40 (фиг. 8). Это обусловлено необходимостью блокировки выдачи данных с портовВ, В 1 на шину 15 (фиг. 1 и 2) блока 1 вциклах записи данных и необходимостьюсогласования момента приема (выдачи) данных отлаживаемого комплекса с временнойдиаграммой сигналов шины 16 (фиг. 15 - 21),Функционирование предлагаемой системы осуществляется в соответствии с алгоритмами, приведенными на фиг. 17. Приэтом отдельные этапы, составляющие алгоритмы режимов работы, выполняются в соответствии с временными диаграммами,приведенными на фиг. 15-21,При включении питания блоком 5 (фиг,6) по программе, записанной в блоке 96памяти, осуществляется настройка блоков75, 172, 201, 187 и 188. Устанавливаютсякоды, определяющие безусловный остановблока 1 (фиг, 2) в первом же цикле, и снимаются сигналы блокировки,В результате этого, система переходитв исходное состояние, в котором блок 1(фиг,1) остановлен в такте Тп (по сигналу останова ОСТ на входе 58 блока 3 (фиг. Л) шина 16сохраняет пассивное состояние, а обменданными заблокирован).В исходном состоянии производитсяпередача информации, зафиксированнойна регистрах 180, 173 и 174 (фиг, 11 и 10); винструментальный комплекс через группу17 входов-выходов.На основании анализа этой информации из инструментального комплекса передается управляющее слово, котороеопределяет переход системы из исходногосостояния в один из четырех режимов работы;"Автомат".Анализ управляющего слова осуществляется блоком 94 (фиг, 6) по заданной в блок96 программе. Управляющее слово, крометого, определяет, будет ли выполняться режим со следующими дополнительными функциями: формирование системой сигналаТЕЯТ на одноименный вход блока 65 (фиг,2); формирование системой сигнала ИМ наодноименный вход блока 65 (фиг. 2); формирование системой сигнала ЮГ(-П на выходе 71,3 блока 1 (фиг, 2); блокировка сигналанемаскируемого прерывания чМ 1,Управление формированием этих сигналов осуществляется кодом с выходов порта В 1 блока 75 (фиг. 3).В режиме "Эмуляция" (фиг. 24) из инструментального комплекса через группу 17входов-выходов принимается и заносится на. порты ВЯ и В 1 блока 201 два байта данныхи производится один цикл чтения блока 1(фиг. 2) этих данных с сохранением пассивного состояния шины 16 (фиг. 1), По завершении цикла обмена система возвращаетсяв исходное состояние,В режиме "Обмен" (фиг. 26) производится один цикл обмена блока 1 с отлаживаемой системой по интерфейсу шины 16 (фиг1).В режиме "Цикл" (фиг. 24) из инструментального комплекса через группу 17 входов 10 выходов принимаются и заносятся в порты В.и В 1 блока 201 два байта данных, представляющие собой команду чтения или записи данных в ячейку памяти или порт ввода-вывода. При этом команда должна быть двух- или однобайтной (в последнем случае во втором байте содержится код ЭО Нкоманды чОР), Система настраивается на режим циклического выполнения записанной в порты В, В 1 блока 201 команды, аппаратный останов блокируется. Блок 1 системы в этом режиме читаеткоды с портов Вф и В 1 блока 201 так же, как и в режиме" Эмуляци 4. Другие циклы об мена выполняются по шине 16 аналогичнорежиму Обмен.В режиме "Автомат" система принимаетот инструментального комплекса семь байтов, определяющих условия основного и 20 вспомогательного остановов. Инициируется блок 12 останова (фиг. 1). После этого система настраивается на автоматическое выполнение программы отлаживаемой системы в реальном масштабе времени, Факти чески между двумя циклами обмена по шине16 присутствуе холостой такт. Для блока 1 (фиг. 2) эта задержка проявляется в виде наличия лишнего такта ожидания ТЮ,Выход из режима "Автомат" происходит 30 при останове по заданным условиям(на основе анализа кода состояния СГИ - СГ 2, ко- торый с выходов 30 блока 3 (фиг. 4) поступает на порт В 2 блока 75 (фиг. 3) или по команде поступает через группу 17 вхо дов-выходов из инструментального комплекса).Формула изобретения 1, Система отладки микропроцессорныхустройств, содержащая процессор, блок 40 коммутации управляющих сигналов, блоксинхронизации процессора, блок задания режимов обмена, блок регистров состояния, первый блок регистров адреса, блок коммутации данных, причем группа входов-выхо дов обмена сигналами данных и группауправляющих чтением входов блока коммутации управляюших сигналов соединены соответственно с разрядами данных и управляющими разрядами шины обмена сис темы, группа выходов, управляющихсигналами разрешения блока коммутации управляющих сигналов, соединена с первой группой управляющих входов процессора, группа входов-выходов данных/адреса ко торого через внутреннюю шину данных соединена с группой информационных входов первого блока регистров адреса и первой группой входов-выходов данных блока коммутации данных, группа выходов кода состояния процессора соединена с группами информационных входов блока задания режимов обмена и блока регистров состояния, группы входов-выходов запросов, выходов состояния очереди команд и вторая группа управляющих входов процессора соединены соответственно с разрядами запросов, разрядами состояния очереди команд и управляющими разрядами внешней шины данных системы, первая группа выходов и выход блока синхронизации процессора соединены соответственно с группой входов синхронизации процессора и входом синхронизации блока задания режимов обмена, группа входов блока синхронизации процессора соединена с разрядами синхронизации процессора и с разрядами синхронизации внешней шины данных системы, выход управления фиксацией адреса и выход разряда управления передачей-приемом данных группы выходов блока задания режимов обмена соединены соответственно с одноименными входами первого блока регистров адреса, блока регистров состояния и блока коммутации данных, первая группа выходов выдачи слова состояния микропроцессора, блока регистров состояния соединена с разрядами сигналов состояния внешней шины системы, группы выходов мультиплексированного кода и кода адреса/данных первого блока регистров адреса соединены с соответствующими группами разрядов адреса внешней шины данных системы, первая группа выходов данных, вторая группа входов-выходов данных и первая группа управляющих входов блока коммутации данных соединены соответственно с разрядами данных внешней шины данных, разрядами данных шины обмена и управляющими разрядами шины обмена системы, о т л и ч а ющ а я с я тем, что, с целью повышения быстродействия, она содержит блок окончания цикла обмена, блок задания режимов эмуляции, блок синхронизации обмена, блок выбора адреса, второй блок регистров адреса и блок останова, причем группа входов-выходов адреса/данных процессора соединена через внутреннюю шину данных с первой группой входов данных второго блока регистров адреса, группа выходов кода состояния процессора соединена с группой информационных входов блока выбора адреса, группа информационных выходов блока коммутации управляющих сигналов - с первой группой входов блока окончания цикла обмена, а выходы первых и вторых управляющих разрядов группы информационных выходов блока коммутации управляющих сигналов соединены с первой группой управляющих входов блока синхронизации5 10 сигналов, первым входом блока синхронизации процессора и первым управляющим входом блока выбора адреса, группа выходов, первый выход стробирования, первый 15 и второй выходы инверсного стробирования 40 45 50 20 25 30 обмена и группой управляющих входов блока выбора адреса, выход разряда синхронизации адреса группы управляющих выходов блока коммутации управляющих сигналов соединен с одноименным входом второго блока регистров адреса, группа выходов состояния, первый и второй выходы блока окончания цикла обмена соединены соответственно с группой информационных входов блока коммутации управляющих и второй выход стробирования которого соединены соответственно с группой управляющих входов первого блока регистров адреса, управляющим входом процессора, вторым входом блока синхронизации процессора, управляющим входом блока синхронизации обмена и входом управления связью с внешней шиной данных блок регистров состояния, вторая группа выходов блока синхронизации процессора и выход тактового разряда этой группы соединены соответственно с второй группой входов блока окончания цикла обмена и вторым управляющим входом блока выбора адреса, группа входов-выходов системы соединена с первой группой входов-выходов блока задания режима эмуляции, вторая группа входав-выходов которого соединена с шиной обмена системы, первый и второй выходы и группа выходов блока синхронизации обмена соединены соответственно с первым управляющим входом блока окончания цикла обмена, третьим управляющим входом бло. ка выбора адреса и второй группой управляющих входов блока коммутации данных, вторая группа выходов данных которого соединена с первой группой входов данных блока останова, выход управлений фиксацией адреса блока задания режимов обмена соединен с одноименными входами блока окончания цикла обмена, блока выбора адреса и второго блока регистров адреса, группа выходов блока задания режимов обмена соединена с второй группой упраеляющих входов блока синхронизации обмена, группа выходов второго блока регистров адреса - с группой адресных входов блока останова, группы входов-выходов данных и управляющих входов соответственно второго блока регистров адреса и блока останова соединены с соответствующими разрядами данных и управляющими разрядами шины обмена системы, вторая группа входов данных блока останова соединена с соответствующими разрядами внутренней шиныданных системы, вторая группа выходов блока регистров состояния - с группой информационных входов блока синхронизации обмена, второй и третьей группами входов данных соответственно второго блока регистров адреса и блока останова, выход сигнала останова блока останова соединен с вторым управляющим входом блока окончания цикла обмена, третий управляющий вход которого соединен с разрядом готовности внешней шины данных системы.2. Система по п 1, от л ич а ю ща я ся тем, что блок окончания цикла обмена содержит первый, второй и третий триггеры, элемент И, первый, второй, третий и четвертый элементы ИЛИ, причем нулевой выход первого триггера подключен к инверсному входу первого элемента ИЛИ, выход которого подключен к совмещенным инверсному 3-входу и К-входу второго триггера, а также к первому разряду группы выходов состояния блока окончания цикла обмена, единичный выход второго триггера подключен к первому выходу блока окончания цикла обмена, а нулевой выход второго триггера - к нулевому входу третьего триггера, единичный выход которого подключен к синхровходу первого триггера, к инверсному входу второго элемента ИЛИ, к второму разряду группы выходов состояния блока окончания цикла обмена, к прямому 1-входу второго триггера, инверсный выход третьего триггера подключен к первому входу элемента И, выход которого подключен к второму выходу блока окончания цикла обмена, выход третьего элемента ИЛИ подключен к прямому Л-входу второго триггера и к третьему разряду группы выходов состояния блока окончания цикла обмена, выход четвертого элемента ИЛИ подключен к прямому входу второго элемента ИЛИ, выход которого подключен к прямому входу первого элемента ИЛИ, первая группа входов блока окончания цикла обмена подключена первым разрядом к нулевому входу первого триггера, а вторым разрядом - к инверсному входу четвертого элемента ИЛИ, установочный и информационный входы третьего триггера подключены к заземляющей шине, прямой вход четвертого элемента ИЛИ - к заземляющей шине, вторая группа входов блока окончания цикла обмена подключена первым, вторым и третьим разрядами к синх. ровходам соответственно второго и третьего триггеров и второму входу элемента И, третий и первый управляющие входы блока окончания цикла обмена являются соответственно прямым и инверсным входами третьего элемента ИЛИ, вход управления фиксацией адреса блока окончания циклаобмена подключен к установочным входампервого и второго триггеров, второй управляющий вход блока окончания цикла обме 5 на - к информационному входу первоготриггера.3. Система по п,1, о тл и ч а ю щ а я с ятем, что блок синхронизации процессора содержит первый и второй триггеры, первый,10 второй и третий элементы НЕ, причем инверсный выход первого триггера подключен кпервым разрядам первой и второй группвыходов блока синхронизации процессора,выход первого элемента НЕ - к второму15 разряду первой группы выходов блока, атакже к входу второго элемента НЕ и к синхровходу второго триггера, инверсный выход которого подключен к второму разрядувторой группы выходов блока, выход второ 20 го элемента НЕ подключен к третьим разрядам первой и второй групп выходов блока ик выходу блока, выход третьего элемента НЕ- к информационному входу второго триггера, обнуляющий и информационный вход25 первого триггера, установочные единичныеи нулевой входы второго триггера подключены к заземляющей шине, первый и второйуправляющие входы блока - к установочному единичному входу и синхровходу соот 30 ветственно первого триггера, группа входовблока подключена первым разрядом к входупервого элемента НЕ, а вторым разрядом -к входу третьего элемента НЕ,4, Система поп 1,отличающаяся35 тем, что блок синхронизации обмена содержит пять элементов И, элемент ИЛИ и элемент НЕ, причем выход первого элемента Иподключен к первому входу второго элемента И, инверсный выход которого подключен40 к первому инверсному входу элемента ИЛИи является вторым выходом блока синхронизации обмена, выход третьего элемента Иподключен к первому входу четвертого элемента И и к входу элемента НЕ, выход кото 45 рого подключен к первому входу пятогоэлемента И и является первым выходом блока синхронизации обмена, инверсный выход четвертого элемента И подключен кпервому разряду группы выходов блока син 50 хронизации обмена, выход пятого элементаИ - к второму разряду группы выходов блокасинхронизации обмена, выход элементаИЛИ - к первому входу третьего элемента И,группа информационных входов блока син 55 хронизации обмена подключена первымразрядом к второму входу второго элемента .И, вторым разрядом и третьим разрядом -к первому и второму инверсным входам первого элемента И, вторая группа управляющих входов блока синхронизации обмена510 первым разрядом подключена к инверсному входу четвертого элемента И, а вторым разрядом - к вторым входам четвертого и пятого элементов И, первая группа управляющих входов блока синхронизации обмена подключена первым разрядом к третьему входу второго элемента И и второму инверсному входу первого элемента ИЛИ, вторым разрядом - к второму входу третьего элемента И, управляющий вход блока синхронизации обмена является третьим входом пятого элемента И.5. Система по п.1, о т л и ч а ю щ а я с я тем, что блок выбора адреса содержит пять триггеров, пять элементов И, четыре элемента ИЛИ, элемент задержки и элемент НЕ, причем прямой выход первого триггера подключен к прямому входу первого элемента И, выход которого подключен к первому входу первого элемента ИЛИ, инверсный выход второго триггера подключен к установочным единичным входам третьего и четвертого триггеров и второму выходу стробирования, к входу элемента задержки, инверсный выход которого подключен к первому входу второго элемента И, инверсный выход третьего триггера - к первому разряду группы выходов блока, прямой. выход - к единичному входу пятого триггера и к первому входу третьего элемента И, инверсный выход которого является первым выходом стробирования блока, инверсный выход пятого триггера подключен к синхровходу четвертого триггера, инверсный выход которого подключен к второму разряду группы выходов блока, к вторым входам третьего и второго элементов И, выход четвертого элемента И подключен к второму входу первого элемента ИЛИ, выход которого подключен к информационному входу второго триггера, выход пятого элемента И подключен к первому входу второго элемента ИЛИ, выход которого подключен к синхровходу первого триггера, выход второго элемента И подключен к третьему разряду группы выходов блока, прямой выход третьего элемента И - к второму выходу инверсного стробирования блока, выход третьего элемента ИЛИ - к первому входу четвертого элемента И, выход четвертого элемента ИЛИ - к обнуляющему входу второго триггера, выход элемента НЕ - к первому входу пятого элемента И, к инверсному обнуляющему входу первого триггера и к первому выходу инверсного стробирования блока, группа информационных входов блока первым, вторым и третьим разрядами подключена соответственно к первому, второму и третьему инверсным входам третьего элемента ИЛИ, группа управляющих 15 20 25 30 35 40 45 50 входов подключена первым разрядом к инверсному входу первого элемента И и к второму входу четвертого элемента И, вторым разрядом - к второму входу пятого элемента И, третьим разрядом - к второму входу второго элемента ИЛИ, третий управляющий вход блока является третьим входом пятого элемента И, первый управляющий вход блока - инверсным входом четвертого элемента ИЛИ, вход управления фиксацией адреса блока подключен к синхровходу третьего триггера и к входу элемента НЕ, второй уп,равляющий вход блока подключен к синхровходам пятого и второго триггеров, единичный и информационный входы первого триггера, единичный вход второго триггера, информационный и обнуляющий входы третьего, пятого и четвертого триггеров, а также прямой вход четвертого элемента ИЛИ подключены к заземляющей шине,6. Система по п.1, о т л и ч а ю щ а я с я тем, что блок останова содержит первое и второе программируемые устройства ввода- вывода, шесть схем сравнения, элемент ИЛИ, причем группы выходов первого, второго и первая группа третьего каналов первого программируемого устройства ввода-вывода подключены к разрядам первой группы информационных входов первой схемы сравнения, выход которой подключен к первому входу элемента ИЛИ, вторая группа выходов третьего канала первого программируемого устройства ввода-вывода подключена к первой группе информационных входов второй схемы сравнения, группы выходов первого и второго каналов, а также первая группа выходов третьего кана-. ла второго про-раммируемого устройства ввода-вывода подключены к разрядам первой группы информационных входов третьей схемы сравнения, выход которой подключен к второму входу элемента ИЛИ, вторая группа выходов третьего канала второго программируемого устройства ввода- вывода подключена к первой группе информационных входов четвертой схемы сравнения, выход которой подключен к второму входу элемента ИЛИ, третья группа выходов третьего канала второго программируемого устройства ввода-вывода подключена к первой группе информационных входов пятой схемы сравнения, выход которой подключен к второму входу элемента ИЛИ, третья группа выходов третьего канала первого программируемого устройства ввода-вывода подключена к первой группе информационных входов шестой схемы сравнения, группа входов адреса блока подключена к вторым группам информацион1700559 Таблица 1 Состояние икл Выдача сигнала подтверждения прерывания /ЮТ Чтение данных из внешнего устройства Запись данных из внешнего устройства Останов Выборка команды Чтение из памяти Запись в память Не абочее состояниебл Условия останова По ных входов первой и третьей схем сравнения, группа входов-выходов блока подключена к группе информационных входов-выходов первого программируемого устройства ввода-вывода и к группе информационных входов второго программируемого устройства ввода-вывода, группа управляющих входов блока останова подключена первым разрядом к входу чтения, вторым разрядом - к входу записи первого и второго программируемых устройств ввода-вывода, третий разряд подключен к входу выбора первого программируемого устройства ввода-вывода, четвертый разряд - к первому входу адреса, пятый разряд - к второму входу адреса, шестой разряд - к входу начальной установки первого и второго программируемых устройств ввода-вывода, седьмой разряд - к входу выбора второго программируемого устройства ввода-вывода, третья группа входов данных блока оста- нова подключена к вторым группам информационных входов второй и четвертой схем сравнения, вторая группа входов данных блока останова - к вторым группам информационных входов шестой и пятой 5 схем сравнения, первая группа входов данных блока останова первым разрядом - к единичному установочному входу первой схемы сравнения, вторым разрядом - к единичному установочному входу третьей схе мы сравнения, третьим разрядом - кнулевому, а четвертым разрядом - к единичному установочному входам второй схемы сравнения, пятый разряд подключен к нулевому установочному входу четвертой схемы 15 сравнения, шестой, седьмой и восьмой разряды - к единичным установочным входам четвертой, шестой и пятой схем сравнения, выход второй схемы сравнения подключен к первому входу элемента ИЛИ, выход кото рого является выходом останова блока останова, выход шестой схемы сравнения подключен к первому входу элемента ИЛИ. Подтверждение прерыванияПрием данных с порта ввода-выводаВыдача данных на порт ввода;.выводаждение останова /выполнение команды НЧтение кода инструкцииЧтение данных из памятиЗапись данных в памятьНе использ етсяУсловия останова по сегментному регистру Внйшняд иги,уа Останов в цикле обмена (физический адрес формируется относительно сегмента ЕЯ) Останов в цикле обмена данными со стеком (физический адрес формируется относительно сегмента ЯЯ) Останов в цикле чтения кода инструкции / физический адрес формируется относительно сегмента СЯ / или в цикле обмена когда физический адрес формируется без использования сегментных регистров /относительно нуля/ Останов в цикле обмена, в котором физический адрес о ми ется относительно сегмента ОЯблока коммутации данных; на фиг 15-17 - временные диаграммы функционирования системы в режиме "Цикл"; на фиг, 18 - 21 - то же, в режимах "Эмуляция" и "Обмен"; на фиг, 22 - 30 - схемы алгоритмов функционирования системы во всех указанных режимах,Система для отладки (фиг, 1) содержит процессор 1, блок 2 коммутации управляющих сигналов, блок 3 окончания цикла обмена, блок 4 синхронизации процессора, блок 5 задания режимов эмуляции, блок 6 синхронизации обмена, блок 7 выбора адреса, блок 8 задания режимов обмена, второй блок 9 регистров адреса, блок 10 регистров состояния, первый блок 11 регистров адреса, блок 12 останова, блок 13 коммутации данных, шину 14 обмена, внутреннюю шину 15 данных, внешнюю шину 16 данных, группу 17 входов-выходов системы, входы-выходы 18 - 64 блоков системы,Процессор 1 (фиг, 2) содержит микропроцессор 65, первый 66, второй 67 элементы И, первый 68, второй 69 и третий 70 элементы ИЛИ, первый 71,1 и второй 71,2 выходы состояния очереди команд микропроцессора 65, выход 71.3 третьего элемента ИЛИ, выход 71.4 второго элемента И 67, вход 72,1 синхронизации микропроцессора 65, вход 72.2 начальной установки микропроцессора 65, вход 72.3 готовности микропроцессора 65, первый вход 73,1 первого элемента ИЛИ 68, первый вход 73,2 второго элемента ИЛИ 69, вход 73.3 запроса прерывания микропроцессора 65, второй вход 74.1 первого элемента ИЛИ 68, второй вход 74.2 второго элемента ИЛИ 69, первый вход 74,3 первого элемента И 66, первый вход 74.4 третьего элемента ИЛИ 70,Блок 2 коммутации управляющих сигналов (фиг. 3) содержит программируемое устройство 75 ввода-вывода параллельной информации, первый вход 76,1 чтения, второй вход 76.2 записи, третий вход 76.3 выбора устройства, четвертый вход 76,4 адреса, пятый вход 76,5 адреса, шестой вход 76.6 начальной установки и рограммируемого устройства 75 ввода-вывода параллельной информации,Блок 3 окончания цикла обмена (фиг, 4) содержит первый 77, второй 78, третий 79 триггеры, элемент И 80, третий 81, первый 82, четвертый 83 и второй 84 элементы ИЛИ, выход 85,1 элемента ИЛИ 81, выход 85,2 элемента ИЛИ 82, единичный выход 85,3 третьего триггера 79, вход 86.1 обнуления первого триггера 77, инверсный вход 86,2 элемента ИЛИ 83,Блок 4 синхронизации процессора (фиг 5) содержит первый 87 и второй 88 триггеры первый 89, второй 90 и третий 91 элементыНЕ, инверсный выход 92,1 первого триггера87, выход 92,2 первого элемента НЕ 89. выход 92,3 третьего элемента НЕ 90, инверс 5 ный выход 92,4 второго триггера 88, вход93,1 первого элемента НЕ 89, вход 93,2третьего элемента НЕ 91.Блок 5 задания режимов эмуляции (фиг,6) содержит микро-ЭВМ 94, программируе 10 мое устройство 95 ввода-вывода последовательной информации, ППЗУ 96, ОЗУ 97,регистр 98, счетчик 99, первый 100 и второй101 магистральные элементы, элементы 102ИСКЛЮЩАЮЩЕЕ ИЛИ, первый 103 и вто 15 рой 104 элементы И, элемент ИЛИ 105, первый 106, второй 107 и третий 108 элементыНЕ, кварцевый резонатор 109, внутреннююшину 110, выход 111 разрешения чтения,выход 112 разрешения фиксации адреса,20 группу 113 входов-выходов данных, первуюгруппу 114 выходов данных, первый 115 ивторой 116 выводы для подключения кварцевого резонатора 109, вторую группу 117выходов данных, первый 117.1 и второй25 117,2 разряды второй группы 117 выходовмикро-ЭВМ 94, выход 118 чтения и выход119 записи микро-ЭВМ 94, тестируемыйвход 120 микро-ЭВМ 94, вход 121 сбросапрограммируемого устройства 95, группу30 122 входов-выходов данных программируемого устройства 95, вход 123 чтения и вход124 записи программируемого устройства95, выход 125 готовности приемника, вход126 управление/данные и вход 127 выбора35 устройства программируемого устройства95, выход 128 первого магистрального элемента 100, вход 129 второго магистральногоэлемента 101, выход 130 счетчика 99, вход131 синхронизации, вход 132 и выход 13340 соответственно готовности и запроса приемника терминала, вход 134 и выход 135соответственно готовности и запроса передатчика терминала, группу 136 выходов регистра 98, разряд 137 первой группы 11445 выходов данных микро-ЭВМ 94, группу 138информационных входов ОЗУ 97, группу139 входов-выходов ППЗУ 96, вход 140.1первого магистрального элемента 100, выход 140,2 второго магистрального элемента50 101,Блок 6 синхронизации обмена (фиг, 7)содержит первый 141, второй 142, третий143, четвертый 144, пятый 145 элементы И,элементы 146 ИЛИ и 147 КЕ, выход 148,155 четвертого элемента И 144, выход 148.2 пятого элемента И 145, первый вход 149,1 второго элемента И 142, первый 149.2 и второй149,3 входы первого элемента И 141, инверсный 150,1 и первый 150,2 входы четвертогоэлемента И 144, второй вход 151.1 второго510 15 20 30 35 40 45 50 55 элемента И 142, первый вход 151.2 третьего элемента И 143,Блок 7 выбора адреса (фиг, 8) содержит первый 152, второй 153, третий 154, пятый 155, четвертый 156 триггеры, четвертый 157,1, первый 157.2, пятый 158, второй 159, третий 160 элементы И, третий 161, первый 162, второй 163, четвертый 164 элементы ИЛИ, элемент 165 НЕ, элемент 166 задержки, выход 167.1 элемента И 159, инверсный выход 167.2 триггера 154, инверсный выход триггера 156, первый 168.1, второй 168.2, третий 168,3 входы элемента ИЛИ 161, инверсный вход 169.1 элемента И 157,2, первый вход 169.2 элемента И 158, первыйвход 169.3 элемента ИЛИ 163,Блок 8 задания режимов обмена (фиг. 9) содержит системный контроллер 170, первый 171,1 и второй 171.2 выходы управления передачей информации системного контроллера 170.Второй блок 9 регистров адреса (фиг, 10) содержит программируемое устройство 172 ввода-вывода параллельной информации, первый 173 и второй 174 регистры, элемент ИЛИ 175, разряды 176.1 группы выходов первого регистра 173, разряды 176.2 группы выходов второго регистра 174, вход 177,1 чтения, вход 177.2 записи, вход 177.3 выбора, вход 177,4 адреса, вход 177,5 адреса программируемого устройства 172 ввода-вывода, группы 178,1 и 178,2 входов второго и третьего каналов программируемого устройства 172 ввода-вывода, группы 179,1 и 179.2 информационных входов первого 173 и второго 174 регистров,Блок 10 регистров состояния (фиг, 11) содержит регистр 180 и регистр 181.Первый блок 11 регистров адреса (фиг.12) содержит первый 182 и второй 183 регистры, элемент ИЛИ 184, группу 185,1 информационных входов первого регистра 182, группу 185,2 информационных входов второго регистра 183, первый вход 186,1 элемента ИЛИ 184, управляющий вход 186.2 первого регистра 182, управляющий вход 186.3 второго регистра 183.Блок 12 останова (фиг. 13) содержит первое 187 и второе 188 программируемые устройства ввода-вывода параллельной информации, первую 189, третью 190, вторую 191, четвертую 192, шестую 193, пятую 194 схемы сравнения, элемент ИЛИ 195, группы 196.1, 196.2 выходов первого, второго, а также группы 196,3 и 196,4 выходов третьего канала первого программируемого устройства 187, группу 197(В) входов схемы 189 сравнения, группы 198.1, 198,2 выходов первого, второго, а также группы 198.3 и 198.4 выходов третьего канала второго программируемого устройства 188 ввода-вывода, группу 199(В) входов схемы 190 сравнения, пеовый 200,1, второй 200,2 третий 200,3, четвертый 200.4, пятый 200.5, шестой 200,6, седьмой 200.7, восьмой 200.8 разряды группы 60 входов блока 12 останова.Блок 13 коммутации данных (фиг, 14) содержит программируемое устройство 201 ввода-вывода параллельной информации, первый 202 и второй 203 блоки магистральных элементов, вход 204.1 чтения, вход 204,2 записи, вход 204.3 выбора, вход 204,4 адреса, вход 204,5 адреса, вход 204.6 начальной установки, группы.205.1 и 205,2 выходов первого и второго каналов программируемого устройства 201, входы 206,1 и 206,2 разрешения первого 202 и второго 203 блоков магистральных элементов.Процессор 1 (фиг. 2) предназначен для выполнения программ отлаживаемого микропроцессорного комплекса, различных сервисных программ, транслируемых в систему отладки от инструментального комплекса через группу 17 входов-выходов. Блок 65 может быть реализован на основе известного микропроцессора К 1810 ВМ 86, Системы кодов входов-выходов блока 65 по назначению и алгоритмам функционирования полностью идентичны известному микропроцессору. Входы-выходы имеют следующее назначение: группа 33 входов предназначена для передачи на входы 72.1 (СК), 72,2 (ВЕЗЕТ) и 72,3 (КЕАОУ) блока 65 соответственно сигналов тактовых импульсов, сброса и готовности.Группа 64 входов предназначена для подачи следующих управляющих сигналов с внешней шины 16 данных предлагаемой системы: сигнала ТЕЯТ-П разрешения завершения команды ИlА 1 Т на вход 73.1, немаскируемого запроса прерывания ИМ 1- П на вход 73.2, запроса прерывания МТЯ на вход 73,3 (вход "чТЯ блока 65).Группа 26 входов предназначена для подачи сигналов ЕТЕЯТ разрешения завершения команды И/АТ, формируемой эмулятором, на вход 74.1, немаскируемого запроса прерывания Е ЙМ, формируемого эмулятором, на вход 74.2, блокировки немаскируемого прерывания БЛ.ММ на вход 74,3, а также сигнала ЕОСК блокировки альтернативных задатчиков в отлаживаемой системе, формируемого эмулятором,Вход 40 предназначен для подачи сигнала СТМА, стробирующего выдачу на шину 16 младшей части адреса или сигнала СТСА,стробирующего выдачу на шину 16 старшейчасти адреса..уме эмп" иармен"КЛд ЯВТ= ф, ОСТ:1(Еезусл й осюаноВ)-- 1 -- "// -- Ф ЮУ.Л(76 У Сигнал ипщеррейса исследуемого компялсп л,падок ЭО-: АР 75Р 1/Я йГ ЮЕФ 7 777 Г) СтА (7 ФГс) с тД 31 М,7) тат ГЮ 7)ГАПЧйг.7Тф (85.3) стю Газ стсА Г 767,87 с тсс и)7 окпы работы зкулятор гя приема 6 авных Юргжые. ромул"- Ю -- 11700559 СоотВетсебенна гчладшю а сгпарший байты 1 оииых илц кода ючамэг, преЬаычаченнюе Ю /ще а проц."ж 7 раю РФаютач й рваче ъчулясци мул= 1 РД= . ГР хайде Рмуние УГ 251700559 ТГЬ Т=Д УЮТ =Д 5 РЗЮ 7=Аб саск =Я 7 тпб=Ф =ф Псн:1 троб=1 Яйпь лт ЛЮгг ФЫР ЬТЗ - : 377 /д юрты ю,зг ха,РФ 3131700559 Е 57: Д 9 мх =Д 5 умт: Дб оск =Д 7 Роб = 46 гп. = Ф ю = 1 про оо - :,М 7мадамание- 3 75 ониообка данова усл о%им ск =Ф д =4о 7 м г 2Группа 19 входов-выходов предназначена для обмена сигналами запроса предоставления высшего Рф(ОТО) по входу-выходу 19.1 и низшего Рф(ОТ 1) по входу выходу 19,2 приоритета.Группа 18 выходов блока 1 предназначена для выдачи сигналов (ОЩ и Ю 1) о состоянии очереди команд с выходов 71,1 и 71.2, сигнала Е ОСК-П блокировки альтернативных задатчиков с выхода 71.3 и исполнительного сигнала Р-П чтения данных с выхода 71,4.Группа 15 входов-выходов предназначена для обмена мультиплексированными сигналами А/Д адреса/данных и А/БТ адреса/слова состояния,Группа 20 выходов предназначена для выдачи сигналов кода состяния /Я В, 52/ микропроцессора, характеризующего его текущий цикл работы и определяющего способ использования шины.Кроме того, входы ТЕЯТ, ЙМ 1, Мй/МХ блока 65 предназначены соответственно для подачи сигналов окончания режима ожидания, запроса немаскируемого прерывания и установки режима. Подключение входа МК/МХ к шине отрицательного потенциала источника питания соответствует заданию максимального режима функционирования блока 65. Выходы ОСК и ВО блока 65 предназначены соответственно для выдачи сигналов блокировки и управления чтением,Блок 2 коммутации управляющих сигналов (фиг. 3) предназначен для управления обменом управляющими сигналами через шину 14 между блоком 5 задания режимов змуляции(фиг. 1) и другими узлами системы. Блок 75 может быть реализован, например, на основе известной микросхемы КР 580И К 55,Здесь и далее при описании портов предполагается, что логика их сигналов прямая, а назначение сигналов для каждого порта приводится в порядке возрастания значности разряда порта, начиная с нулевого. Группа 21 входов-выходов блока 2 предназначена для обмена сигналами данных с соответствующими разрядами шины 14, Группа 22 входов предназначена для передачи с соответствующих разрядов шины 14 сигналов управления чтением на вход 76,1 (ЙО) блок 75, управления записью на вход 76.2 (О/й), управления выбооом блока на вход 76.3 (С 5), кода выбора одного иэ трех портов или регистра управляющего слова на входы 76,4 и 76 5 (АИ А 1), а также сигнала сброса на вход 76.6 (Б) блока 75,Группа 23 выходов порта ВИ предназначена для передачи сигнала "Пуск" запускацикла обмена данными блока 1 с устройствами отлаживаемой системы на вход 169.35 блока 7 (фиг. 8), сигнала ПРД разрешенияпродолжения цикла обмена после остановапо условиям или безусловного останова навход 86.1 блока 3 (фиг, 4), сигнала БЛ.ГОТ.блокировки готовности блока 1 на вход 86.210 блока 3 (фиг, 4), сигнала АВТ настройки навыполнение программы отлаживаемой системы в реальном масштабе времени на вход169,1 блока 7 (фиг. 8), сигнала ЭМУЛ блокировки обмена данными между блоком 115 (фиг, 1) и устройствами отлаживаемой системы и разрешения приема данных с выходов205,1 и 205.2 блока 201 (фиг. 14), сигналаЦКЛ настройки системы на циклическое выг 1 олнение команды (обмена данными с пор 20 том ввода-вывода или ячейкой памятиотлаживаемой системы), принимаемой с выходов 205,1 и 205.2 портов В и В 1 блока 201и поступающей на входы 151.1 блока 6(фиг.7) и 169,2 блока 7 (фиг, 8),25 Группа 30 входов порта В 2 блока 75предназначена для приема сигналов СГ 6,СГ 1 и СГ 2 состояния с выходов 85.1, 85,2 и85.3 блока 3 (фиг, 4), При этом, нулевое значение кода этих сигналов соответствует ап 30 паратному останову блока 1 (фиг. 2).Группа 26 выходов порта В 1 блока 75предназначена для выдачи сигнала ЕТЕЯТразрешения завершения команды УЧАТ(формируемого блоком 5 задания режимов35 эмуляции) на вход 74,1 блока 1 (фиг, 2), сигнала ЕММ 1 немаскируемого запроса прерывания (формируемого блоком 5) на вход 742блока 1, сигнала БЛ,КМблокировки немаскируемого прерывания на вход 74,3 блока40 1, сигнала Е ОСК блокировки альтернативных задатчиков в отлаживаемой системе навход 74.4 блока 1, а также сигнала СТРОБ навход 27 блока 9 (фиг, 10) разрешения выдачина входы портов В, В 1 и В 2 блока 17245 состояния мультиплексированного адреса/данных, адреса/слова состояния блока 1шины 15 в такте Т% работы микропроцессора КР 1810 ВМ 6 (блок 1),Блок 3 окончания цикла обмена (фиг. 4)50 предназначен для формирования сигналаокончания цикла обмена через внешнююшину 16 данных (фиг. 1).Триггер 78 (фиг, 4) предназначен дляформирования на выходе 28 сигнала синх 55 ронизации состояния готовности в блоке 4(фиг. 5). Триггер 79 формирует сигнал состояния СГ 2 на выходе 85.3, а также нулевымвыходом управляет выдачей сигнала КЦОчерез элемент И 80 на выходе 29. Триггер 77предназначен для запоминания сигнала1700559 юйа мха 1 Ж 46 я-:югЦЯзтФСоставитель Д.Ванюхинтор О,Хрипта Техред М,Моргентал Корректор Э.Лончакова аз 4468 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ ССС113035, Москва, Ж, Раушская наб., 4/5зводственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 10ОСТ останова, поступающего на вход 58 чтения внешней памяти программ, выходблока 3 с одноименного выхода блока 12 АЕ 112 - сигнала разрешения фиксацииостанова (фиг. 1). адреса, группа 113 ОВ входов-выходов - дляВход 16 блока 3 предназначен для под- обмена сигналами данных, выходы Р 2 2114ачи с соответствующего разряда шины 16 5 - сигналы порта Р 2, выходы СЯ 1 115 и СВ 2сигнала ВЕАОУ-П готовности, разрешаю - для подключения кварцевого резонащего завершения цикла обмена, вход 37 - тора 109, выходы Р 1 117 - сигнала порта Р 1,для подачи сигнала ЭГОТ готовности блока выход ВО 118 - сигнала разрешения чтения1(фиг.1),формируемогосистемойприобме- внешней памяти данных, выход МЯ 119 -не данными между блоком 1 и портами Вф и 10 сигнала разрешения записи внешней памяВ 1 блока 201 (фиг, 14), вход 45 - для подачи ти данных, выход ТО 120 - сигнала, испольсигнала СФА строба фиксации адреса, вход зуемого при выполнении команд перехода,31 - для подачи сигналов ВЕАОУ готовности Блок 95 предназначен для органиэациина вход 31,3, а также сигналов состояниясинхронного и асинхронного обмена послеблока 4 на входы 31;2 и 31.1, 15 довательным кодом между группой 17 вхоБлок 4 синхронизации процессора(фиг. дов-выходов и шиной 110 блока 5,5) предназначен для формирования извест- Этот блок может быть выполнен на осных сигналов ЯЕАОУ готовности, СК такто- нове известной микросхемы марки КР 580вых импульсов и РЕЯЕТ сброса для ВВ 51, представляющей собой универсальсинхронизации микропроцессора типа 20 ное программируемое устройство преобраК 1810 ВМ 86, а также управления работой зования и передачи данных.блока 3 (фиг. 4), Триггеры 87 и 88 предназ- Блок 95 содержит следующие входы иначены для формирования соответственно выходы: входы й 121 сброса, группу О 122сигналов готовности ВЕАОУ и сброса входов-выходов данных, вход ЧТ 123 чте;РЕВЕТ, 25 ния, вход ЗП 124 записи, выход ГПР 125Блок 41 предназначен для подачи сиг- готовности приемника, вход 126 У/О принала стробирования фиксации адреса СФА, знака управление/данные, вход 127 ВУ вывходы 93.1 и 93,2 - для подачи с интерфей- бора устройства, вход ВХП 128сной шины 16 соответственно сигналов так- последовательных данных, выход ВПО 129товой частоты С С-П и сброса начального 30 последовательныхданных, входы 130 синхпуска микропроцессора ВЕЗЕТ-П. ронизации приемника СПР и передатчикаВыходы 92.1, 92.2, 92.3 и 92,4 блока 4 СПО, вход СНХ 131 синхронизации, входпредназначеныдля выдачи сигналов готовно- ГПрТ 132 готовности и выход ЗПрТ запросасти ВЕАОУ управления блоком 3 и сброса 133 приемника, вход ГПТ 134 готовности иРЕЯЕТ, которые поступают соответственно 35 выход ЗПрТ 135 запроса передатчика,на входы 72,3 блока 65 (фиг. 2)31,2. блока 3) Блок 96 (фиг, 6) является перелрограм(фиг,4) 31,1 блока 3 (фиг,4),31,2 блока 3 мируемым ПЗУ и предназначен для хране(фиг. 4), 72.1 блока 65 (фиг. 2), 72.2 блока 65 ния программ обмена данными и(фиг, 2). программами между блоком 5 и портамиБлок 5 задания режимовзмуляции(фиг. 40 ввода-вывода блоков предлагаемой систе 6) предназначен для осуществления приема мы, подключенными к шине 14 (фиг. 1) спо интерфейсу ИРПС от инструментального одной стороны, а также к обмену даннымикомплекса отладки через группу 17 входов- между блоком 5 и инструментальным компвыходов системы(фиг. 1) управляющихслов, лексом по интерфейсу ИРПС через группупередачи сигналов управления работой 45 17 входов-выходовсдругойстороны. ОЗУ 97предлагаемой системы в заданном режиме, предназначено для временного хранениясбора информации о состоянии микропро-, данных для обмена между блоком 5 и указацессора и передачи этой информации по нными абонентами,ийтерфейсу ИРПС в инструментальный ком- Регистр 98 предназначен для фиксацииплекс, 50 восьми младших разрядов адреса обращеБлок 5 может быть выполнен, например, ния блока 94. Старшие разряды адреса обнаосновеизвестнойоднокристальноймик- . ращения формируют на выходах ф - 2ро-ЭВМ (ОМ ЭВМ) типа КР 1816 ВЕ 35, кото- разрядов группу 114 выходов порта Р 2, вырая представлена блоком 94, алгоритмы даваемые блоком 94 автоматически из счетфункционирования и режимы использова чика команд в чтения кода команды.ния блока 94 полностью идентичны извест- Выборка кодов команд иэ РВОМ 96 осуным. ществляется по команде РМЕ с выхода 111Вход 1251 ЙГ блока 94 предназначен блока 94, обмен данными с ВАМ 97 и портадля приема сигнала прерывания, выход ми блоков системы, подключенными черезРМЕ 111 - для выдачи сигнала разрешения группу 36 входов-выходов к шине 14(фиг. 1)10 15 20 25 30 35 40 45 50 55- по сигналам чтения и записи с выходов 118и 119 блока 94 соответственно.В качестве старших разрядов адресаблока 97 БАМ используются сигналы 2 - 6 разрядов порта Р 2, поступающие с выходов 114 блока 94. Седьмой разряд порта Р 2 (выход 137) используется для выборки блока 97, Разряды порта Р 2 24 - 27 устанавливаются программно. Сигналы с выходов разрядов 10 - 15 порта Р 1 через блок 104 элементов И, шину 110 и группу 36 входов-выходов используются для адресации как внутренних элементов блока 5 (фиг, 6), так и элементов, подключенных к шине 14 обмена системы,С момента включения питания системы и до установки на выходах 117.1 и 117.2 разрядов 17 - 16 порта Р 1 кода 10 элементом НЕ 106 фиксируется сигнал СБРОС, который через соответствующий разряд шин 14 поступает на входы 76.6 блока 2 (фиг, 3), 55,6 блока 12 (фиг. 13), 204,6 блока 13 (фиг, 14), 177.6 блока 9 (фиг. 10),Выход управления записью элемента НЕ 107 соединен через шину 14 с входами 76,2 блока 2 (фиг. 3), 177,2 блока 9 (фиг, 10). Выход управления чтением элемента Н Е 108 соединен через шину 14 с входами 76,1 блока 2 (фиг, 3), 177,1 блока 9 (фиг, 10), 55,1 блока 12 (фиг. 13), 204.1 блока 13 (фиг, 14).Кроме того, сигналами с соответствующих адресных разрядов шины 110 через шину 14 и входы 76.4, 76,5 и 76.6 блока 2 (фиг,3), 177.4, 177.5 и 177,3 блока 172 (фиг, 20),55.3, 55.4 и 55,5 блока 12 (фиг. 13), 204,4,204.5 и 204,3 блока 13 (фиг. 14) осуществляется управление указанными блоками по входам А 9, А 1(обращение к порту или регистру управляющего слова) и СЯ (разрешение работы блока) в соответствии с известным для схемы КР 580 ВВ 55 алгоритмом,Блок 99 является генератором синхронизации приемника и передатчика и осуществляет деление частоты приема-передачи, например, с коэффициентом 1/33 для получения на выходе стандартной частоты интерфейса ИРПС.Блоки 100 и 101 предназначены для согласования сигналов с входов-выходов 128 и 129 с линией связи 17. Они могут быть реализованы на известных элементах типа К 170 АП 2,Блок б синхронизации обмена (фиг. 7) предназначен для управления обменом через блок 13 коммутации данных, а .также формирования необходимых для этого управляющих сигналов,Группа 52 входов предназначена для подачи сигналов нулевого ЯО, первого Я 1. второго Я 2 разрядов кода сосояния микропроцессора на еходы 14 ц,; 149.3 и 149 1 с соответствующих выходов регистра 180блока 10 (фиг, 11),Код состояния микропроцессора характеризует текущий цикл работы в соответствии с табл. 1,На входы 42, 150,1 и 150,2 блока 6 (фиг,7) поступают сигналы выдачи кода адреса нашину 16 с выхода элемента И 160 блока 7(ДТ/В) с выхода 171.1 контроллера 170 иразрешения передачи данных (ОЕИ) с выхода 171.2 контроллера 170 блока 8 (фиг. 9),Выход 38 блока 6 (фиг. 7) предназначендля формирования сигнала управления элементом И 158 блока 7(фиг. 8), выход 37 - длявыдачи сигнала готовности блока 1 (фиг, 1),формируемого системой при обмене данными блока 1 с портами В и В 1 блока 201(фиг.14).Группа 39 выходов предназначена длявыдачи с выходов 148.1 и 148.2 соответственно сигналов стробирования приема данных (СТДЭ) блоком 1 из портов Вф, В 1 блока201 (фиг, 14) и стробиоования обмена данными (СТД) блоком 1 через шину 16 (фиг, 1).Блок 7 выбора адреса (фиг. 8) предназначен для формирования сигналов управления выбором адреса при обмене данными всистеме, а также некоторых других сигналовуправления обменом,Триггер 152 предназначен для фикса-ции строба фиксации адреса в циклическомрежиме работы системы, Триггеры 153 - 156предназначены соответственно для формирования на выходе 44 сигнала (СТСС) выдачи на шину 16 (фиг. 1) битов состояния(ЯИ-П-Я 2-П) из регистра 181 блока 10 (фиг.11), определяющего начало цикла обмена пошине 16, для формирования на выходе 167.2сигнала СТСА выдачи на шину 16 старшейчасти адреса (А 16 - А 19, ВНЕ, где ВНЕ, -старший разряд мультиплексированной шины адреса/слова состояния микропроцессора), для формирования Сигналасинхронизации установки триггера 156 поС-входу, для формирования на выходе 167,3сигнала (СТМА) управления выдачей на шину 16 младшей части адреса (АИ-А 15).. Группа 20 входов блока 7 предназначена для подачи сигнала состояния ф, Я 1 и Я 2микропроцессора 65 блока 1 (фиг. 2) на входы 168.1, 168,2 и 168,3 соответственно.Группа 25 входов предназначена дляподачи на входы 169,1, 169.2 и 169.3 сигналов АВТ, ЦКЛ и ПУСК соответственно с выходов одноименных разрядов порта В 9блока 75 (фиг. 3), как описано выше,Входы 29, 45 и 32 предназначены дляподачи сигналов окончания цикла обменаКЦО, строба фиксации адреса, СФА и тактовых импульсов соответственно, которые поступают с выходов элементов И 80 блока 3 (фиг. 4), выхода А 1 Е блока 170 (фиг. 9) ивыхода 92,3 (32) блока 4 (фиг, 5),Выход 44 предназначен для выдачи сигнала СТСС, выходы 167.1, 167.2 и 167.3 - сигналов СФС строба фиксации слова состояния, СТСА стробирования выдачи нашину 16 (фиг. Я старшей части адреса (А 16 -А 19, ВНЕ), СТМА стробирования выдачи на 10шину 16 младшей части адреса соответственно, которые поступают на входы ОЕ блока 181 (фиг, 11), 186,1 блока 11 (фиг. 12),186.2 (ОЕ) блока 182 (фиг. 12), 186.3 блока183 (фиг. 12), 15Выходы 40 и 42 блока 7(фиг. 8) предназначены для выдачи прямого и инверсногосигналов стробирования выдачи на шину 16(фиг. 1) младшей или старшей частей адреса,которые поступают соответственно йа входы элемента И 67 блока 1 (фиг. 2) и элементаИ 145 блока 6 (фиг, 7).Блок 8 задания режимов обмена (фиг. 9)предназначен для осуществления развязкиуправляющей, адресной и информационной 25шин, а также различения внешних устройств и памяти при обращении к ним блока1,.Блок 8 может быть реализован на основе известной микросхемы марки К 301810 ВГ 88. При этом алгоритм функционирования блока 170 и назначение его входоввыходов полностью идентичны известнымНа фиг. 9 показаны только те входы-выходы блока 170, идентификация которых су щественна для пояснения алгоритма работы блока в составе системы.Группа 20 входов предназначена для подачи сигналов состояния Щ Я 1 и Я 2 микропроцессора 65. (фиг. 2). 40Входы и выходы блока 8 (фиг. 9) имеют следующее назначение; вход 34 - для подачи тактовых импульсов с выхода 92.3 блока 4 (фиг, 5), входы АЕй, 10 В и СЕй - входы внешних управляющих сигналов, различаю щих выдачу командных сигналов, режим работы системного контроллера и разрешения выдачи как командных сигналов, так и сигналов управления (при АЕЙ = =1, 10 В = 9 и СЕЙ = 1), блок 170 работает без 50 выдачи семи командных сигналов от внутреннего формирователя командных сигнал.ов, в режиме системной шины и .разрешения выдачи сигнала ОЕй/, выходы ОТ/й 171.1, ОЕИ 171,2 и АЕ 45 - для управ ления приемом-передачей данных, разре- . шения обмена данными и разрешения фиксации адреса.Сигналы с выходов 171.1, 171.2 и 45 блока 8 поступают соответственно на входы 150,1 блока б (фиг. 7), вход 47 блока 13 (фиг.14), 150.2 блока 6 (фиг, 7) и вход 45 блоков 3,7,9, 10 и 11,Второй блок 9 регистров адреса (фиг, 10)предназначен для приема и хранения мультиплексированных сигналов адреса/словасостояния при обмене между шинами 14 и15 (фиг, 1),Блок 72 предназначен для организацииобмена между паритетами Вф - В 2 и группой48 входов-выходов, Он может быть реализо-ван на основе известной микросхемы. КР 580 ИК 55, управляемой сигналами с входов 177.1-177,6, как описано выше. Регистры 173 и 174 предназначены для хранениякодов адреса/слова состояния при обмене,Группа 52 входов блока 9 предназначена для подачи с одноименных выходов блока 10 (фиг. 11) фиксированного на времявыполнения цикла обмена кода Фф - ФЯ 2 типа цикла обмена блока 1 (три младших разряда слова состояния),Группа 48 входов-выходов предназначена для обмена сигналами данных 100 ф 10 О 7 с шиной 14 системы, входы 45 и 27 -соответственно, для подачи сигналов СФАстробирования фиксации адреса с блока 8 исигнала СТРОБ разрешения выдачи на порты В 6 - В 2 блока 172 состояния мультиплексированной шины адреса/данных,адреса/слова состояния блока 1 в такте работы микропроцессора ТВ/ (режим ожидания готовности).Группа 15 входов предназначена дляподачи сигналов А 16 (ТЗ-П-А 19) ЯТб-П адреса/слова состояния микропроцессора (втактах Т 1; Т 2 - старшие разряды адоеса, втактах Т 2 - Т 4 - третий - шестой разряды сло-,ва состояния процессора) с соответствующих разрядов шины 15 на группу 179,1входов, а также сигналов АОИ - АО 15 адреса/данных(в тактах Т 1, Т 2 - младшие 15разрядов адреса, в тактах Т 2 - Т 4 - принимаемые или передаваемые микропроцессоромданные) с соответствующих разрядов шины15 на группу 179,2 входов.Группа 50 выходов предназначена длявыдачи на выходы 176.1 кода сигналовФА 16/ЯТЗ - ФА 19/ЯТ 6, ФВНЕ/ЯТ 17/, фиксированного на время выполнения циклаобмена состояния адресных разрядов А 16 -А 19 блока 1 или после выдачи сигналовСТРОБ 3 - 6 разряда слова, а также выдачина выходы 176,2 кода сигналов ФА -ФА 15/ФА - ФА 7/ фиксированного на время обмена адреса Аф-А 7 микропроцессора65 (фиг. 2) (после выдачи сигнала СТРОБ. навход 27 в порте В 1 блока 172 фиксируетсясостояние разрядов АОО-АО 7 микропроцессора в такте ТЮ).50 55 Группа 50 выходов образуется выходами 176,1 и 176,2 регистров 173 и 174 соответственно.Группа входов порта ВФ блока 172 образуется разрядами группы 52 входов блока 9 и группой 176.1 выходов регистра 173,На входы 178.1 и 178,2 портов В 1 и В 2 блока 172 поступают соответственно разряды ФА - ФА 7 и ФА 8 - ФА 15 группь 1 176.2 выходов,Блок 10 регистров состояния (фиг, 11) предназначен для фиксации кода состояния микропроцессора в процессе обмена. Группа входов 20 блока 10 предназначена для подачи нулевого 3 - второго 52 сигналов состояния микропроцессора блока 41 (фиг, 2). На входы 45 и 44 поступают сигналы СФА стробирования фиксации адреса и СТСС - стробировэния выдачи на шину 16(фиг, 1) кода Яф - Г 2, определяющие начало цикла обмена по шине 16.Группы 52 и 51 выходов блока 10 (фиг, 11) предназначены для выдачи соответственно, сигналов ФЯ - Ф 32 фиксированного на время выполнения цикла обмена кода типа цикла обмена микропроцессора 65 (фиг. 2) (три младших разряда слова состояния) и кода 5-П - Я 2-П слова состояния микропроцессора для передачи на шину 16(фиг, 1).Первый блок 11 регистров адреса (фиг.12) предназначен для приема и хранения мультиплексированных сигналов адреса/слова состояния при обмене между шинами 15 и 16(фиг. 1),Регистр 182 предназначен для выдачи на группу 53 блока 11 кода сигналов А 16/ЯТЗ-П - А 19/БТ 6-П, ВАЕ/Т 7-П мультиплексированного кода адреса/слова состояния (в тактах Т 1, Т 2 - старшие разряды адреса, в тактах Т 2-Т 4 - третий- шестой разряды слова состояния микропроцессора), а также старшего разряда мультиплексированного кода адреса/слова состояния микропроцессора (в тактах Т 1, Т 2 - признак обращения к старшему байту в шестнадцатиразрядном слове данных, в тактах Т 2-Т 4 - старший байт слова состояния микропроцессора),Регистр 183 предназначен для выдачи на группу 54 выходов кода АОД- АО 15 сигналов адреса/данных (в тактах Т 1, Т 2 - младшие 15 разрядов адреса, в тактах Т 2-Т 4 принимаемые или передаваемые микропроцессором данные),На группу 15 входов блока 11 поступают коды сигналов А 16/8 ТЗ -А 19/ЯТ 16, ВН Е/ЯТ 7 (разряды 185,1) и АЯ АО 15 (разряды 185.2) с шины 15 (фиг, 1). Нэ вход 45 поступает сигнал СФА стробировэния фик 5 10 15 20 25 30 35 40 45 сации адреса с одноименного выхода блока 8 (фиг, 9).Группа 43 входов предназначена для подачи на входы 186.1, 186.2 и 186.3 соответственно сигналов СФС стробирования фиксации слова состояния микропроцессора, СТСА стробировэния выдачи на шину 16 старшей части А 16-А 19, ВНЕ адреса микропроцессора и СТМА стробирования выдачи на шину 16 младшей части адреса А 9-А 15, которые поступают с выходов 167,1, 167.2 и 167,3. группы 43 выходов блока 7 (фиг. 8),Блок 12 останова (фиг. 13) предназначен для формирования сигналов останова по различным условиям, задаваемым при отладке. При этом, адреса остановов с учетом возможного ветвления программы могут задаваться как парой: основной адрес и альтернативный, так и отдельно основной или альтернативный.Блоки 187 и 188 предназначены для использования в качестве программируемых портов ввода-вывода, принимающих коды условий останова, Они могут быть реализованы на основе известных микросхем типа КР 580 В В 55,Схемы 189-194 сравнения предназначены для формирования сигналов останова по основному(альтернативному) адресу схемой 189 (190), по заданному типу цикла обмена по основному (альтернативному) адресу схемой 191 (192), по используемому сегментному регистру по основному (альтернативному) адресу схемой 193 (194).Элемент ИЛИ 195 предназначен для формирования нэ выходе 58 сигнала остано,вэ, который поступает на вход блока 3 окончания цикла обмена (фиг. 4), Группа 50 входов предназначена для подачи кода ФА 1-ФА 15 адреса фиксированного на время выполнения цикла обмена с выходов блока 9. Группа 56 входов-выходов - для подачи сигналов данных,300 ф-ЗОО 7 с шины 14 обмена (фиг. 1),Группа 55 входов предназначена для подачи управляющих сигналов с соответствующих разрядов шины 14, как было описано выше,Порты Вф, В 1 и В 2 блока 187 предназначены для формирования на группах 196.1, 196.2, 196,3 и 196,4 выходов соответственно кодов сигналов 1 А 1-1 А 8 первого - восьмого разрядов кода условия останова на основному адресу, кода 1 А 17 - 1 А 19 семнадцатого-девятнэдцатого разрядов кода условия останова по основному адресу и, наконец, кода 1 Щ - 182, 1 ЯТЗЯТ 4 условия останова по типу цикла обмена для основного адреса и кода условия остэновэ по коду используе 1700559 18мого сегментного регистра для основногоадреса,Порты В 6, В 1 и В 2 блока 188 предназначены для формирования на группах 198.1,198.2, 198,3 и 198.4 выходов соответственнокодов 2 А 1 - 2 А 8 первого-восьмого разрядовкода условия останова по альтернативномуадресу, кода 2 А 9 - 2 А 16 девятого - шестнадцатого разрядов кода условия останова поальтернативному адресу, кода 2 А 17 - 2 А 19семнадцатого - девятнадцатого разрядов кода условия останова по альтернативномуадресу, кода 2 Я 7-2 Я 2, 2 ЯТЗЯТ 4 условияостанова по типу цикла обмена по альтернативному адресу и условия останова покодуиспользуемого сегментного регистра приостанове по альтернативному адресу.Группа 52 входов блока 12 предназначена для подачи кода ФЯД-.ФЯ 2 типа циклаобмена фиксированного на время выполнения цикла обмена, группа 57 входов - дляподачи кода А 16/ЯТЗ - А 17/ЯТ 4 шестнадцатого разряда адреса (третьего разряда слова состояния и семнадцатого разрядаадреса) четвертого разряда слова состоянияс шины 15 (фиг, 1).Группа 60 входов блока 12 предназначена для подачи управляющих сигналов условий останова У 01 - У 08 на входы200.1 - 200.8 блока 12 следующим образом:вход 200,1 при У 01 = 1/У 01 = ф/ включает(исключает) адреса в условия останова поосновному адресу; вход 200.2 при У 02 = 1/У 02 = ф/ включает (исключает) адреса А 1 -А 19 в условия останова по альтернативномуадресу; вход 200.3 при УОТ = 1 /У 07 = /разрешает(запрещает) останов по условиямосновного адреса; вход 200.4 при УОЗ ==1/УОЗ = / включает (исключает) в условияостанова по основному адресу тип циклаобмена /Я-Я 2/; вход 200,5 при У 04 = 1/У 04 = / включает (исключает) в условияхостанова по альтернативному адресу тотцикл обмена /ф - Я 2/; вход 200.6 при У 08 =- -1 /У 08 = ф/ разрешает (запрещает) остановпо условиям альтернативного адреса; вход200,7. при У 05 = 1/У 05= ф/ включает(исключает) в условиях останова по основному адресу код используемого сегментногорегистра (ЯТЗ, ЯТ 4); вход 200.8 при У 06 = 1/У 06 = ф/ включает (исключает) в условияхостанова по альтернативному адресу кодиспользуемого сегментного регистра (ЯТЗ,ЯТ 4). Присутствие кода С 16 на группе 60 входов инициирует безусловный остандв в каждом цикле обмена,.Формирование условий останова по типу цикла обмена в зависимости от сигналовна выходах 196.4 (198,4) осуществляется в соответствии с табл, 2.Формирование условий останова по типу используемого сегментного регистра (СЯ.5 ОЯ, ЯЯ, ЕЯ ) в зависимости от значений сигналов на выходах 196,5 (198.5) осуществляется в соответствии с табл. 3.Схемы 189 - 194 срабатывают при совпа 10 45 АО 15 (в тактах Т 1, Т 2 - младшие пятнадцать разрядов адреса, в тактах Т 2 - Т 4 - принима 50 55 15 20 25 30 35 40 дении условий останова. При этом на выходе блоков 189 - 194 формируется сигнал"Лог. 1". Поскольку выходы блоков 189 - 194 объединены по "монтажному ИЛИ", то сиг.нал останова может быть сформирован только при наличии сигналов "Лог, 1" на выходе схем сравнения, обслуживающих все типы остановов.Для исключения возможности формирования какого-либо сигнала останова достаточно установить выход соответствующего блока в состояние "Лог, 1", Принудительная установка в "0" любого из блоков, входящих в соответствующую группу(189, 191, 193 или 190, 192, 194), приводит к тому, что соответствующая группа командоаппаратов не будет формировать сигнал оста нова, Установка в "1" всех блоков сравнения группы приводит к безусловному останову в каждом цикле обмена,Блок 13 коммутации данных (фиг. 14) предназначен для коммутации потоков данных при обмене между шинами 15 и 16 (фиг.1). Блок 201 является программируемым портом ввода-вывода, который может быть выполнен на известной микросхеме марки КР 580 ВВ 55. Управление этим блоком по входам 204,1 - 204.6 осуществляется аналогично тому, как было описано выше. Блоки 202 и 203 являются магистральными эле-, ментами, коммутирующими потоки данных при обмене,Группа 62 входов-выходов предназначена для обмена кодами 10 - 107 данных с шиной системы, группа 63 входов-выходов - для обмена кодами адреса/данных АОО -емые или передаваемые микропроцессором данные) с шиной 15 системы (фиг. 1).Группа 59 входов-выходов блока 13 (фиг. 14) предназначена для обмена кодами адреса/данных АОД-П-АО 15-П с шиной 16 системы, группа 39 входов - для подачи на входы 206.1 и 206.2 соответственно сигналов ГТДЭ строба приема данных микропроцессором с портов В, В 1, блока 201 и СТД - стробэ обмена данными микропроцессора по шине 16, которые поступают с выходов 148.1 и 148.2 блока 6 (фиг. 7).При значении сигнала СТДЭ =6 данные передаются с портов Вф и В 1 через блок 202

СмотретьЗаявка

4719071, 17.07.1989

ХАРЬКОВСКОЕ НАУЧНО-ПРОИЗВОДСТВЕННОЕ ОБЪЕДИНЕНИЕ ПО СИСТЕМАМ АВТОМАТИЗИРОВАННОГО УПРАВЛЕНИЯ

БАЖЕНОВ СЕРГЕЙ ЕВГЕНЬЕВИЧ, МОЧЕНКОВ АНДРЕЙ ВЛАДИМИРОВИЧ, ОДНОКОЗОВ ВЛАДИМИР ИВАНОВИЧ, СИЗОНЕНКО ОЛЕГ АЛЕКСАНДРОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ТОПОРКОВ ВАЛЕНТИН ВАСИЛЬЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ

МПК / Метки

МПК: G06F 11/28

Метки: микропроцессорных, отладки, устройств

Опубликовано: 23.12.1991

Код ссылки

<a href="https://patents.su/41-1700559-sistema-otladki-mikroprocessornykh-ustrojjstv.html" target="_blank" rel="follow" title="База патентов СССР">Система отладки микропроцессорных устройств</a>