Интерполятор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 987634

Автор: Полосин

Текст

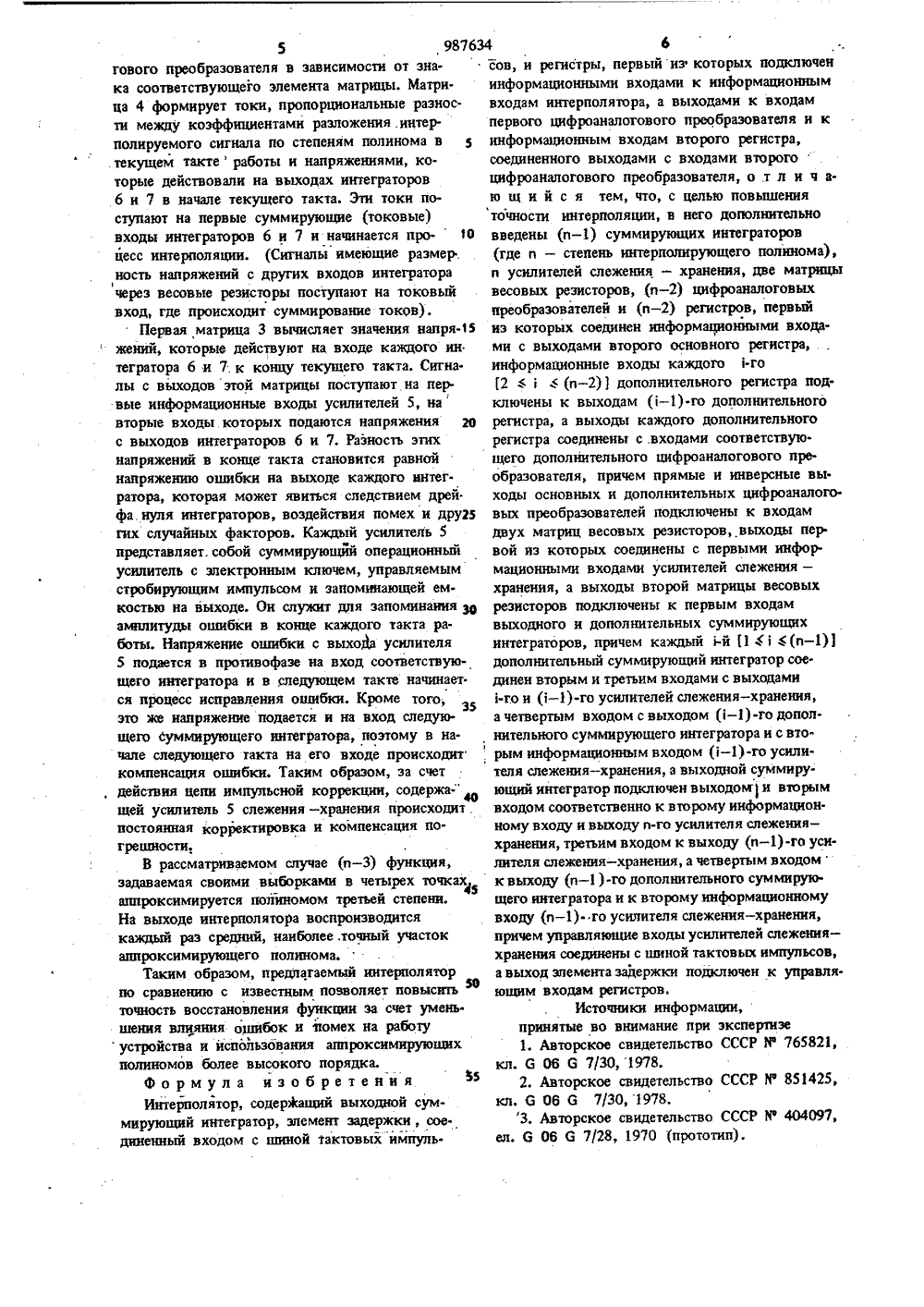

, С. Полоси Ульяновский политехнический ийстнтут"с 4 Фк) Заявител 54) ИНТЕРПОЛЯТО жащнй сум- апоминающие Изобретение относится к автоматике и вычислительной технике, в частности, к устройствам восстановления формы сигналов, заданных своими значениями, в дискретные моменты времени.Известен интерполятор, содер мирующие интеграторы, ключи, з элементы и сумматоры 1).Недостатками интерполятора являются пониженная точность и сложность конструктивной реализации.Известен также интерполятор, содержащий генератор импульсов, счетчик, ключи, операционный усилитель, интеграторы, сумматор и блок памяти узловых значений функции и ее производной 12). Недостатком данного интернолятора является ограниченная область применения.Наиболее близким к предлагаемому является интерполятор, содержащий выходной суммирующий интегратор, элемент задержки, сое 20 диненный входом с шиной тактовых импуль сов, и регистры, первый иэ которых подключен информационными входами к информациощым входам интерполятора, а выходами - к входам первого цифро - аналогового преобразователя и к информационным входам второго регистра, соединенного выходами с входами второго цифро - аналогового преобразователя, причем выходы цифро-аналоговых преобразователейподключены к входам выходного суммирующего интегратора, а входы обнуления регистров соединены непосредственно или через элемент задержки с,. шиной тактовых импульсов 3),Недостатком этого устройства является пониженная точность интерполяции.Цель изобретения - повьппеиие точности интерполяции.Указанная цель достигается тем, что в интерполятор, содержащий выходной суммирующий интегратор, .элемент задержки, соединенный входом с шиной тактовых импульсов, и регистры, первый из которых подключен информационными входами к информационным входам интерполятора, а выходами к входам первого цифро - аналогового преобразователя и к ив формационным входам второго регистра, соединенного выходами с входами второго34 5 10 15 20 25 30 40 45 55 3 9876 цифро - аналогового преобразователя, дополнитель но введены (и - 1) суммирующих интеграторов (где и - степень интерполнрующего полинома), и усилителей слежения - хранения, две матри-; цы весовых резисторов, (и - 2) цифро-аналого.вых нреооразователей и (и - 2) регистров, пер.вый нз которых соединен информационнымивходами с выходами второго основного регистра, информационные входы каждого -го(2и - 2 дополнительного регистра подключены к выходам (-1) -го дополни.тельного регистра, а выходы каждого допой-.нительного регистра соединены с выходамисоответствующего дополнительного цифро - аналогового преобразователя, причем прямые иинверсные выходы основных и дополнительныхпифро - аналоговых преобразователей подключены к входам двух матриц весовых р;зисторов,выходы первой из которых соединены с первыми информационными входами усилителейслежения - хранения, а выходы второй матрицы весовых резисторов подключены к первымвходам выходного и дополнительных суммирующих интеграторов, причем каждый -и(1 (о - 1) 1 дополнительный суммирующий интегратор соединен вторым и тре.тьим входами с выходами -го и ( - 1)-гоусилитслей слежения - хранения, а четвертымвходом с выходом ( - 1)-го дополнительногосуммирующего интегратора и с вторым информационным входом ( - 1)-го усилителя слежения - хранения, д выходной суммирующий интегрдтор. подк:почен выходом и вторым входомсоответственно к второму информационномувходу и выходу и-го усилителя слежения - хра 35пения, третьим входом к выходу (и - 1)-гоусилителя слежения - хранения, а четвертымвходом к выходу (0-1).го дополнительного суммирующсго интегратора и к второму инфор. мационному входу (и - 1)-го усилителя слеже. ния - хрднеиия, причем управляющие входы усилителей слсжснпя - хранения соединены с шиной тактовых импульсов, а выход элемента задержки подключен к управляющим входам регист- ров.Нд чертеже изображена блок - хсемд лредлагдемого интерлолятора (для случая п=3).Устройство содержит два основных регистра 1, два основных цифроаналоговых преобразователя 2, первую и вторую матрицы 3 и 4 весовых резисторов, и усилителей 5 слеженияхранения, выходной суммирующий интегратор6, (о - 1) дополнительных суммирующих интеграторов 7, шину 8 тактовых импульсов, элемент 9 задержки, (и - 2) дополнительных цифро - аналоговых преобразователя 10 и (и - 2)дополнительных регистра 11. Первый из основ.ных регистров 1 подключен информационнымивходами к информационным входам интерполя. тора, а выходами - к входам первого основного цифро - аналогового йреобрдзователя 2и к информационным входам второго основного регистра 1, соединенного выходами свходами входного основного цифро-аналоговогопреобразователя 2.Первый. из дополнительных регистров 11соединен информационными входами с выходами второго основного регистра 1, информационные входы каждого -го (2и - 2) дополнительного регистра 11 подключены к выходам (1-1)-го дополнительного регистра 11,а выходы каждого из регистров 11 соединеныс выходами соответствующего дополнительногоцифро - аналогового преобразователя 10. Пря.мые и инверсные выходы цифро - аналоговыхпреобразователей 2 и 10 подключены к входамматриц 3 и 4 весовых резисторов, выходы первой 3 иэ которых соединены с первыми информационными входами усилителей 5 слежения - хранения. Выходы второй матрицы 4 подключены к первым входам выходного суммирующего интегратора 6 и дополнительных сумми.рующих интеграторов 7, Каждый -й (1 (и - 1) дополнительный суммирующий ин. тегратор 7 соединен вторым и третьим входамис выходами -го и (1 - 1)-го усилителей 5 слежения - хранения, а четвертым входом с выходом ( - 1)-го интегратора 7 и с вторым информационным входом ( - 1)-го усилителя 5,Управляющие входы всех усилителей 5 подключены к шине 8 ввода тактовых импульсови к входу элемента 9 задержки, выход которого соединен с управляющими входами регистров 1 и 11, Выходной суммирующий интегратор 6 подключен выходом к вторым входамсоответственно к второму информационномувходу и выходу и-го усилителя 5, третьим входом - к выходу (и - 1)-го усилителя 5, а четвертым входом к выходу (и - 1).го интеграто.ра 7 и к второму информационному входу(и - 1)-го усилителя 5.Интерполятор работает следующим образом,Каждый такт начинается подачей на шину 8стробирующего импульса, по заднему фронтукоторого элемент 9 задержки формирует управляющий импульс, Этот импульс вызываетсдвиг информации в цепочке регистров 1 и 11и прием внешней информации в первый из ре.гистров (в том случае, когда каждый нз регистров выполнен по двухтактной схеме на основном и буферном регистрах,элемент 9 задерж.ки может быть исключен из состава интерпол ятора),цифровые значений преобразуются цифро -аналоговыми преобразователями 2 и 10 и аналоговую форму и поступают на входы мат.риц 3 и 4. Рзисторы в матрицах подключаютсяк прямому и инверсному выходу цифро - аналогового преобразователя в зависимости от знака соответствующего элемента матрицы, Матрица 4 формирует токи, пропорциональные разности между коэффициентами разложения . интерполируемого сигнала по степеням полинома в.текущем тактеработы и напряжениями, которые действовали на выходах интеграторов6 и 7 в начале текущего такта. Эти токи поступают на первые суммирующие (токовые)входы интеграторов 6 и 7 и начинается процесс интерполяции. (Сигналы имеющие размер.ность напряжений с других входов интегратора1через весовые резисторы поступают на токовыйвход, где происходит суммирование токов).Первая матрица 3 вычисляет значения напря жений, которью действуют на входе каждого ннтегратора 6 н 7. к концу текущего такта. Сигна.лы с выходов этой матрицы поступают на лер.вые информационные входы усилителей 5, навторые входы которых подаются напряжения 2 пс выходов интеграторов 6 и 7. Разность этихнапряжений в конце такта становится равнойнапряжению ошибки на выходе каждого интегратора, которая может явиться следствием дрей.фа нуля интеграторов, воздействия помех и дру 2 Згих случайных факторов. Каждый усилитель 5представляет. собой суммирующйй операционныйусипитель с электронным ключем, управляемымстробирующим импульсом и запоминающей емкостью на выходе. Ои служит для запоминания З 1амплитуды ошибки в конце каждого такта работы. Напряжение ошибки с выхода усилителя5 подается в противофазе на вход соответствующего интегратора и в следующем такте начинает.ся процесс исправления ошибки. Кроме того,это же напряжение подается и на вход следую.щего Суммирующего интегратора, поэтому в начале следующего такта иа его входе происходиткомпенсация ошибки. Таким образом, за счет, действия цени импульсной коррекции, содержа-"щей усилитель 5 слежения - хранения происходит.постоянная корректировка и компенсация погрешности,В рассматриваемом случае (и - 3) функция,задаваемая своими выборками в четырех точкахишроксимируется полиномом третьей степени.На выходе интерполятора воспроизводитсякаждый раз средний, наиболее. точный участокаппроксимирующего полинома.Таким образом, предлагаемый интерполяторпо сравнению с известным позволяет повысить56точность восстановления функции за счет умень.щения ющяния ошибок и помех на работуустройства и йспользования аппроксимирующихполиномов более высокого порядка.Формула изобретения "эИнтерполятор, содержащий выходной суммирующий интегратор, элемент задержки, сое.диненный входом с шиной тактовых импуль 5 987634 6сов, и регистры, первый из которых подключенинформационными входами к информационнымвходам интерполятора, а выходами к входампервого цифроаналогового нреобразоватепя и кинформационным входам второго регистра,соединенного выходами с входами второгоцифроанапогового преобразователя, о .т л и ч а.ю щ и й с я тем, что, с целью повышенияточности интерполяции, в него дополнительновведены (и - 1) суммирующих интеграторов(где и - степень интерполирующего полинома),и усилителей слежения - хранения, две матрицывесовых резисторов, (и - 2) цифроаналоговыхпреобразователей и (и - 2) регистров, первыйиэ которых соединен информационными входами с выходами второго основного регистра,информационные входы каждого 1-го2(и - 2)1 дополнительного регистра подключены к выходам ( - 1)-го дополнительногорегистра, а выходы каждого дополнительногорегистра соединены с.входами соответствующего дополнительного цифроаналогового преобразователя, причем прямые и инверсные выходы основных и дополнительных цифроаналоговых преобразователей подключены к входамдвух матриц весовых резисторов, выходы пер.вой из которых соединены с первыми инфор.мационными входами усилителей слежения -хранения, а выходы второй матрицы весовыхрезисторов подключены к первым входамвыходного н дополнительных суммирующихинтеграторов, причем каждый -й 11(и - 1дополнительный суммирующий интегратор соединен вторым и третьим входами с выходами-го и (1 - 1) -го усилителей слежения-хранения,а четвертым входом с выходом ( - 1) -го дополнительного суммирующего интегратора и с вторым информационным входом ( - 1) -го усилителя слежения - хранения, а выходной суммирующий интегратор подключен выходоми вторымвходом соответственно к второму информацион.ному входу и выходу и-го усилителя слежения -хранения, третьим входом к выходу (и - 1) -го усилителя слежения - хранения, а четвертым входомк выходу (и - 1) -го дополнительного суммирующего интегратора н к второму информационномувходу (и - 1)- го усилителя слежения - хранения,причем управляияцие входы усилителей слеженияхранения соединены с шиной тактовых импульсов,авыход эпементазадержки подключен к управля.ющим входам регистров.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССР Р 765821,кл. 6 06 6 7/30, 1978.2. Авторское свидетельство СССР й". 851425,кл, 6 06 6 7/30, 1978,3. Авторское свидетельство СССР Хф 404097,ел. 6 06 6 7/28, 1970 (прототип).987634 Составитель С, КазиновТехред С. Чигунова едактор Ю, С ктор Н, Король акзз 103063 одписн Проектная, 4 Тираж 704 ВНИИПИ Государственного комитета по делам изобретений и открытий 313035,;Москва, Ж, Раушская наб., д

СмотретьЗаявка

3280036, 17.04.1981

УЛЬЯНОВСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

ПОЛОСИН СЕРГЕЙ СТЕПАНОВИЧ

МПК / Метки

МПК: G06G 7/30

Метки: интерполятор

Опубликовано: 07.01.1983

Код ссылки

<a href="https://patents.su/4-987634-interpolyator.html" target="_blank" rel="follow" title="База патентов СССР">Интерполятор</a>

Предыдущий патент: Многофункциональный тригонометрический преобразователь

Следующий патент: Устройство для вычисления корней приведенного квадратного уравнения

Случайный патент: Импульсный дождевальный аппарат