Программируемое логическое устройство

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

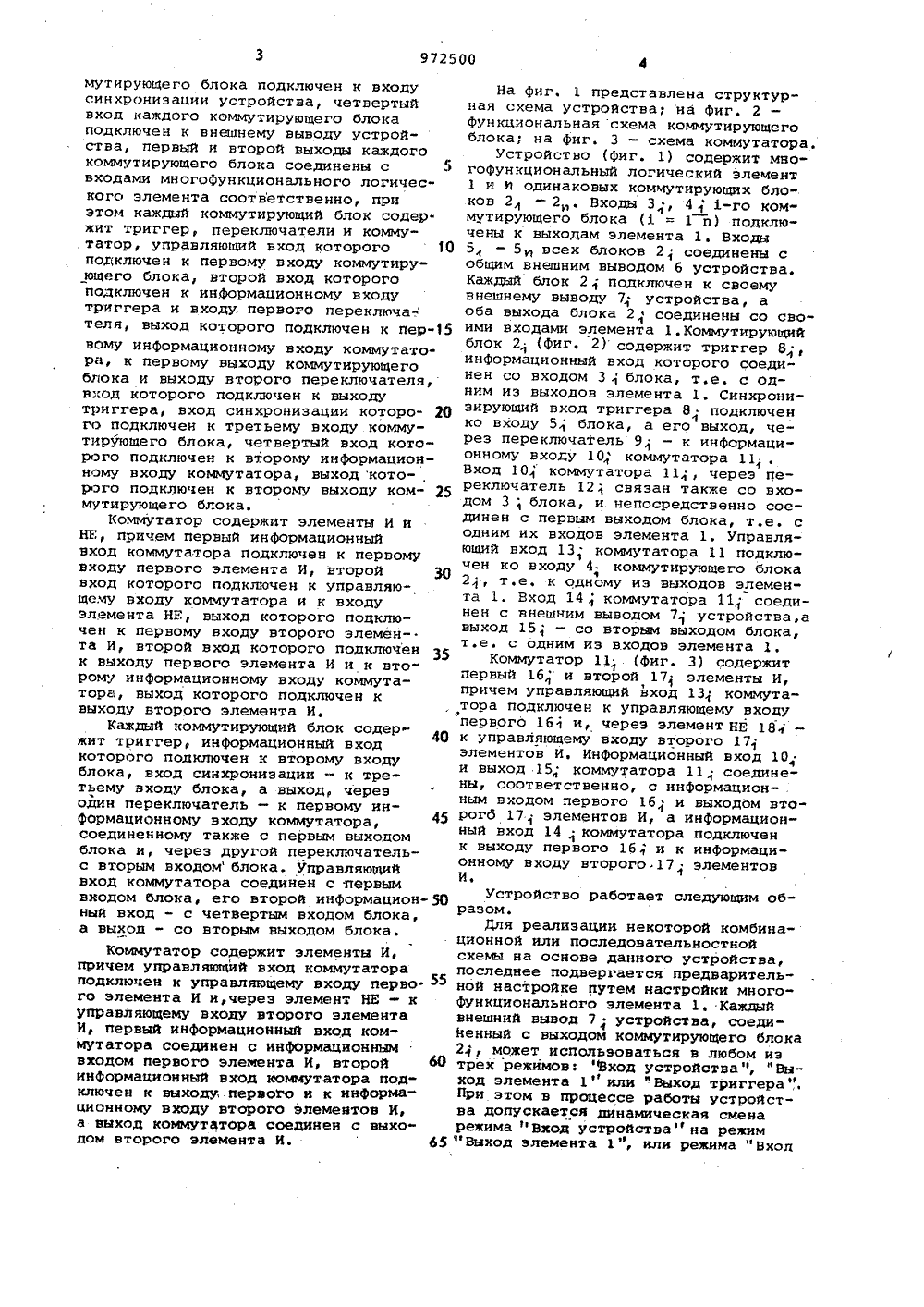

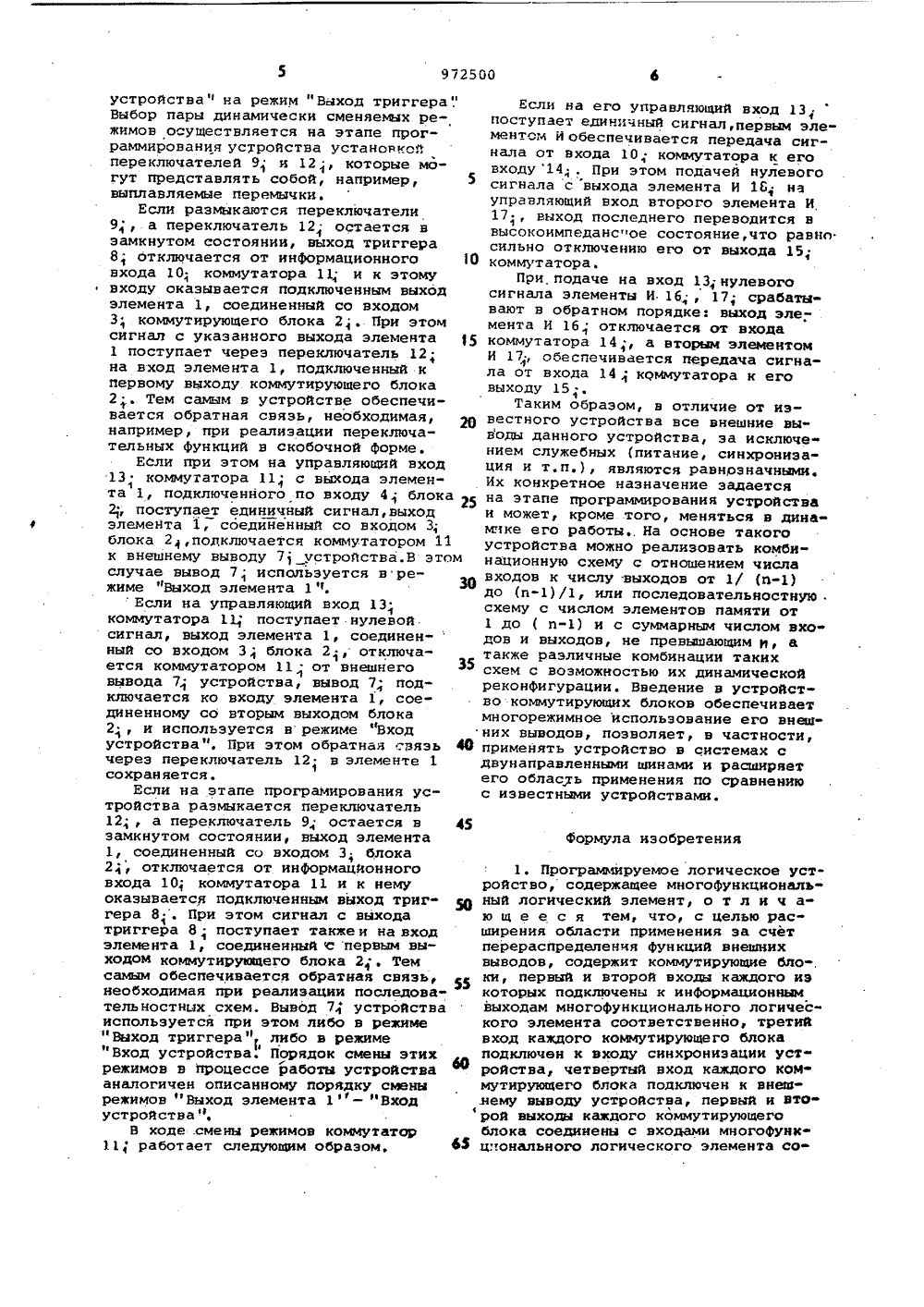

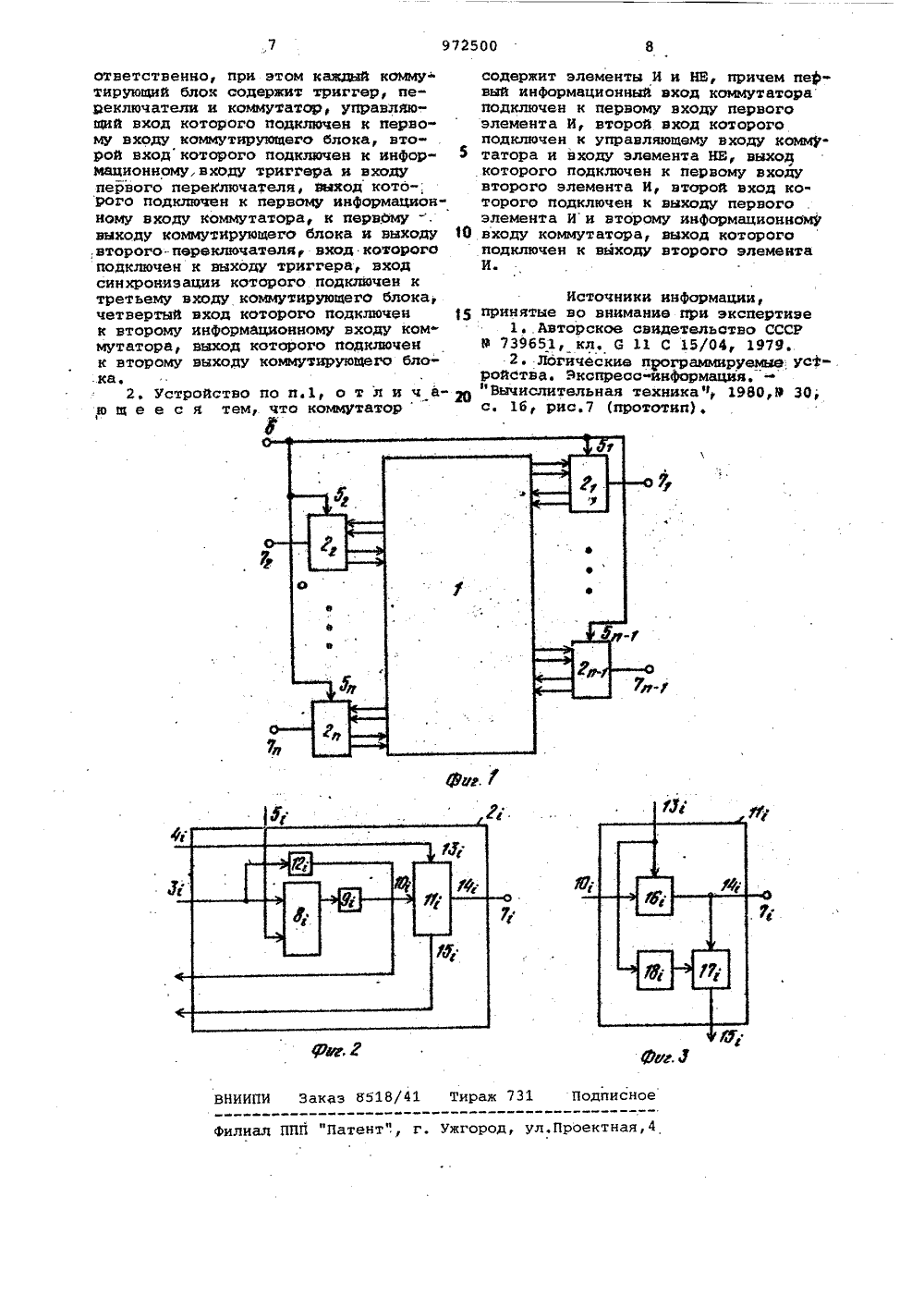

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик и 972500(22) Заявлено 27,02. 81 (21) 325171 б/18-24с присоединением заявки Нов(23) Приоритет -Опубликовано 071182, Бюллетень М41 1 И М. Кл.з О Об Р 7/ОО Государствеииий комитет СССР ио делам. изобретений и открытий1 И)УДК б 81. 3 (088. 8) Дата опубликования описания 07. 11.82 Ю.Ъ.Бузунов, Н.Н.Шипилов и В,И,Бородин(54) ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОИСТВО Изобретение отйосится к вычислительной технике и может быть использовано, в частности, при разработке больших интегральных схем(ПЗЖ), размещаемые на одном крксталле и содержащие матрицы логическихэлементов И, ИЛИ и триггеры (1),Недостатком этого устройства является его низкая универсальность,обусловленная стандартным.назначением внешних выводов одна часть выводов в них используется в качествевходов, а другая - в качестве выходов устройства,Наиболее близким,к предложенномупо технической ущностиявляется программируемый логический блок, содержащий матрицу основных и дополнительных логических элементов И, элементы ИЛИ и синхронизируемые триггеры2) .Недостаткам известного устройстваявляется ограниченность его применения, обусловленная однозначным распределением функций внешних выводов.Одна группа выводов в устройстве используется в режиме "Вход устройства", другая - только в режиме "вы" ход триггера", и,лишь третья группа выводов может использоваться как врежиме "Вход устройства", так и в ,режиме фВьтход элемента ИЛИ". С помощью такого устройства нельзя,например, реализовать комбинационную схему с числом выходов,йревышающкм число выводов третьей группы, поскольку выходные сигналы на выводах . второй группы будут запаздывать иа один такт относительно сигналов на выводах третьей группы. Кроме того, на соотношение числа входов и выхо дов схем, для реализации которых,прерразначено устройство, нвлагаются кесткке ограничения. Все это сужает область применения устройства.Цель изобретения - расширение об-: 2 О ласти устройства за счет перераспределения функций внешних выводов.Поставленная цель достигается тем,что программируемое лагкчесжое устройство, содержащее многофункциональный логический элемент, содержит коммутирующие блоки, первмй к второй входЫ каждого из которых подключены к информационным выходам многофункциоч нальногологического, элемента соот- ветственно, третий вход каждого ком 972500мутирующего блока подключен к входусинхронизации устройства, четнертыйвход каждого коммутирующего блокаподключен к внешнему выводу устройства, первый и второй выходы каждогокоммутирующего блока соединены с 5входами многофункционального логического элемента соответственно, приэтом каждый коммутирующий блок содер"жит триггер, переключатели и комму. татор, упранляющий вход которого 1 Оподключен к первому входу коммутирующего блока, второй вход которогоподключен к информационному входутриггера и входу, первого переключа-.теля, выход которого подключен к пер ному информационному входу коммутатора, к первому ныходу коммутирующегоблока и выходу второго переключателя,вход которого подключен к выходутриггера, вход синхронизации которого подключен к третьему входу коммутирующего блока, четвертый вход которого подключен к второму информационному входу коммутатора, выход которого подключен к второму выходу ком" 25мутирующего блока.Коммутатор содержит элементы И иНЕ, причем первый информационныйвход коммутатора подключен к первомувходу первого элемента И, второй 30вход которого подключен к управляющему входу коммутатора и к входуэлемента НЕ, выход которого подключен к первому входу нторого элемента И, второй вход которого подключен З 5к выходу первого элемента И и к нторому информационному входу коммутатора, выход которого подключен квыходу второго элемента И,Каждый коммутирующий блок содержит триггер, информационный входкоторого подключен к второму входублока, вход синхронизации - к третьему входу блока, а выход, черезодин переключатель - к первому информационному входу коммутатора, 45соединенному также с первым выходомблока и, через другой переключательс вторым входом блока. Управляющийвход коммутатора соединен с первымвходом блока, его второй информацион ный вход - с четвертым входом блока,а выход - со вторым выходом блока.Коммутатор содержит элементы И,причем управляющий вход коммутатораподключен к управляющему входу первого элемента И и,через элемент НЕ - куправляющему входу второго элементаИ, первый информационный вход коммутатора соединен с информационнымвходом первого элемента И, второй 60информационный вход коммутатора подключен к выходу,.первого и к информационному входу второго элементов И,а выход коммутатора соединен с выхо"дом второго элемента И. 65 На Фиг. 1 представлена структурная схема устройства; на фиг, 2функциональная схема коммутирующегоблока; на фиг. 2 - схема коммутатора.Устройство (фиг. 1) содержит многофункциональный логический элемент1 и И одинаковых коммутирующих бло"кон 2 л - 2,. Входы 2,;, 4, 1-го коммутирующего блока (1 = 1 и) подключены к выходам элемента 1. Входы5 - 5 всех блоков 2; соединены собщим внешним выводом 6 устройства.Каждый блок 2подключен к своемувнешнему выводу 7 устройства, аоба ныхода блока 2 соединены со своими входами элемента 1Коммутирующийблок 2 (Фиг. 2)содержит триггер 8,информационный вход которого соеди"нен со входом 2блока, т.е. с одним из выходов элемента 1. Синхронизирующий вход триггера 8 подключенко входу 5 блока, а его выход, через переключатель 9 - к информационному входу 10,; коммутатора 11Вход 10.; коммутатора 11, через переключатель 12 связан также со входом 2блока, и,непосредстненно соединен с первым выходом блока, т,е. содним их входов элемента 1. Упранляющий вход 12; коммутатора 11 подключен ко входу 4 коммутирующего блока2, т.е, к одному из выходов элемента 1. Вход 14коммутатора 11,; соединен с внешним выводом 7 устройства,авыход 15 - со вторым вйходом блока,т.е. с одним из входов элемента 1,Коммутатор 11 . (Фиг. 2) содержитпервый 16 и второй 17 элементы И,причем управляющий вход 12 кошута"тора подключен к управляющему входупервого 16 и, через элемент НЕ 18 -к управляющему входу второго 17элементов И. Информационный вход 10и выход 15 коммутатора 11соединены, соответственно, с информационным входом первого 16 и выходом второгб 17 элементов И, а информационный вход 14коммутатора подключенк выходу первого 16 и к информационному входу второго 17 элементовИ,Устройство работает следующим образом.Для реализации некоторой комбинационной или последовательностнойсхемы на основе данного устройства,последнее подвергается предварительной настройке путем настройки многоФункционального элемента 1. Каждыйвнешний вывод 7 устройства, соедийенный с выходом коммутирующего блока2(, может использоваться в любом изтрех режимовг цВход устройства", "Выход элемента 1 или "Выход триггера ",.При этом и процессе работы устройства допускается динамическая сменарежима "Вход устройствами на режим972500 10 формула изобретения 1. Программируемое логическое устройство, содержащее многофункциональный логический элемент, о т л и ч аю щ е е с я тем, что, с целью расширения области применения за счет перераспределения функций внешних выводов, содержит коммутирующие бло-, ки, первый и второй входы каждого иэ которых подключены к информационным выходам многофункционального логического элемента соответственно, третий вход каждого коммутирующего блока подключен к входу синхронизации устройства, четвертый вход каждого коммутирующего блока подключен к внеш.нему выводу устройства, первый и втО рой выходы каждого коммутирующего блока соединены с входами многофункционального логического элемента соустройства " на режим "Выход триггера ".Выбор пары динамически сменяемых режимов осуществляется на этапе ггрограммирования устройства установкойпереключателей 9 и 12, которые могут представлять собой, например, 5выплавляемые перемычки.Если размыкаются переключатели9, а переключатель 12 остается взамкнутом состоянии, вйход триггера8 отключается от информационноговхода 10 коммутатора 11 и к этомувходу оказывается подключенным выходэлемента 1, соединенный со входом3 коммутирующего блока 2 . При этомсйгнал с указанного выхода элемента 51 поступает через переключатель 12;на вход элемента 1, подключенный кпервому выходу коммутирующего блока2 . Тем самым в устройстве обеспечивается обратная связь, необходимая,например, при реализации переключательных функций в скобочной форме.Если при этом на управляющий вход13 коммутатора 11 с выхода элемен 1та 1, подключенного по входу 4 блока 252;, поступает единичный сигнал, выходэлемента 1, соедйненный со входом 3;блока 2,подключается коммутатором 11к внешнему выводу 7 устройства.В этомслучае вывод 7 используется в режиме "Выход элемента 1 ч. 30Если на управляющий вход 13коммутатора 13.; поступает нулевойсигнал, выход элемента 1, соединен-ный со входом 3 блока 2 , отключа фется коммутатором 11от внешнеговывода 7 устройства, вывод 7 подключается ко входу элемента 1, соединенному со вторым выходом блока2 , и используется в режиме фВходустройства". При этом обратная связь 46через переключатель 12 в элементе 1сохраняется.Если на этапе програмирования устройства размыкается переключатель12;, а переключатель 9 остается взамкнутом состоянии, вйход элемента1, соединенный со входом 3; блока2, отключается от информационноговхода 10; коммутатора 11 и к немуоказывается подключенным выход триг- щгера 8 , При этом сигнал с выходатриггера 8 поступает такжеи на входэлемента 1, соединенный с первым выходом коммутирующего блока 2 . Темсамым обеспечивается обратная связь,необходимая при реализации последовательностных схем. Вывод 7 устройстваиспользуется при этом либо в режиме"Выход триггера " либо в режиме1Вход устройства. Порядок смены этих6режимов в процессе работы устройствааналогичен описанному порядку сменырежимов Выход элемента 1 ф - "Входустройства ",В ходе .смены режимов коммутатор11; работает следующим образом. М Если на его управляющий вход 13; поступает единичный сигнал, первым элементом И обеспечивается передача сигнала от входа 10 коммутатора к его входу 14, При этом подачей нулевого сигнала с выхода элемента И 16 на управляющий вход второго элемента И 17, выход последнего переводится в высокоимпедансое состояние,что равно сильно отключению его от выхода 151 коммутатора.При подаче на вход 13; нулевого сигнала элементы И. 16;, 17; срабатывают в обратном порядке: вйход элемента И 16 отключается от входа коммутатора 14, а вторым элементом И 17, обеспечивается передача сигнала от входа 14коммутатора к его выходу 15.Таким образом, в отличие от известного устройства все внешние выводы данного устройства, за исключением служебных (питание, синхронизация и тп,), являются равнозначными. Их конкретное назначение задается на этапе программирования устройства и может, кроме того, меняться в дииамчке его работы., На основе такого устройства можно реализовать комбинационную схему с отношением числа входов к числу выходов от 1/ (и) до (и)/1, или последовательностную схему с числом элементов памяти от 1 до ( и) и с суммарным числом входов и выходов, не превышающим И, а также различные комбинации таких схем с возможностью их динамической реконфигурации. Введение в устройство коммутирующих блоков обеспечивает многорежнмное использование его внешних выводов, позволяет, в частности, применять устройство в системах с двунаправленными шинами и расширяет его облас 7 ь применения по сравнению с известными устройствами."Г ираж 731 Подписное ВНИИПИ Заказ о ал ППП "Патент", г. Ужгород, Ул,Проектная,4 ответственно, при этом каждый комму- тирующий блох содержит триггер, переключатели и коммутатор, управляющий вход которого подключен к первому входу коммутирующего блока, второй входкоторого подключен к информационному, входу триггера и входу первого переКлючателя, выход кото-; рого подключен к первому информации" ному входу коммутатора, к первому -. выходу коммутирующего блока и выходу второго-переключателя вход которого подключен к выходу триггера, вход синхронизации которого подключен к третьему входу коммутирующего блока, четвертый вход которого подключен к второму информационному входу коммутатора, выход которого подключен к второму выходу коммутирующего блока2. Устройство по п,1, о т л и ч а,ю щ е е с я тем, что коммутаторК содержит элементы И и НЕ, причем первый информационный вход коммутатора подключен к первому входу первого элемента И, второй вход которого подключен к управляющему входу комму" татора и входу элемента НЕ, выход которого подключен к первому входу второго элемента И, второй вход которого подключен к выходу первого элемента Ии второму информационному 30 входу коммутатора, выход которогоподключен к выходу второго элемента И. Источники информации,д принятые во внимание при экспертиве1. Авторское свидетельотво СССР9 739651, кл. О 11 С 15/04 1979.2Логические программируемые усФ-.ройства. Экспресс-информация.О "Вычислительная техникач, 19 В 0,9 30,с. 16 рис.7 (прототип.

СмотретьЗаявка

3251716, 27.02.1981

ПУШКИНСКОЕ ВЫСШЕЕ ОРДЕНА КРАСНОЙ ЗВЕЗДЫ УЧИЛИЩЕ РАДИОЭЛЕКТРОНИКИ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ, ПРЕДПРИЯТИЕ ПЯ А-7162

БУЗУНОВ ЮРИЙ АНАТОЛЬЕВИЧ, ШИПИЛОВ НИКОЛАЙ НИКОЛАЕВИЧ, БОРОДИН НИКОЛАЙ ИННОКЕНТЬЕВИЧ

МПК / Метки

МПК: G06F 7/00

Метки: логическое, программируемое

Опубликовано: 07.11.1982

Код ссылки

<a href="https://patents.su/4-972500-programmiruemoe-logicheskoe-ustrojjstvo.html" target="_blank" rel="follow" title="База патентов СССР">Программируемое логическое устройство</a>

Предыдущий патент: Устройство для управления вводом информации в электронную вычислительную машину

Следующий патент: Устройство для сравнения чисел

Случайный патент: Насадка шахтной крепи