Устройство для испытания дискретных интеграторов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 966764

Авторы: Шепелевский, Ярыгин

Текст

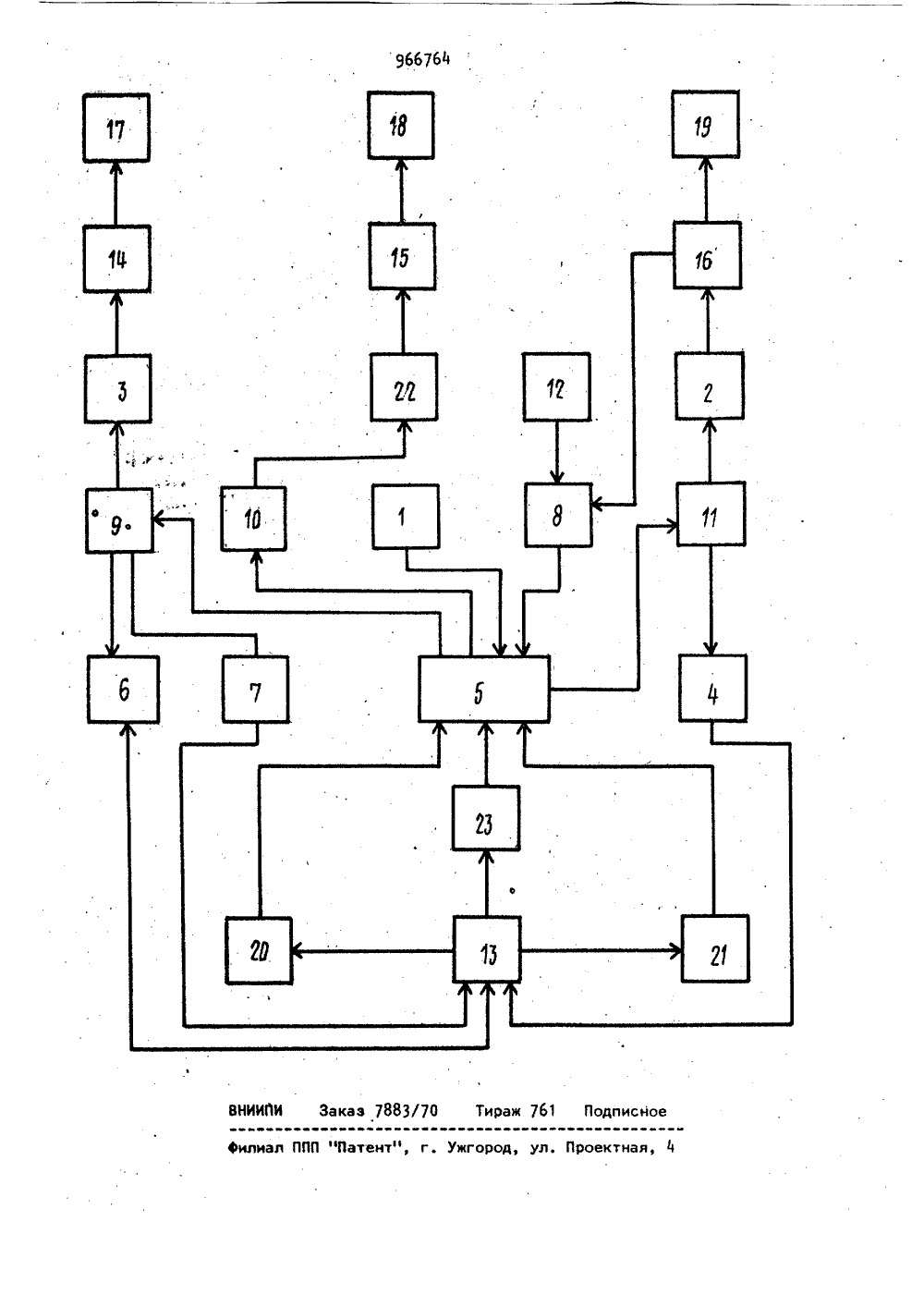

Союз СоветскихСоциалистическихРеспублик АВТОРСКОМУ СВИДЕТЕЛЬСТ(22)Заявлено Н 01 С 9/22 с присоединением заявки Ркударетвениый коиите СССР па делам изобретений и открытиХата опубликования описания 18. 10.8(72) Авторыизобретения рыгин Л,Ю. Шепелевский и А 1 т(1 СОМн,11 л ТЕЩ т.-.Р)т 1/.1Севастопольское отделение Всесоюзного нау но исследовательского, проектно-конструкторс ого и технологического института сточников тома 7) Заявитель) УСТРОЙСТВО ДЛЯ ИСПЫТАНИЯ ДИСКРЕТНЫХ ИНТЕГРАТОРОВ Изобретение относится к системам автоматического контроля и может быть использовано при исследованиях и испытаниях интеграторов дискретного действия.По основному авт. св. Х 822302 известно устройство для испытания дискретных интеграторов, обеспечивающее проверку погрешности зарядноразрядного цикла при многократном циклировании, содержащее генератор меток, соединенный со схемой управления; генератор тока разряда, который через логический ключ соединен с выходом схемы управления, а второй вы-. ход этого логического ключа подключен к последовательно соединенным счетчику времени разряда, дешифратору и индикаторному устройству; генератор тока заряда, который через второй логический ключ также соединен со схемой управления, а второй выход этого ключа подключен к последовательно, соединенным счетчику времени заряда, дешифратору и индикаторному устройству, при этом дешифраторэтой цепи и задатчик времени зарядачерез схему совпадения подключенык схеме управления. Генераторы токазаряда и разряда соединены также с1 исследуемым интегратором, которыйчерез параллельно включенные устройство сравнения и схему защиту подключенк схеме управления. Кроме того, името ется цепочка последовательно соединенных между собой и подключенныхк схеме управления через логический.ключ счетчика циклов, дешифратора ииндикаторного устройства 13Недостатком известного устройстваявляется дополнительная погрешность,возникающая при разряде интеграторовмалым током, мейее 10 мкА и обуспов"ленная тем,что при малых токах разрядда найряжение "отсечки"(падение напря.жения на электродах интегратораЙослевыработки рабочего вещества) нарастает медленно вследствие протекания на3 96676электродах неуправляемых электрохимических процессов не связанных спереносом основного рабочего вещества. При этом для различных интеграто,ров наблюдается значительный разброспо времени протекания этих йроцессов.Цель изобретения - повышение точности определения погрешности зарядно-разрядного цикла, соУказанная цель достигается тем,что в устройство для.испытания дискретных интеграторов введены втораясхема сравнения, вход которой соединен с дискретным интегратором, а выход - с одн-.м из входов схемы управления, и второи генератор тока разряда, выход которого соединен диск-ретным интегратором, а вход - через;логический ключ с одним из выходовсхемы управления.- На чертеже представлена структурная схема устройства,аУстройствь содержит генератор меток времени 1, счетчик времени заряда 2, счетчик времени разряда 3, генератор тока заряда 4, схему управления 5, первый генератор тока разряда 6, второй .генератор тока разряда 7, схему совпадений 8, логическиеключи 9- 11, задатчик времени заряда12, дискретный интегратор,13, дешифраторы 14-16, индикаторные устройства 17-19, первое устройство сравнения 20, схему защиты 21, счетчик циклов 22 и второе устройство сравнения 23,Устройство работает следующим образом.При необходимости занесения в интегратор определенного количества4 Оэлектричества при известной величине тока заряда оператор задает необходимое время заряда задатчиком в 1 емени заряда 12. При этом соответствующий выход дешифратора 16 счетчика вре.мени заряда 2 подключается к схемесовпадения 8.Время заряда начинается при подаче оператором команды "Пуск" в схемууправления 5. При этой команде схемауправления 5 подключает дискретный Оинтегратор 13 к генератору тока заряда 4 через логический ключ 11. Одно-временно со схемой управления 5 илогическим Ключом 11 разрешается,лрохождение импульсов с генератора меток Ивремени 1 на счетчик времени заряда2, дешифратор 16 и индикатор 19. По, мере заполнения счетчика на индика 4торном табло индицируется время за-. ряда дискретного интегратора. По окончании заданного времени положительный уровень с дешифратора 16 поступает на схему совпадения 8, которая через схему управления 5 и логический ключ 11 отключает дискретный интегратор 13 от генератора тока заряда 4, а счетчик времени заряда 2 от генератора меток времени 1, Конечное значение времени заряда фиксируется на индикаторном табло 19.При необходимости снятия с интегратора занесенного количества электричества при малом токе разряда оператор задает его величину первым ге-нератором тока разряда 6. Первое уст-. ройство сравнения 20 настраивается на порог, превышающий падение напряжения на интеграторе в процессе разряда с учетом температурных вариаций, т.е. порог, соответствующий началу увеличения напряжения на интеграторе в процессе разряда.,Второе устройство сравнения 23 соответственно настраивается на максимально допустимое напряжение отсечки. Второй генератор тока разряда 7 настроен на величину максимально допустимого тока для данного типа интегратора,Время разряда начинается при подаче команды "Пуск" в схему управления 5. При этой команде схема управления 5 подключает дискретный интегратор 13 к первому генератору тока и первому и второму устройствам сравнения 20 и 23, Одновременно схемой управленйя 5 и логическим ключом 9 разрешается прохождение импульсов с генератора меток времени 1 на счетчик времени разряда 3, дешифратор 14 и индикатор 17. По мере заполнения счетчика 3 на индикаторном табло 17 индицируется время разряда дискретного интегратора 13.По окончании разряда на интегратор 13 начинает расти напряжение, которое фиксирует первое устройство сравнения и подает сигнал в схему управления 5, которая через логический ключ 9 отключает первый генератор тока разряда 6 от интегратора 13 и подключает к нему второй генератор тока разряда 7. При этом скорость нарастания напряжения на интеграторе 13 резко возрастает, и по достижению максимально допустимого напряжения отсечки срабатывает второе уст966764, 6интегратора", "Циклирование" и позволяет проводить исследования и испытания электрохимических дискретных ин.теграторов на надежность при малыхтоках разряда с повышенной точностью. формула изобретения Источники информации,принятые во внимание при экспертизе 23 1. Авторское свидетельство СССР М 822302, кл. Н 01 6 9/22, 16.04.79.5ройство сравнения 23, посылая сигнал в схему управления 5, которая отключает через .логический ключ 9 дискрет ный интегратор 13 от второго генератора тока разряда 7, а счетчик времени разряда 3 от генератора меток времени 1. Конечное значение времени разряда фиксируется на индикаторном табло 17.По окончании каждого зарядно-раз- В рядного цикла схема управления 5 вырабатывает импульс, который через логический ключ 10 поступает на счетчик циклов 22, дешифратор 15 и индикатор 18. 18 случае выхода из строя исследуемого интегратора 13 схема защиты 21 через схему управления 5 и логические ключи 9 и 11 отключает генераторы тока заряда 4 и разряда 6 или 7 и ос танавливает счетчики заряда 2 и разряда 3. При этом индикаторное устройство 18 фиксирует количество наработанных циклов.Устройство работает в трех режимах: "Заряд интегратора", "Разряд Устройство для испытания дискретных интеграторов по авт. св. Ю 822302, о т л и ч а ю щ е е с я тем, что, с целью повышения, точности определе-. ния погрешности зарядно-разрядного цикла, в него введены вторая схема сравнения, вход которой соединен с дискретным интегратором, а выходс одним из входов схемы управления, и второй генератор тока разряда, выход которого соединен с дискретным интегратором, а вход - через логический ключ с одним иэ выходов схемы управления.

СмотретьЗаявка

3263316, 23.03.1981

СЕВАСТОПОЛЬСКОЕ ОТДЕЛЕНИЕ ВСЕСОЮЗНОГО НАУЧНО ИССЛЕДОВАТЕЛЬСКОГО, ПРОЕКТНО-КОНСТРУКТОРСКОГО И ТЕХНОЛОГИЧЕСКОГО ИНСТИТУТА ИСТОЧНИКОВ ТОКА

ШЕПЕЛЕВСКИЙ ЛЕОНИД ЮРЬЕВИЧ, ЯРЫГИН АЛЕКСАНДР СТЕПАНОВИЧ

МПК / Метки

МПК: H01G 9/22

Метки: дискретных, интеграторов, испытания

Опубликовано: 15.10.1982

Код ссылки

<a href="https://patents.su/4-966764-ustrojjstvo-dlya-ispytaniya-diskretnykh-integratorov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для испытания дискретных интеграторов</a>

Предыдущий патент: Устройство для намотки бандажей из ленточного материала

Следующий патент: Способ изготовления секций высоковольтных конденсаторов

Случайный патент: Способ наддува газогенератора для двигателя внутреннего горения