Устройство для контроля параметров логических блоков

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

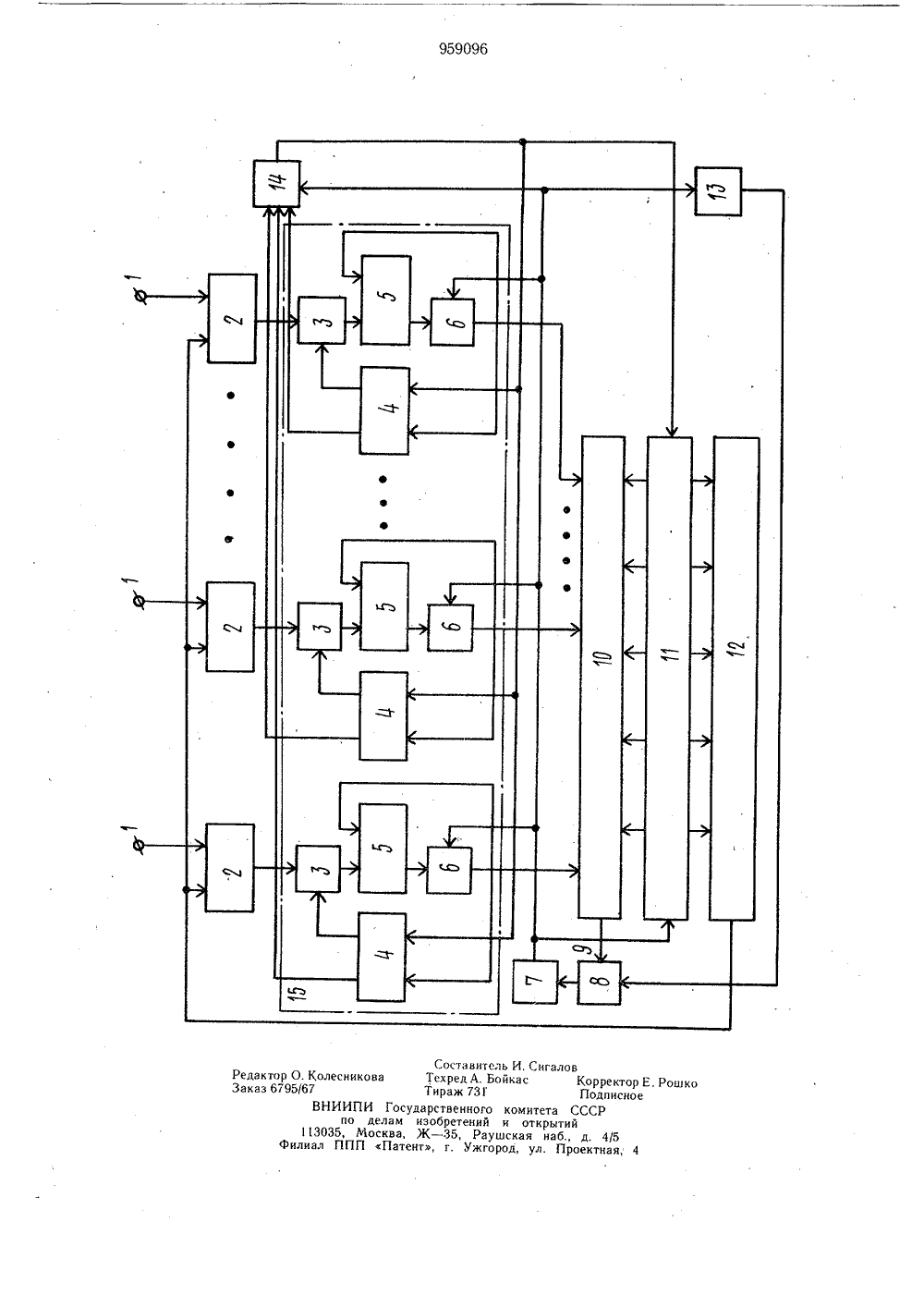

ОП ИСАНИЕИЗЬБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик(51) М, Кл. Сз 06 Г 15/46 Гесударстееккмй кемитет Опубликовано 15.09.82. Бюллетень34Дата опубликования описания 25.09.82пв делам кэобретений и еткрмткй(54) . УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАМЕТРОВИзобретение относится к области вычислительной техники и может найти применение в различных системах контроля и управления, а также в устройствах сопряжения аналоговой аппаратуры с цифровыми системами.Известно устройство автоматического контроля, содержащее коммутатор, формирователь сигналов, блок уставок, логический блок, цифровой преобразователь, кодер адреса. параметров 1.Недостатком данного устройства является низкое быстродействие, обусловленное последовательным обслуживанием цепей параметров, текущие значения которых вышли за пределы допусков.Наиболее близким по технической сущности к данному является устройство для контроля параметров, содержащее блоки сравнения, триггеры, блок приоритета, генератор импульсов, запоминающий блок, счетчик импульсов, цифроаналоговый преобразователь, элемент задержки и элемент ИЛИ. На каждом такте развертки напряжение с выхода цифроаналогового преобразователя (ЦАП) подается на все блоки сравнения одновременно. Если напряжение развертки превосходит по величине напряжения на некоторых шинах устройства, то в соответствующих каналах срабатывают блоки сравнения, после чего через блок приоритета в блок памяти по адресам сработавших каналов последовательно записывается значение кода развертки 2.Недостатком устройства является низкая достоверность контроля, обусловленная тем, что на каждом последующем такте раз вертки выходное напряжение однозначнопревосходит напряжение на входах уже сработавших блоков, поэтому этим каналам приписываются значения напряжений развертки последующих тактов, что не от,вечает действительности. Кроме того, данное устройство не обеспечивает параллельной записи кода напряжения развертки в блок памяти, а также прервание развертки при контроле напряжении всех каналов на первых тактах, что снижает быстродей 2 о ствие устройства.Цель изобретения - повышение быстродействия и точности контроля.Поставленная цель достигается тем, чтов устройство для контроля параметров, содержащее блок памяти, генератор импульсов, счетчик импульсов, цифроаналоговыйпреобразователь, элемент ИЛИ, элемент задержки, многоканальный блок приоритетаи группу схем сравнения, причем информационные входы устройства соединены соответственно с первыми входами схем сравнения группы, выход каждой схемы сравнениягруппы соединен с информационным входомсоответствующего канала многоканальногоблока приоритета, первая группа выходовмногоканального блока приоритета соединена с группой информационных входов блокапамяти, первая и вторая группы информационных выходов счетчика импульсов соединены соответственно с группой адресныхвходов блока памяти и группой входов цифроаналогового преобразователя, выход цифроаналогового преобразователя соединенсо вторыми входами схем сравнения групы, выход элемента задержки соединен спервым-входом элемента ИЛИ, выход которого соединен со входом генератора импульсов, управляющий выход блока памятисоединен со вторым входом элемента ИЛИ,введен в элемент И, причем выход генератора импульсов соединен со счетным входом счетчика импульсов, со входом элемента И, со входом элемента задержки и с 25первым установочным входом многоканального блока приоритета, выход элемента Исоединен с установочным входом счетчикаимпульсов и вторым установочным входоммногоканального блока приоритета, втораягруппа выходов многоканального блока при- Зворитета соединена с группой входов элемента И,Многоканальный блок приоритета содержит в каждом канале первый и второйэлемент И, первый и второй триггер, при 35чем первый, вход первого элемента И каждого канала является информационным входом блока, выход второго элемента И каждого канала соединен с первыми входамипервого и второго триггеров соответствующего канала и является выходом группы вы оходов блока приоритета, выход первого элемента И каждого канала соединен со вторым входом второго триггера соответствующего канала, выход которого соединен спервым входом второго элемента И соответ45ствующего канала, второй вход второгоэлемента И является первым установочнымвходом блока, второй установочный входблока соединен со вторыми входами вторых триггеров всех каналов, первый выход первого триггера каждого канала со оединен со вторым входом первого элемента И соответствующего канала, вторые выходы первого триггера каждого канала образуют вторую группу выходов многоканального блока приоритета.На чертеже приведена функциональнаясхема устройства для контроля параметров.Схема устройства включает входы 1,контролируемых параметров, группу схем сравнения 2, первый элемент И 3, первый триггер 4, второй триггер 5, второй элемент И 6, генератор 7 импульсов, элемент ИЛИ 8, управляющий выход блока памяти 9, блок 10 памяти, счетчик 11 импульсов, ЦАП 12, элемент 13 задержки, элемент И 14 и многоканальный блок 15 приоритета. Каждый канал многоканального блока 15 приоритета содержит в каждом канале первый и второй элементы И 3 и 6 и триггеры 5.Устройство работает следующим образом.В исходном состоянии счетчик импульсов1 и триггеры 4 и 5 установлены в 0, элементы И 3 открыты, а элементы И 6 и элемент И 14 закрыты, на входы 1 поданы контролируемые параметры.Запуск многоканального измерителя производится через блок 1 О памяти, Запускаю.ций импульс появляется на его выходе 9 и через элемент ИЛИ 8 возбуждает генератор 7 импульсов, Выходной импульс последнего поступает на входы элемента задержки 13 и счетчика импульсов 11, изменяя на единицу его цифровое значение, в результате чего с выхода ЦАП 12 на входы схем сравнения. 2 подается напряжение первого такта развертки.Если это напряжение превосходит по величине напряжения на некоторых входах 1, то в соответствующих каналах срабатывают схемы сравнения и через элементы И 3 устанавливают триггера 5 этих каналов в единичное состояние, открывая соответствующие элементы И 6, в противном случае многоканальный блок приоритета 15 остается в исходном состоянии.Импульс, поступивший на вход элемента задержки 13, задерживается последним на время переходных процессов в схеме сравнения 2 и многоканальном блоке 15 приоритета, после чего через элемент ИЛИ 8 вновь возбуждает генератор импульсов 7.Импульс с выхода последнего поступает снова на вход элемента задержки 13 и счетчика импульсов 11, одновременно через открытые элементы И 6 производя запись информации со счетчика импульсов 11 в ячейки памяти блока 10, соответствующие номерам сработавших каналов. Этим же сигналом триггеры 4 и 5 сработавших каналов перебрасываются соответственно в единичное и нулевое состояние, блокируя эти каналы до конца развертки и открывая по соответствующим входам элемент И 14. На входы схем сравнения 2 подается новое напряжение и следует очередной такт развертки. После нескольких тактов все каналы устройства окажутся заблокированными, что означает, что все поданные на входы 1 параметры замерены, поэтому очередной импульс с выхода элемента задержки 13, возбудив генератор импульсов 7, установит через открывшийся элемент И 14 счетчик импульсов 11 и триггеры 4 многоканального блока приоритета 15 в нулевое состояние. Устройство будет подготовлено к очередному циклу работы.Таким образом, в предлагаемом устройстве исключается искажение информации за счет приписывания ряду каналов значений напряжений развертки последующих тактов, что повышает достоверность измерений, а также обеспечивается параллельная запись информации в блок памяти о всех сработавших на данном такте каналах и прерывание цикла развертки при измерении всех поданных на вход устройства напряжений, что повышает быстродействие устройства.Формула изобретения1. Устройство для контроля параметров логических блоков, содержащее блок памяти, генератор импульсов, счетчик импульсов, цифроаналоговый преобразователь, элемент ИЛИ, элемент задержки, многоканальный блок приоритета и группу схем сравнения, причем информационные входы устройства соединены соответственно с первыми входами схем сравнения группы, выход каждой схемы сравнения группы соединен с информационным входом соответствующего канала многоканального блока приоритета, первая группа выходов многоканального блока приоритета соединена с группой информационнь 1 х входов блока памяти, первая и вторая группы информационных выходов счетчика импульсов соединены соответственно с группой адресных входов блока памяти и группой входов цифроаналогового преобразователя, выход цифроаналогового преобразователя соединен со вторыми входами схем сравнения группы, выход элемента задержки соединен с первым входом элемента ИЛИ, выход которого соединен со входом генератора импульсов, управляющий выход блока памяти соединен со вторым входом элемента ИЛИ, отличаюи 4 ееся тем, что, с целью повышения быстродействия и точности контроля, в устройствовведен элемент И, причем выход генератораимпульсов соединен со счетным входом счет 5 чика импульсов, со входом элемента И, свходом элемента задержки и с первым установочным входом многоканального блокаприоритета, выход элемента И соединен сустановочным входом счетчика импульсов,и вторым установочным входом многоканального блока приоритета, вторая группа выходов многоканального блока приоритета соединена с группой входов элемента И.2, Устройство по п. 1, отличиюи 1 еесятем, что многоканальный блок приоритета5содержит в каждом канале первый и второйэлемент И, первый и второй триггер, причем первый вход первого элемента И каждого канала является информационным входом блока, выход второго элемента И каждого канала соединен с первыми входамипервого и второго триггеров соответствующего канала и является выходом группывыходов блока приоритета, выход первогоэлемента И каждого канала соединен совторым входом второго триггера соответст 25 вующего канала, выход которого соединенс первым входом второго элемента И соответствующего канала, второй вход второгоэлемента И является первым установочнымвходом блока, второй установочный входблока соединен со вторыми входами вторых3 п триггеров всех каналов, первый вход первого триггера каждого канала соединен совторым входом первого элемента И соответствующего канала, вторые выходы первоготриггера каждого канала образуют вторуюгруппу выходов блока приоритета.35 Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССР489115, кл. 6 06 Г 5/46, 1976.2. Авторское свидетельство СССР485458, кл. 6 06 Г 15(46, 976.едактор О. Колаказ 6795/6ВН ИПИ Госпо деламМосква,ППП Пате Составите Техред А. БТираж 73 Г дарственногоизобретенийЖ - 35, Рау нт, г. Ужго ь И. Сигаловйкас Корре ктоПодписнокомитета СССРи открытийшская наб., д. 4/5од, ул. Проектная,

СмотретьЗаявка

3243205, 02.02.1981

ВОЙСКОВАЯ ЧАСТЬ 60130

ФРОЛОВ ВЛАДИМИР ПЕТРОВИЧ, МАКСИМОВ ЮРИЙ АЛЕКСАНДРОВИЧ, МОХНОБРОВ НИКОЛАЙ ВАСИЛЬЕВИЧ, БЕЛОВА ТАТЬЯНА ОЛЕГОВНА

МПК / Метки

МПК: G06F 11/28

Метки: блоков, логических, параметров

Опубликовано: 15.09.1982

Код ссылки

<a href="https://patents.su/4-959096-ustrojjstvo-dlya-kontrolya-parametrov-logicheskikh-blokov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для контроля параметров логических блоков</a>

Предыдущий патент: Система автоматического управления загрузкой бункеров

Следующий патент: Устройство для моделирования колебаний гусеничных машин

Случайный патент: Способ теплового зондирования скважин