Микропроцессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

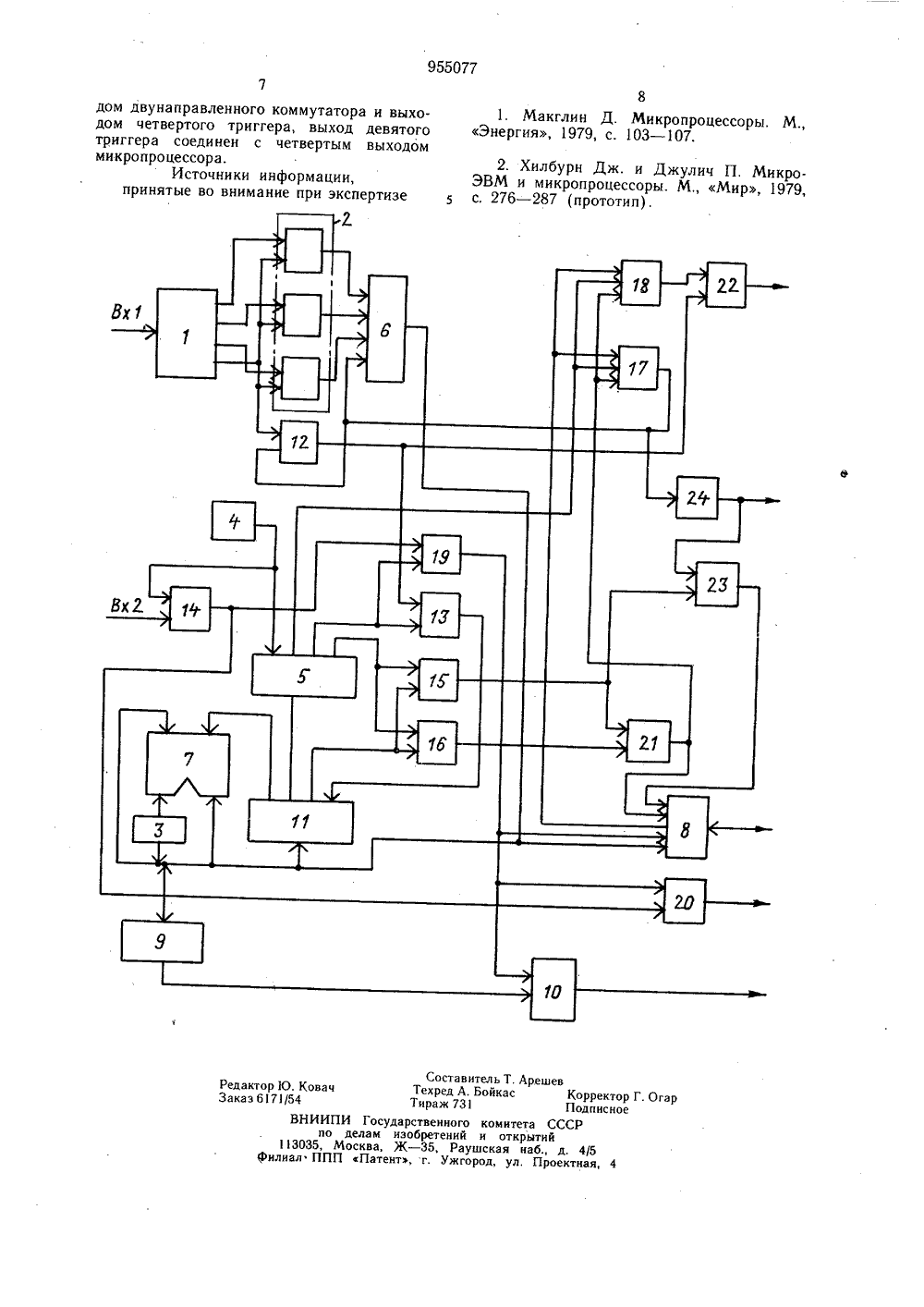

,1955077 Оп ИСАНИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик(51) М. Кл.з б 06 Г 5/00 Гоеударетвеииый комитет СССР Опубликовано 30.08.82. Бюллетень32Дата опубликования описания 30.08.82ив делам иэобретеиий и открытий(71) Заявит 54 РОПРОЦЕСС 1Изобретение относится к вычислительной технике, в частности к малым цифровым вычислительным устройствам, в том числе и к многопроцессорным, предназначенным для работы в системе управления технологическими процессами, системах сбора и обработки информации и в системах измерения параметров объекта.Известен микропроцессор, содержаший приоритетный блок, блок регистров общего назначения, регистры и триггеры 11.Недостатком известного устройства является наличие специальной шины Запрос принят, которая является частью системной магистрали и используется только в процессе обработки прерывания. При многопроцессорной системе число таких шии увеличивается пропорционально числу процессоров. Это приводит к снижению эффективности использования оборудования за счет перенесения части функций на шины нестандартных соединений.Наиболее близким к предлагаемому по технической сушности является микропроцессор, содержащий арифметико-логический блок, блок регистров общего назначения, коммутатор, двунаправленный коммутатор,буферныи регистр, генератор, дешифраткоманд, триггеры и регистры 12. Недостатком известного микропроцессора является наличие дополнительных цепей Б внешних соединений, которые должны бытьподведены к любым модулям, в частности интерфейсам, которые используют код команды Рестарт для сброса триггеров прерывания. В многопроцессорных системах введение таких нестандартных соединений приводит к значительному усложнению внешних соединений особенно в тех случаях, когда внешние устройства, подключенные к обшей магистрали, используются несколькими процессорами коллективно. В таких 15 случаях в целях уменьшения цепей внешнихсоединений используют программный сброс триггеров прерывания, что также приводит к уменьшению эффективности использования оборудования. Кроме того, в указанном могодуле имеется аппаратно сложная структура и сложный алгоритм реализации процесса передачи системной магистрали в многопроцессорных системах.Цель изобретения - упрошение и повышение эффективности микропроцессора.3Поставленная цель достигается тем, что в микропроцессор, содержащий приоритетный блок, вход которого соединен с первым входом микропроцессора, группа выходов приоритетного блока соединена с группой входов регистра, выходы которого соединены с группой входов коммутатора, выход которого соединен с первыми входами двунаправленного коммутатора, дешифратора команд и арифметико-логического блока, соединенного двусторонними связями с буферным регистром и блоком регистров общего назначения, выход которого соединен с первым входом регистра адреса, выход приоритетного блока соединен со входом регистра и первым входом первого триггера, выход которого соединен с первым входом второго триггера, выход которого соединен со вторым входом дешифратора команд, первый выход кОторого соединен со вторым входом арифметико-логического блока, генератор, выход которого соединен с первыми входами блока синхронизации и третьего триггера, второй вход которого соединен со вторым входом микропроцессора, второй выход дешифратора команд соединен с первыми входами четвертого и пятого триггеров, выходы которых через элемент ИЛИ соединены с первыми входами шестого и седьмого триггеров и со вторым входом двунаправленного коммутатора, третий выход дешифратора команд соединен со вторым входом блока синхронизации, первый выход которого соединен со вторыми входами четвертого и пятого триггеров, второй выход блока информации соединен со вторыми входами шестого и седьмого триггеров, третьи входы которых соединены с выходом двунаправленного коммутатора, третий выход блока синхронизации соединен со вторым входом второго триггера, выход регистра адреса соединен с первым выходом микропроцессора, выход регистра адреса соединен с первым выходом микропроцессора, двунаправленный коммутатор соединен двусторонней связью с шиной данных, выход шестого триггера соединен со вторым входом первого триггера и входом коммутатора, введены два триггера, два элемента И, элемент НЕ, причем выход третьего триггера соединен с первыми входами восьмого и девятого триггеров, выход восьмого триггера соединен со вторыми входами регистра адреса,девятого триггера и с третьим входом двунаправленного коммутатора, выходы первого и седьмого триггеров через первый элемент И соединены со вторым выходом микропроцессора, выход шестого триггера через элемент НЕ соединен с третьим выходом микропроцессора и первым входом второго элемента И, выход и второй, вход которого соединены соответственно с четвертым входом двунаправленного коммутатора и выходом четвертого триггера, выход девятого51 О15 триггера соединен с четвертым выходом микропроцессора.На чертеже приведена блок-схема микропроцессораМикропроцессор содержит приоритетный блок 1, регистр 2, буферный регистр 3, генератор 4, блок 5 синхронизации, коммутатор 6, арифметико-логический блок 7, двунаправленный коммутатор 8, блок 9 регистров общего назначения, регистр 10 адреса, дешифратор 11 команд, триггеры 12 - 20, элемент ИЛИ 21, элементы И 22 - 23 и элемент НЕ 24.После приема приоритетным блоком 1 запроса на прерывание на его выходах появляется закодированный в двоичном коде уровень, который фиксируется в регистре 2. Одновременно приоритетный блок 1 выдает сигнал возникновения внешнего прерывния и переводит триггер 12 в активное состояние. Далее сигнал поступает на триггер 13 и переводит его в активное состояние. В результате на его выходе возникает сигнал Прерывание разрешено, который поступает на дешифратор 11. Одновременно сигнал от триггера 12 через элемент И 22 поступает на шину запроса системной магистрали.25 Следовательно, другой микропроцессор,который в настоящий момент пользуется системной магистралью, воспринимает этот сигнал, завершает вычислительный процесс и выдает сообщение о том, что системная магистраль освобождена. Это сообщение микропроцессора поступает на триггер 14, синхронизируется с тактовыми импульсами генератора 4 и передается на триггер 19.После поступления разрешающего сигнала от блока 5 триггер 19 вырабатывает сигнал подтверждения захвата, который активизирует коммутатор 8, регистр 10 и через триггер 20, тактированный от генератора 4, поступает на шину системной магистрали. Этот сигнал информирует другие микропроцессоры о том, что магистраль занята. После 40 этого микропроцессор, полностью активизированный, приступает к обработке внешнего прерывания.В первом машинном такте, который определяется блоком 5, на выходе арифметикологического блока 7 выставляется слово- состояние, формат которого носит информацию о том, что микропроцессор перешел в режим обработки прерывания. Совокупность битов слово-состояния и синхроимпульса устанавливает триггеры 17 и 18 в актив ное состояние. После завершения первогомашинного такта микропроцессор переходит на второй машинный такт, в котором происходит чтение команды Рестарт, определяющий условный переход на начало обработки программы прерывания соответст вующего уровня, по которому был принятзапрос, Сигнал от триггера 7 поступает на, триггер 12 и коммутатор 6. В результате5триггер 12 возвращается в исходное состояние, а через коммутатор 6 на дешифратор 11 поступает код уровня текушего прерывания - команда Рестарт. Одновременно сигнал с триггера 17 через элемент НЕ 24 поступает на элемент И 23 и как строб Прерывания на соответствующий выход микропроцессора,После фиксации слова-состояния в триггерах 17 и 18 во втором машинном такте активизируется триггер 5. На его выходе появляется строб Чтение, который через элемент ИЛИ 21 поступает на коммутатор 8 и активизирует его. Одновременно строб Чтение поступает и на элемент И 23. В режиме чтения из памяти или чтения порта внешнего устройства коммутатор 8 устанавливается в направлении, при котором поток данных направлен в сторону микропроцессора, т. е. микропроцессор читает шины данных. Но в режиме Чтение команды Рестарт совокупность сигналов стробирования, прерывания и чтение на входах элемента И 23 образуют на его выходе сигнал, который устанавливает направление потока данных в обратную сторону, в результате чего команда Рестарт через коммутатор 8 поступает в системную магистраль. В дальнейшем процессе эта команда в сопровождении строба Прерывание воспринимается портом внешнего устройства, выставившим прерывание, и используется согласно алгоритма его функционирования. Сигнал запроса на пользование системной магистрали поддерживается до окончания обработки программы определенного уровня прерывания. Это достигается тем, что сигнал на триггере 18 блокирует сигнал от триггера 12 вне зависимости от его состояния до конца обработки подпрограммы прерывания и снимается только после того, как микропроцессор в ходе обработки программы встречает команду останова вычислительного процесса. При этом микропроцессор выставляет слово-состояние Останов, которое сбрасывает триггеры 17 и 18. Сигнал от триггера 18 через элемент И 22 и поступает в системную магистраль и сообщает другим процессорам о том, что активный микропроцессор освобождает магистраль.Полное отключение от магистрали происходит только тогда, когда снимается внешний сигнал йриоритета. Вследствие этого триггер 14 сбрасыцается и сбрасывает триггер 19.Следовательно, коммутатор 8 и регистр 10 отключаются от системной магистрали и с триггера 20 подается сигнал Магистраль освобождена.При использовании предлагаемого процессора возрастает эффективность использования оборудования на 30 - 50 О/О, уменьшается число цепей внешних соединений 5 10 15 20 25 Зо 35 40 45 50 55 6на 7 - 15 О/О и появляется возможность унификации узлов микропроцессора.формула изобретенияМикропроцессор, содержащий приоритетный блок, вход которого соединен с первым входом микропроцессора, группа выходов приоритетного блока соединена с группой входов регистра, выходы которого соединены с группой входов коммутатора, выход которого соединен с первыми входами двунаправленного коммутатора, дешифратора команд и арифметико-логического блока, соединенного двусторонними связями с буферным регистром и блоком регистров общего назначения, выход которого соединен с первым входом регистра адреса, выход приоритетного блока соединен со входом регистра и первым входом первого. триггера, выход которого соединен с первым входом второго триггера, выход которого соединен со вторым входом дешифратора команд, первый выход которого соединен со вторым входом арифметико-логического блока, генератор, выход которого соединен с первыми входами блока синхронизации и третьего триггера, второй вход которого соединен со вторым входом микропроцессора, второй выход дешифратора команд соединен с первыми входами четвертого и пятого триггеров, выходы которых через элемент ИЛИ соединены с первыми входами шестого и седьмого триггеров и со вторым входом двунаправленного коммутатора, третий выход дешифратора команд соединен со вторым входом блока синхронизации, первый выход которого соединен со вторыми входами четвертого и пятого триггеров, второй выход блока информации соединен со вторыми входами шестого и седьмого триггеров, третьи входы которых соединены с выходом двунаправленного коммутатора, третий выход блока синхронизации соединен со вторым входом второго триггера, выход регистра адреса соединен с первым выходом микропроцессора, двунаправленный коммутатор соединен двусторонней связью с шиной данных, выход шестого триггера соединен со вторым входом первого триггера и входом коммутатора, отличающийся тем, что, с целью упрощения и повышения эффективности, в него введены два триггера, два элемента И, элемент НЕ, причем выход третьего триггера соединен с первыми входами восьмого и девятого триггеров, выход восьмого триггера соединен со вторыми входами регистра адреса, девятого триггера и с третьим входом двунаправленного коммутатора, выходы первого и седьмого триггеров через первый элемент И соединены со вторым выходом микропроцессора, выход шестого триггера через элемент НЕ соединен с третьим выходом микропроцессора и первым входом второго элемента И, выход и второй вход которого соединены соответственно с четвертым вхо955077 Составитель Т.Техред А. БойкасТираж 731 еше Редактор Ю. КовачЗаказ 6171/54ВНИИ Корректор Г. ОгарПодписноеСР дарственного комит изобретений и отк Ж - 35, Раушская нт, г. Ужгород, ул та рыти наб д. 4/ ктна дом двунаправленного коммутатора и выходом четвертого триггера, выход девятого триггера соединен с четвертым выходом микропроцессора.Источники информации,принятые во внимание при экспертизе ПИ Гос по делам 113035, Москва Филиал ППП Пат

СмотретьЗаявка

2918451, 20.05.1980

РИЖСКОЕ ПРОИЗВОДСТВЕННОЕ ОБЪЕДИНЕНИЕ "ВЭФ" ИМ. В. И. ЛЕНИНА

ВЕНТИНЬШ ЯНИС ЯНОВИЧ, ВИДЕНИЕКС ПЕТЕРИС ОСКАРОВИЧ, БУСЛОВИЧ СОЛОМОН ЛЕЙБОВИЧ, СКОРИНКО СЕРГЕЙ ЕВГЕНЬЕВИЧ

МПК / Метки

Метки: микропроцессор

Опубликовано: 30.08.1982

Код ссылки

<a href="https://patents.su/4-955077-mikroprocessor.html" target="_blank" rel="follow" title="База патентов СССР">Микропроцессор</a>

Предыдущий патент: Устройство для управления виртуальной памятью

Следующий патент: Ассоциативный параллельный процессор

Случайный патент: Транспортное средство