Устройство для испытаний дискретных электрохимических интеграторов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

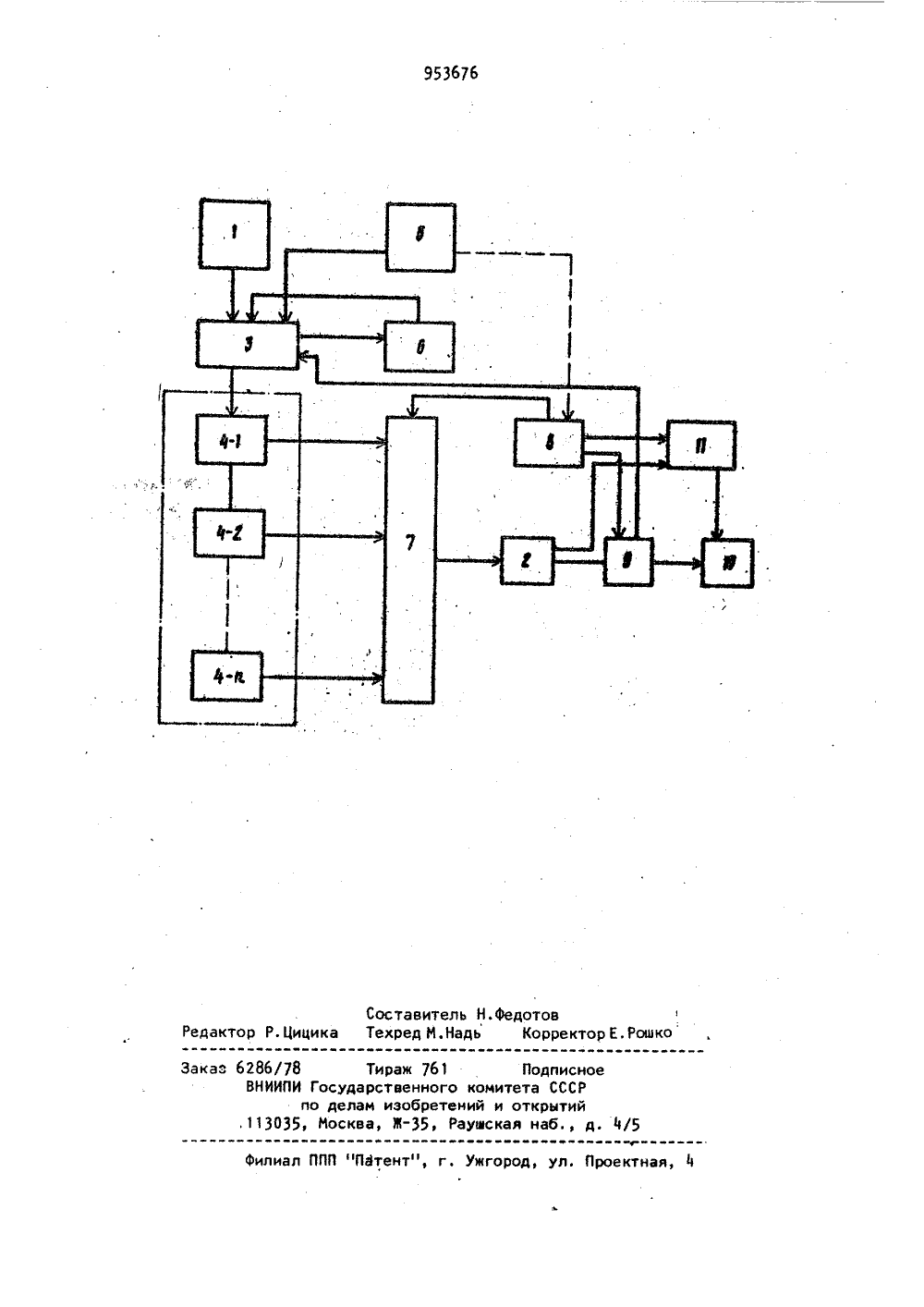

(21) 299021 ием заявк присоелине 3) Прнорит ударстаеииый комитет СССР 82 Бюллетень ме 31 описания 23.08.82 публиковано 23Дата опублнковани елаи иаооретеииии открытий 3) УДК 6213162) Авторы изобретения ТМТЯм ов Котляр, В. Степанов и Л. М.. .ННЧНСь.ьМЬЪЯТЯМИ.ни научноа Краснодарское отделение с опытным производ Всесоюзного ордена Трудового Красного Знам исследовательского института источников то) УСТРОЙСТВО ДЛЯ ИСПЫТАНИЙ ДИСКРЕТНЫХ ЭЛЕКТРОХИМИЧЕСКИХ ИНТЕГРАТОРОВтелем, под выход .деши Одновремен ток заряда тоцника. Процесс заряддаце операторомкоманды "Пуск".ма управления коключает испытываисточнику токаОдновременно ссхемы управления начинается при по" схему управления о этой команде схе тактами релеподмый интегратор к и схеме сравнения, этим сигнал со разрешает прохож 1Изобретение относится к информационно-измерительной технике и представляет собой автоматизированнуюизмерительную систему, предназначенную для испытаний большой партииэлектрохимицеских интеграторов одновременно.Известно устройство для определения параметров и испытаний электрохимических интеграторов, включающеестабилизированный источник тока,генератор стабилизированной частоты,управляющий элемент, задатцик длительности импульса, синхронизатор,задающий мультивибратор, счетчик15числа импульсов, блок отсчета иуправления, Устройство является универсальным и предназначено для контроля параметров интеграторов как призарядных, так и при разрядных .ис"пытаниях 13.Однако оно рассчитано на испытания одновременно нескольких инте"граторов. Наиболее близким к изобретению является устройство, содержащее источник тока, схему сравнения, схему управления, генератор метоК времени, устройство для измерения временного интервала. Для занесения в интегратор определенного количества электричества при зарядных испы" таниях оператор задает необходимое в этом. случае время заряда переключаключающим соответствующийФратора к схеме управления,но выбирается необходимыйстабилизированного ис953676 50 55 дение импульсовгенератора меток времени на устройство измерения временного интервала, которое состоит из двоично-десятичного счетчика, двоично-десятичного дешифратора и цифрового десятичного табло. По мере заполнения счетчика на табло индищруется время заряда. По окончании необходимого временного интервала заряда положительный уровень с дешифратора, служащий для поджигания катодов первых цифровых индикаторных ламп, поступает на схему управления, которая отключает интегратор от зарядной цепи и прекращает прохождение импульсов счета с генератора меток времени на устройство измерения временного интервала, Одновременно с заполнением воеменного устройства импульсами с генератора меток времени схема сравнения осуществляет допусковый контроль напряжения на интеграторе и при превышении им определенного уровня, что свидетельствует о неисправности интегратора, формирует сигнал на схемууправления, прекращающую процесс заряда 2 3Однако известное устройство не рассчитано на испытание нескольких интеграторов одновременно, и ртобы повысить его производительность, пришлось бы в соответствующее число раз увеличить количество источников тока и схем сравнения, что привело бы к резкому увеличению веса, габаритов и потребляемой мощности установки. Цель изобретения - повышение производительности.Указанная цель достигается тем, что в устройство, содержащее источник тока и интегратор меток времени, подключенные к входу схемы управления, выход которой соединен с входом блока измерения временного интервала, схему сравнения, введены коммутатор, оперативное запоминающее устройство, схема совпадения, схема сигнализации и распределитель, причем выходы распределителя связаны с адресными вхо)ами оперативного запоминающего устройства, первым входом схемы совпадения и входами управления ком мутатора, информационные входы которого подключены к испытываемым интеграторам, а выход " к входу схемы сравнения, выход которой связан с 5 0 20 25 30 35 40 45 входом "Запись" оперативного запоминающего устройства и вторым входом схемы совпадения, а выход схемы совпадения вместе с выходом оперативного запоминающего устройства подключен к схеме сигнализации.На чертеже показана структурная схема устройства.. Схема содержит источник 1 тока интегрирования, схему сравнения 2, схему управления 3, интеграторы 4-1-4=п,генератор 5 меток времени,.формирователь 6 временных интервалов, коммутатор распределитель 8, оперативное запоминающее устройство ОЗУ) 9, схему 1 О сигнализации совпадения.Процесс испытаний интеграторов начинается по команде оператора и состоит в следующем, Съема управления 3 включает интеграторы в цепь источника 1 тока интегрирования и разрешает прохождение меток времени на формирователь б временных интервалов. Он в свою очередь осуществляет подсчет этих меток и сравнение текущего значения временного интервала и заданного значения этого интервала, Одновременно метки времени запускают рас" пределитель 8, на выходах которого появляется сдвинутая во времени последовательность импульсов, В соответствии с сигналами распределителя 8 коммутатор 7 начинает поочередно подключать к входу схемы сравнения заряжаемые интеграторы, Схема сравнения 2 осуществляет контроль напряжения на интеграторе по двум уровням. При достижении напряжения на каком-либо интеграторе первого контролируемого уровня сигнал со схемы сравнения 2 поступает на вход схемысовпадения 11, которая осуществляет временное разделение этого сигнала в соответствии с сигналами распределителя 8. После этого схема совпадения 11 своими выходными сигналами включает сигнализацию о номере интегратора, напряжение на котором вышло за первый контролируемый уровень. При превышении напряже" нием на интеграторе второго контролируемого уровня сигнал со схемысравнения 2 поступает на шину "Записьн ОЗУ 9 и записывается в ячейку,на входе которой присутствует тактовый импульс с распределителя. ОЗУ 9в свою очередь своими выходными сигналами включает световую сигнализацию о выходе напряжения на этом инте3676 5 95 граторе за второй контролируемый уровень и одновременно Формирует сигнал на схему управления 3, по которому данный интегратор выводится из зарядной цепи.Таким образом, введение в установку коммутатора, ОЗУ и схемы совпадения, управляемых распределителем, позволило резко повысить производительность зарядных испытаний одной установкой и сократить число схем сравнения и высокостабильных источников тока при использовании известной установки. тельности, в нее введены коммутатор, оперативное запоминающее устройство, схема совпадения, схема сигнализации и распределитель, причем выходы распределителя связаны с адресными ми входами оперативного запоминающего устройства, первым входом схемы совпадений и входами управления коммутатора инФормационные входы 1 О которого подключены к испытываемыминтеграторам, а выход - к входу схемы сравнения, выход которой связан С входом "Запись" оперативного запоминающего устройства и вторым входомсхемы совпадения,а выход схемы совпадения вместе с выходом оперативно-.го запоминающего устройства подключен к схеме сигнализации. 1. Приборы и системы управления.- "Машиностроение"1968 , Ъ 11, с,55., 25 . 2. Авторское свидетельство ЩРИ 555153, кл, Н 01 С 9/22, 1976 (прототип). Формула изобретения Устройство для испытаний дискретных электрохимических интеграторов, содержащее источник тока и генератор меток времени, подключенные к входу схемы управления; выход которой соединен с входом блока измерения временного интервала, схему сравне.- ния, о т л и ч а ю щ е е с я тем, что, с целью повышения производи 20 Источники инФормации, принятые,во внимание при экспертизеСоставитель Н.Федотовдактор Р. Цицика Техред И.Надь Корректор Е.Рашко 1303 цеа г илиал ППП "Патен г. У род, ул. Проек акав 6286/78ВНИИПИ Тираж 761сударственного коделаи изобретенийосква, В, Рауас Подписное итета СССР и открытий кая наб., д.

СмотретьЗаявка

2990211, 09.07.1980

КРАСНОДАРСКОЕ ОТДЕЛЕНИЕ С ОПЫТНЫМ ПРОИЗВОДСТВОМ ВСЕСОЮЗНОГО ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ НАУЧНО-ИССЛЕДОВАТЕЛЬСКОГО ИНСТИТУТА ИСТОЧНИКОВ ТОКА

КОТЛЯР ЯКОВ АРОНОВИЧ, СТЕПАНОВ ВЛАДИМИР ГРИГОРЬЕВИЧ, СМИРНОВ ЛЕВ МИХАЙЛОВИЧ

МПК / Метки

МПК: H01G 9/22

Метки: дискретных, интеграторов, испытаний, электрохимических

Опубликовано: 23.08.1982

Код ссылки

<a href="https://patents.su/4-953676-ustrojjstvo-dlya-ispytanijj-diskretnykh-ehlektrokhimicheskikh-integratorov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для испытаний дискретных электрохимических интеграторов</a>

Предыдущий патент: Способ изготовления анизотропных постоянных магнитов

Следующий патент: Катодный узел ионного источника

Случайный патент: 401804