Устройство для умножения чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

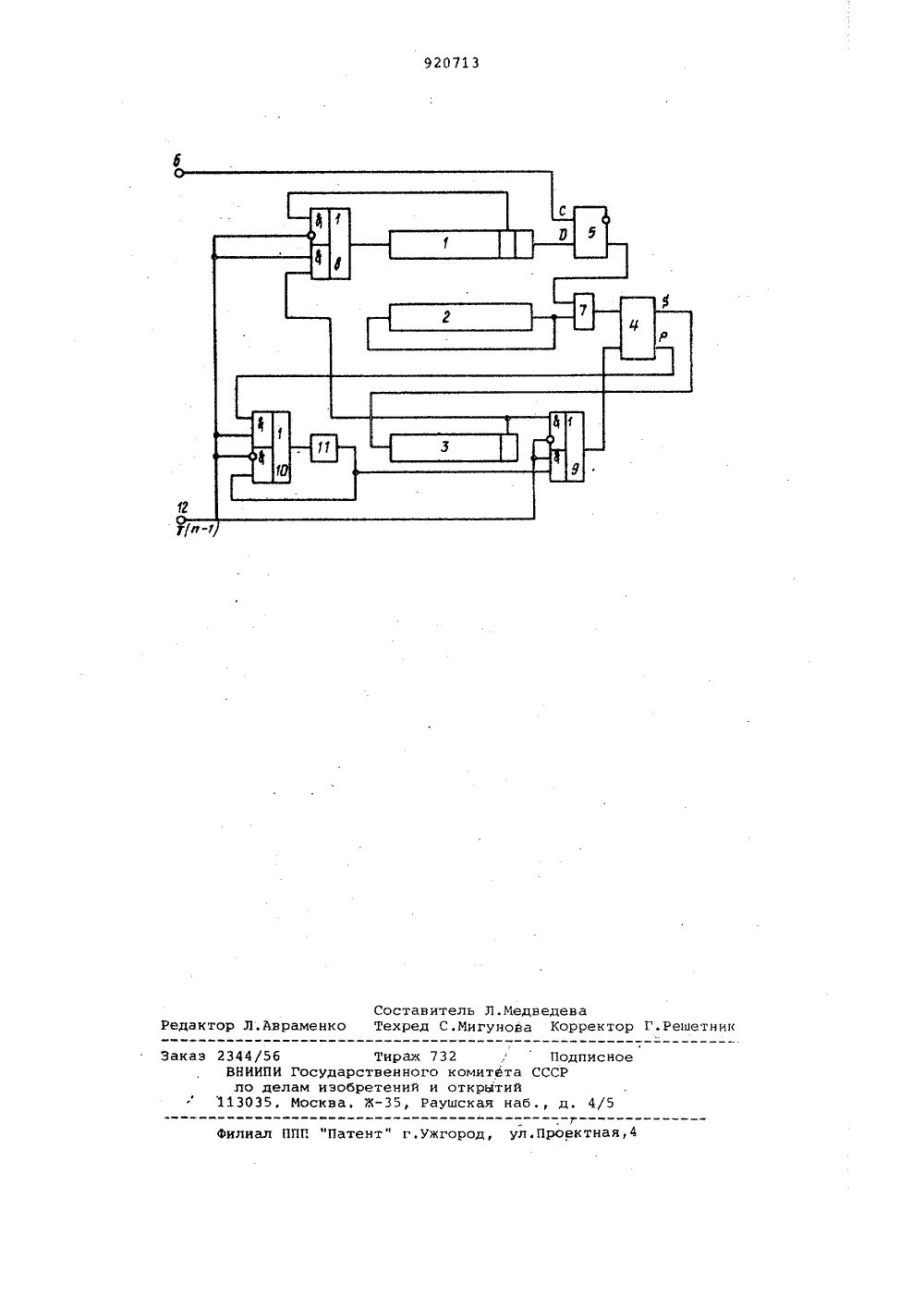

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик(61) Дополнительное к авт. сеид-ву(22) Заявлено 040780 (21) 2950652/18-24 рцм.кл. С 06 Г 7/52 с присоединением заявки йоГосударственный комитет СССР но делам изобретений и открытийДата опубликования описания 150482 В.И.Корнейчук, В.П.Тарасенко, Я.И.Торошанкои Фам Тин НгияКиевский ордена Ленина политехнический институт: .им.50-летия Великой Октябрьской социалистической революции(54) УСТРОЙСТВО ДЛЯ УИНОЖЕНИЯ ЧИСЕЛ Предлагаемое устройство относится к вычислительной технике и может ; быть использовано при построении циф ровых специализированных вычислитель ных машин последовательного действия.Известно устройство для умножения последовательного типа, содержащее регистры множителя, множимого и произведения, одноразрядный сумматор пос ледовательного действия, блок управ" ления,логические элементы И и ИЛИ(,Ц .Принцип работы такого устройства не позволяет в полной мере использовать в нем динамические регистры с большой степенью интеграции, что приводит к росту аппаратурных затрат и габаритов.Наиболее близким по техническому решению к предлагаемому является ус О тройство для умножения чисел последовательного типа, выполненное на динамических регистрах, содержащее дина- , мические регистры множителя, множимого и произведения, одноразрядный сумматор, О-триггер и логический элемент Й-ИЛИ и логический элементИ, причем вход синхронизации Р-триггера соединен с первой такто-вой шиной, информационный вход О-триггера соединен о выходои. первого раз= ряда динамического регистра множителя, выход второго разряда которого соединен с первым входом первого ло" гического элемента И-ИЛИ, выход ко" торого соединен с входом динамичес" кого регистра множителя, выход дина" мического регистра множимого соеди-нен со своим входом, выходом суммы одноразрядного сумматорасоединен со входом динамического регистра произведения (21 .Результат умножения - знак и про" изведение " в таком устройстве формируется через и циклов, разрядность регистров равна л (и ." разрядность операндов, включая один знаковый разряд) .Знак формируется в бтдельном и-м цикле с помощью сумматора, что приводит к усложнению входных схем сум" матора и уменьшению быстродействия,Цель изобретения - повтшение быстродействия устройства.Поставленная цель достигается тем, что в устройство для умножения введены динамический регистр и два логических элемента И-ИЛИ, причем выход 0-триггера соединен с первым входам логического элемента И, второй вход которого соединен с выходомдинамического регистра множимого, а :.выход - с первым входом одноразрядного сумматора, второй вход которого сумматор последовательного действия 4,О-триггер 5, О-вход которого подключен к выходу первого разряда регистра 1, первая тактовая шина б, логический элемент И 7, логические элементы И-ИЛИ 8, 9 и 10, динамический регистр 11, вторая тактовая шина 12.Вход синхронизации О-триггера 5 соединен с первой тактовой шиной б,информационный вход О-триггера 5 сое. - 4 О динен с выходом первого разряда динамического регистра множителя 1,выход второго разряда которого соединен с первым входом логического элемента И-ИЛИ 8, выход которого соединен со входом динамического регистра множителя 1, выход динамического регистра множимого 2 соединен со своим входом, выход суммы одноразрядного сумматора 4 соединен со входомдинамического регистра произведения 3, выход О-триггера 5 соединен с первым входом логического элемента И 7,второй вход которого соединен с выходом динамического регистра множимого 2, а выход . - с первым входомодноразрядного сумматора 4, второй,вход которого соединен с выходом логического элемента И-ИЛИ 9, выходпереноса одноразрядного сумматора 4соединен с первым входом логического элемента И-ИЛИ 10, выход которогосоединен с входом динамического регистра 11 вторые и третьи входы ло 55 бО гических элементов И-ИЛИ 8 и 10, первый и второй входы логического элемен б 5 соединен с выходом второго логического элемента И-ИЛИ, выход переноса одноразрядного сумматора соединен с первым входом третьего логического элемента И-ИЛИ, выход которого соединен с входом динамического регистра, вторые и третьи входы первого и третьего логических элементов ИИЛИ, первый и второй входы второго логического элемента И-ИЛИ объединены и подключены к второй тактовой шине, выход динамического регистра соединен с третьим входом второго логического элемента И-ИЛИ и четвертым входом третьего логического элем нта И-ИЛИ, выход динамического регистра. произведения соединен с чет- вертыми входами первого и второго логических элементов И-ИЛИ, второй вход первого, третий вход третьего и первый вход второго логических элементов И-ИЛИ выполнены инверсньли.На чертеже представлена блок-схема устройства.25Устройство содержит (и)-разрядные регистры множителя 1, множимого2 и 2(и)-разрядный регистр произведения 3, (и) - разрядность мантисс сомножителей 3, одноразрядный ЗО та И-ИЛИ 9 объединены и подключенык второй тактовой шине 12, выход динамического регистра 11 соединен стретьим входом логического элементаИ-ИЛИ 9 и четвертым входом логического элемента И-ИЛИ 10, выход динамического регистра произведения 3соединен с четвертыми входами логических элементов И-ИЛИ 8 и 9, первый,второй, третий входы соответствующихлогических элементов И-ИЛИ 9, 8 и 10выполнены инверсными.Устройство работает следующим образом.Работа устройства осуществляетсяпо циклам, равным циклам циркуляцииинформации в регистрах 1, 2 и 3, длительность которых равна (и) тактов.Считаем,что когда на выходах первого разряда динамических регистров 1и 2 н режиме хранения находятся пер вые разряды записанных в них чисел,на первой тактовой шине б появляется единичный сигнал Т 1, соответствующий началу цикла. Когда на выходахпервого разряда регистров 1 и 2 находятся последние разряды чисел, навторой тактовой шине 12 появляетсЯединичный сигнал Т (и), соответствующий концу цикла. Умножение мантисс двух чисел осуществляется за(и) циклов. Результат умноженияпредставляется 2 (и)-разрядной мантиссой произведения,В исходчом состоянии в регистрах1 и 2 записаны прямые коды мантиссмножителя и множимого младшими разр: - .дами вперед, в регистре 3 - нулевойкод.Рассмотрим работу устройства в(-м цикле. В начале (-го цикла состояние узлов следующее. В регистре1 записан сдвигнутый на (1-1) - разряд впоаво код множителя, в регистре2 - код множимого.В регистрах 11 и 3сформированы (и) старших разрядов,а в (1-1) старших разрядах регистра11 - (1-1) младших разрядов (1-1)-йсуммы частичных произведений. В такте Т 1 на 11-триггер 5 записывается 1-я цифра множителя. Очередная 1-я сумма частичных произведений Формируется следующим образом. На один из входов сумматора4 через элемент И 7, управляемыйтриггером 5, поступает код множимого, умноженный на 1-ю цифру множителя. Цепь циркуляции регистра произведения 3 при умножении замыкаетсячерез сумматор 4 и содержит (и)разряда, что обеспечивает сдвиг вправо старших (и) разрядов (1-1)-йсукины частичных произведений и еесложение с кодом, поступающим на, первый вход сумматора 4, В первых (и)тактах 1-го цикла цепь цижуляции регистра 11 коммутир ется на режимхранения записанного в нем старшегоразряда (1-1)-й суммы частичных произведений, В такте Т (и) его информация выдается на сумматор, а навход регистра 11 поступает значениестаршего разряда (перенос) 1-й суюсь,Старший разряд 1-и суммы частичных 5произведений всегда равен переносу,вырабатываемому при сложения пос)леднего разряда мантиссы множимога сосдвинутой вправо (1-1)-й суммой частичных произведений. Сформированнаятаким образом 1-я сумма частичныхпроизведений записывается в регисто3. Цепь циркуляции регистра 1 коммутируется с выхода его второго разряда, что обеспечивает сдвиг множителяв каждом цикле на один разряд вправо,В такте Т (и) на выходе первого разряда регистра 3 появляется 1.-я цифра 1-й суммы частичных произведений,являющаяся 1-й циФрой младших разрядов произведения. Подача ее на вход 20сумматора блокируется, а в такте Т(и)через элемент И-ИЛИ 8 она записывается в освобождающийся при сдвиге нправо разряд регистра 1,Таким образом., после выполнения 5(и) циклов в регистре 1 Формируется (и) младших, а в регистрах 11 и3 - (и) старших разрядов произведения.В режиме хранения цепи циркуляции 30регистров 11 и 3 объединяются и онирассматриваются как один (и)-разрядный регистр результата.Знак результата в предлагаемомустройстве необходимо формировать 35отдельной схемой, например, с помощью Т-триггера при приеме операндов.По сравнению с известным н данномустройстве для умножения, разрядность 40динамических регистров которого наединицу меньше, получается выигрышв оборудовании, определяемый величиной 1. = ЗИАД где Чр - аппаратурныезатраты на один разряд динамического регистра.При использовании устройства вспециализированных ЦВМ с сокращенным (и)-тактным машинным цикломупрощается блок местного управленияумножением, так как цикл схемы устройства совпадает с машинным цикломСЦВМ. Такой сокращенный машинныйцикл может быть н СЦВМ с диапазономпредставления входных, выходных ипромежуточных переменных, ограничен 55ном только положительными числами.В таких ЦВМ обрабатывать знаки чисел нет необходимости, в памяти хранятся только (и)разрядные мантиссы чисел. бОЦикл работы известного устройствасоставляет и тактов и для работы ввычислительном устройстве с сокраш(енным машинным циклом требуются дополнительные затраты при построении б 5 блока местного управления, а такжеумножение в нем осуществляется заи тактон, В данном устройстве гроизведение Формируется на (и) тактав,Таким образом, время выполненияоперации умножения уменьшается на2 птакт, т.е. быстродействие увеПичявается.Формула изобретенияУстройство для умножения чисел,содержащее динамические регистрымножителя, множимога и произведения,О-триггер, одноразрядный сумматор,логический элемент И-ИЛИ и логический элемент И, причем вход синхронизации 0-триггера соединен с первойтактовой шиной, информационный входО-триггера соединен с выходом первого разряда динамического регистра множителя, выход нтораго разряда которога соединен с первым входом первогологического элемента И-ИЛИ,выход кото"рого соединен с входам динамическогоре"истра множителя, выход динамического регистра мнажимага соединен ссвоим входом, выход суммы одноразрядного сумматора саединсн с входомдинамического регистра произведения,о т л и ч а ю щ е е с я тем, чтос целью повышения быстродействия, внего введены динамический регистр идва логических элемента И-ИЛИ. причем выход О-триггера соединен с первым входом логического элемента И.нтарой вход которого соединен с выходом. динамического регистра множимого,а выход - с перным входом одноразрядного сумматора, второй вход которого соединен с вь;ходом второго логического элемента И-ИЛИ, выход переносаодноразрядного сумматора соединен спервым входом третьего логическогоэлемента И-ИЛИ, ьыход которого соединен с входом динамического регистра, вторые я третья входы первого итретьего логических элементов И-ИЛИ,первый я второй входы второго логичес"кого элемента И-ИЛИ объединены я подключены к второй тактовой шине, выходдинамического регистра соединен стретьим входом второго логическогоэлемента И-ИЛИ и четвертым входомтретьего лагяческага элемента И-ИЛИ,выход динамического регистра произнедения соединен с четвертыми входами первого я второго логических элементов И-ИЛИ, второй нходпервого, третий вход третьего ипервый вход второго логических элементов И-ИЛИ выполнены инверсными.Источники информации,принятые во внимание при экспертизеАвторское снидетельство СССРР 608157, кл,С Сб Г 7/39. 1978,2. Авторское свицетельстно. СССРпо заявке Р 2761786/24-18,кл. 0 06 Г.7/82, 1979 (прототип)920713 Составитель Л.Медведеванко Техред С.Мигуноаа Корректор Г.Решетник Редактор Л.Авр аз илиал ППП "Патент" г,ужгород, ул.Проектная,4 344/56 Тираж 732 ВНИИПИ Государственного ко ло делам иэобретений и от 13035, Москва. 3-35, Раушс Подпистета СССРцтийя наб., д, 4/

СмотретьЗаявка

2950652, 04.07.1980

КИЕВСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. 50-ЛЕТИЯ ВЕЛИКОЙ ОКТЯБРЬСКОЙ СОЦИАЛИСТИЧЕСКОЙ РЕВОЛЮЦИИ

КОРНЕЙЧУК ВИКТОР ИВАНОВИЧ, ТАРАСЕНКО ВЛАДИМИР ПЕТРОВИЧ, ТОРОШАНКО ЯРОСЛАВ ИВАНОВИЧ, ФАМ ТИН НГИЯ

МПК / Метки

МПК: G06F 7/52

Опубликовано: 15.04.1982

Код ссылки

<a href="https://patents.su/4-920713-ustrojjstvo-dlya-umnozheniya-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения чисел</a>

Предыдущий патент: Множительно-делительное устройство

Следующий патент: Устройство для вычисления полиномов второй степени

Случайный патент: Автоматический пробоотборник порошкообразных материалов