Устройство для генерирования сигналов заданной формы

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 886223

Автор: Кренев

Текст

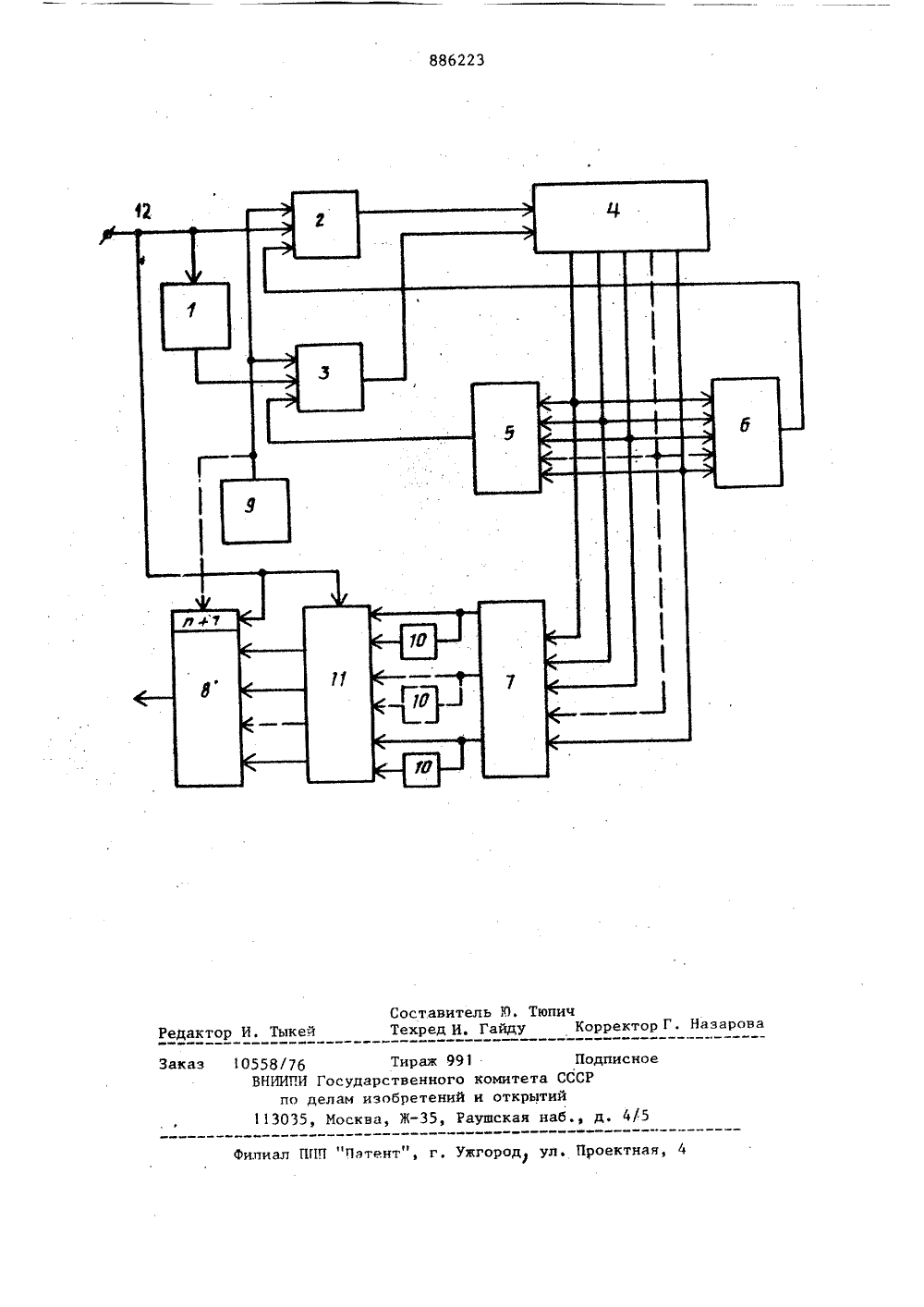

О П И С А Н И Е п)886223ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советск илСоциалистическиеРеспублик(5)М. Кл, Н 03 К 3/64 с присоединением заявки,% -Гасударственный кемнтет СССР но делам нзевретеннй н втерытн 11(72) Автор .изобретения А. Н. Кренев Ярославский государственный университет(7 ) Заявитель 1,54) УСТРОИСТВО ДЛЯ ГЕНЕРИРОВАНИЯ СИГНАЛОВ ЗАДАННОЙ ФОРМЫИзобретение относится к импульсной технике и может быть использовано для получения сложных модулирующих сигналов для систем передачи дискретной информации с ограниченным спектром.Известно устройство, содержащее генератор, импульсов, счетчик, выходы которого соединены со входами бло" ка памяти, выходы которого подключены ко входам цифроаналогового преобразователя, выход которого являет." ся выходом устройства, два элемента И, элемент НЕ, дешифраторы минимальной и максимальной кодовых комби.15 наций, причем генератор импульсов подключен к первым входам первого и второго элементов И, вторые входы которых соединены с выходами дешифраторов максимальной н минимальной кодовых комбинаций соответственно, входы которых подключены к выходам счетчика, входы сложения и вычитания которого подключены к выходам перво" го и второго элементов И соответстф венно, а вход синхронизации устройства соединен с третьим входом пер-вого элемента И и через элемент НЕ с третьим входом второго элемен - та И 13.Однако данное устройство обладает недостаточно широкими функциональными воэможностями, так как не позволяет получить синхронизированные генерированные сигналы, относи тельно симметричные некоторого фиксированного значения напряжения.Цель изобретения - расширение функциональных возможностей путем генерирования сложных синхронизируемых сигналов, симметричных относительно своего среднего значения.Поставленная цель достигается тем, что в устройстве для генерирования сигналов заданной формы, содержащем генератор импулъсов, выход которого соединен с первыми входами первого и второго элементов И, вто86223 10 25 30 35 40 45 50 55 3 8 рые входы которьх соединены друг с; другом через иннертор, а третий вход соединен соответственно с выходами первого и второго дешифраторов, разрядные входы которых соединены между собой и подключены через реверсивный счетчик к выходам элементов И, а через блок памяти ко входам циФроаналогового преобразователя, введены и элементов НЕ и и "канальный дйухразрядный мультиплексор, разрядные выходы которого, кроме последнего, подключены к младшим разрядным входам цифроаналогового преобразователя, а вход управления соединен со входом синхронизации цифроаналогового преобразователя и входом старшего разряда устройства, первые входы и-канального двухразрядно" го мультиплексора соединены с выходами блока памяти непосредственно, а вторые входы соединены с выходами блока памяти через элементы НЕ.На чертеже представлена функциональная схема устройства.Устройство содержит элементНЕ, элементы 2 и 3 И, реверсивный счетчик 4, дешифраторы 5 и 6, блок 7 памяти, цифроаналоговый преобразователь (ЦЛП) 8, генератор 9 импульсов, элементы 10 НЕ, и "канальный двух- разрядный мультиплексор 1, На чертеже также показан вход 2 синхрониФэации, С помощью элементов О НЕ, мультиплексора 11, а также синхронного управления и+1 разрядом цифроаналогового преобразователя 8 и мультиплексора 11, достигается формиронание синхронизируемых симметричных Функций. В случае использования цифроаналогового преобразователя 8 с внутренней буферной памятью, вход синхронизации его соединен с выходом генератора 9 импульсов.Устройство работает следующим образом.На вход 12 синхронизации подается бинарный сигнал, несущий информацию, а с выхода генератора 9 импульсов следуют тактовые импульсы с периодом не больше, чем 1/2 к длительности самого короткого информационного импульса где к - количество разрядов счетчика 4). Если в первый момент времени после включения счетчик 4 находится в промежуточном состоянии (не в экстремальном),то с выходов . дешифраторов 5 и 6 минимальной и максимальной кодовых комбинаций на нхо- -4ды элементов 2 и 3 И воздействуют логические "1 . Допустим, что в момент включения на вход 12 синхронизации .устройства воздействовала логическая 1 В.этЬм случае тактовые1 иимпульсы проходят вход сложения счетчика 4 через элемент 2 И. По мере поступления тактовых импульсон на счетчик 4,на адреснйе входы блока 7 памяти поступает сигнал с соответствующих выходов счетчика 4, который подается также на входы дешифратора 5 и 6 экстремальных кодовых комбинаций. Блок 7 памяти осуществляет функциональное преобразование двоичного кода счетчика 4 н код большей разрядности и, линейно связанный с требуемым значением выходного напряжения устройства в данный момент времени. Кодовые комбинации (слова) с выхода блока 7 памяти подаются через элементы 10 НЕ и днухразрядныйи -канальный мультиплексорна соот.ветствующие входы цифроаналоговогопреобразователя 8. Если на вход управления мультиплексора 1 воздейст".вует логическая "1", то кодовые комбинации через него проходят с первыхнидон всех и разрядов не инвертируясь и подаются на соответствующие входы младших разрядов цифроаналогового преобразователя 8. Если на вход управления мультиплексора 1 воздействует логический "0 то кодовые комбинации на цифроаналоговый преобразователь 8 через мультиплексор 11 проходят со вторых входов иннертиру" ясь элементами 10 НЕ. Воздействие на вход цифроаналогового преобразователя 8 логической "1" (при воздействии на остальные и входов нулевой кодоной комбинации с выходов мультиплексора 1 вызывает появление на его выходе соответствующего напряжения О +, равного 0,5 О ,гдеОцорределяется по формуле:0= О +ВО.и+ф щ 4 Ф При воздействии на входы цифроаналогового преобразователя 8 последонате" льности кодовых комбинаций с выхода мультиплексора 11 на его выходе формируется сигнал О(1), причемь. 1 - -макс(О (После достижения полного заполнения счетчика м, сигнал на-вьходе дешифратора 6 максимальной кодовой комбинации заменяется на логический 1 110 , а на выходе дешифратора 5 мини. мальной кодовой комбинации сохраня. ется логическая "1", н результате886223ьпреобразователя 8 фиксируется заданный уровень напряжения. Это устойчивое состояние устройства сохраняется до замены на входе синхронизации устройства логического "О" налогическую "1", после чего процессформирования сигнала повторится.Таким образом, предлагаемое устройство позволяет формировать слож 1 Е ные синхронизируемые сигналы, симметричные относительно своего среднего значения. 20 Устройство для генерирования сигналов заданной формы по автсв.811237,о т л и ч а ю щ е е с ятем, что, с целью расширения функциональных возможностей, в него вве% дены и элементов НЕ и и-канальныйдвухразрядный мультиплексор, разрядные выходы которого, кроме последнего, подключены к младшим разрядным входам цифроаналогового преобу 11 разователя, а вход управления соединен со входом старшего разряда цифроаналогового преобразователя и входомсинхронизации устройства, первыевходы и-канального двухразрядногомультиплексора соединены с выходамиблока памяти непосредственно, а вторые входы соединены с выходами блокапамяти через элементы НЕ.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРВ 811237, кл. Н 03 К 3/64, 1979. чего оба элемента 2 и ЗИ закрытыи тактовые импульсы на счетчик 4 не поступают На выходе цифроаналогового преобразователя 8 фиксируется заданный таблицей истинности, блока 7 памяти, некоторый уровень напряжения, лежащий в инвервале (О , О б)ьиф Устойчивое состояние схемы сохрайяет ся до замены на входе синхронизации устройства логической "1" иа логичес кий "О". В этом случае элемент 2 И остается в закрытом состоянии, а на втором входе элемента 3 И после ин-. вертирования элементом 1 НЕ логический 0 заменяется на логичес кую "1" и элемент 3 И открывается. Тактовые импульсы, проходя через эле. мент 3 И воздействуют на вход вычитания счетчика 4, Воздействие логического "О" на и+1 разряд цифроаналогового преобразователя 8 вызы вает появление на его выходе минимально возможного напряжения О и (при воздействии на остальные и входов нулевой кодовой комбинации с выходов мультиплексора 11) . При воздействии на вход управления мультиплексора 11 логического "О" информация на его выход подается со вторых входов и, следовательно, инвертируется элементами 1 О НЕ. Инвертированной последовательности кодовых комбинаций соответствует инвертированный сигнал. Таким образом в этом случае сигнал на выходе цифроаналогового преобразователя 8 изменяется в интервале 1,О , 3, ). Формирование сигнала заканчивается при появлении на вы- ходЕ дешифратора 5 минимальной кодовой комбинации логического "О", в результате чего элемент 3 И закрывается и на выходе цифроаналогового Формула изобретения886223 Составитель Ю. ТюпичТехред И. Гайду Корректор Г. Назарова едакто ыкеи Заказ 91 исное та СССытнй илиал ППП "Патент", г. Ужгород ул. Проектная 8/76 Тираж ИИПИ Государственно по делам изобретен 3035, Москва, Ж,о коми йнот Заушск

СмотретьЗаявка

2855473, 11.12.1979

ЯРОСЛАВСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ

КРЕНЕВ АЛЕКСАНДР НИКОЛАЕВИЧ

МПК / Метки

МПК: H03K 3/64

Метки: генерирования, заданной, сигналов, формы

Опубликовано: 30.11.1981

Код ссылки

<a href="https://patents.su/4-886223-ustrojjstvo-dlya-generirovaniya-signalov-zadannojj-formy.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для генерирования сигналов заданной формы</a>

Предыдущий патент: Генератор высоковольтных импульсов

Следующий патент: Генератор пилообразного напряжения

Случайный патент: Способ испытания электрических кабелей на герметичность