Устройство для вычисления функции у =а у -1+в

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

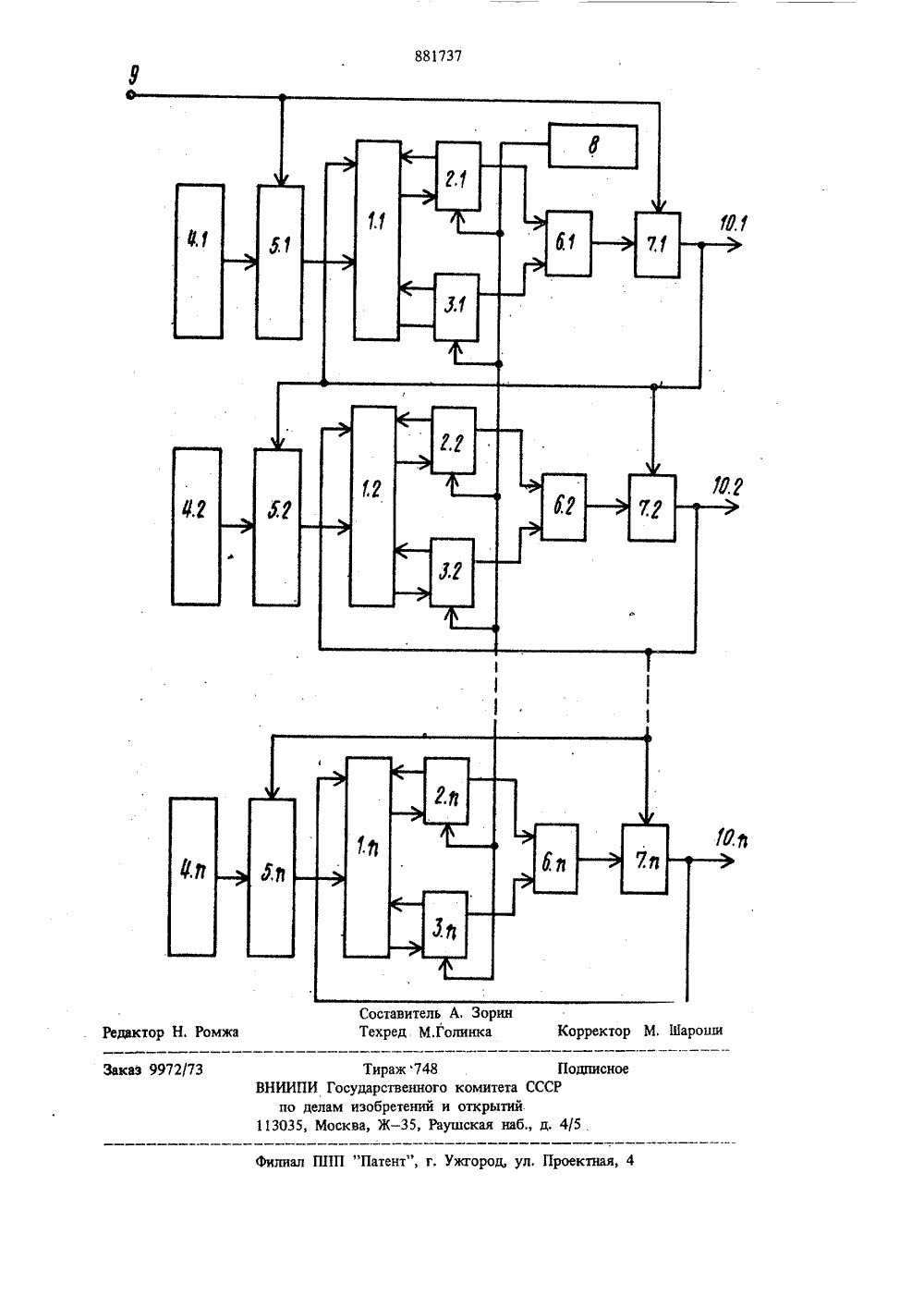

Союз СоветскикСоциалистическихРеспублик ОП ИСАНИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 1188 737ц(5)М. Кл, 6 06 Е 7/544 с присоединением заявки РЙ -Гееудорстакнный комнтет СССР(28) П риоритет но делам нзобретеннй н открытнйДата опубликования описания 15.11.81 72) Авторы изобретен и В. И. Жабин, В. И, Корнейчук, В. С. Козак, Ю. В. КА. С, Покаржевский, А. П. Скочко, В. П, Тарасенко Киевский ордена Ленина политехнич Великой Октябрьской социалисти аявител ский институ ой революции 4) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ У "А 1-1 Изобретени технике и мозированных ци ствах Истигается тем, ч оэф сумма относится к вычислительноиет найти применение в специалн.фровых вычислительных устройзвестно устройство, содержащее регистр аргумента, блоки памяти, умножитель и сум. 5матор 1) .Недостатками устройства являются ни ие функциональные возможности и низкое быстродействие,ч10Наиболее близким по техническои сущности к предлагаемому является устройство, содержащее и сумматоров коэффициентов, связанных со входами и выходами и регистров суммы и выходами и коммутаторов, имеющи цепи выдачи прямого кода, первый регистр коэффициента, соединенный со входами первого коммутатора, блок управления, соедютенный с цепями приема кода на регистр суммы 2120Цель изобретения - повьппение быстродей. тов (и - количество вычисляемых зн чении), и регистров сумм, и коммутаторов, .первый регистр коэффициентов и блок синхронизации, выход которого подключен к управ.ляющим входам регистров сумм, выход пер.вого регистра коэффициентов соединен с пер.вым входом первого коммутатора, выходыкоммутаторов подключены к первым входамсоответствующих сумматоров коэффициентов,вторые входы которых соединены с выходамисоответствующих регистров сумм, первые выходы сумматоров коэффициентов соединенысо входами соответствующих регистров сумм,дополнительно введены и - 1 регистров коэффициентов, и регистров переносов, и выходных сумматоров и и дешифратороь, причемвторой вход первого коммутатора соединенсо входом устройства и с первым входомпервого дешифратора, выходы регистров коэффициентов со второго до и.го соединены спервыми входами соответствующих коммутаторов, управляющие входы регистров переносов соединены с выходом блока синхронизации, вторые входы сумматоров коэффициен.881737 4 соответствии с системой переключательных функций При этомЯ -К тов соединены со входами соответствующихрегистров переносов, выходы которых соеди.иены с третьими входами соответствующихсумматоров коэффициентов, выход .го дешифратора ( - 1, 2, , и-. 1) соединен с четвертым входом .го сумматора коэффициентов,вторым входом (+1).го коммутатора и первым входом (Н 1).го пешифратора, выходп.го дешифратора соединен с четвертым входом и-го сумматора коэффициентов, выходыстарших разрядов регистров сумм и переносовсоединены с первыми и вторыми входамисоответствующих выходных сумматоров, выходы которых соединены с входами соответствующих дешифраторов, выходы которых являются выходами устройства,На чертеже представлена блок-схема устрой.ства,Устройство содержит п сумматоров 1 - 1 Лкоэффициентов, и регистров 21 - 2.и сумм,и регистров 3,1 - Зп переносов, и регистров4,1 - 4,и коэффициентов, и коммутаторов5,1 - 5,п, и выходных сумматоров 6,1 - 6п,и дешифраторов 7,1 - 7. и, блок 8 синхронизации, вход 9 устройства, выходы 10,1 - 10, иустройства, Сумматоры 1 и регистры 2 и 3содержат по (ц+2) разрядов (ц - разрядностькоэффициентов А и В), причем-ый разрядрегистра суммы 2.( - 1, ц+2; первымисчитаются старшие разряды) соединен совходом с.го и с выходом (Й +1)-го разря.дов сумматора 13, а 3-ый разряд регистрапереносов 3,связан со входом 3 -го и выходом (Я +2)-го разрядов сумматора 1. ,Выходы четырех старших разрядов регистра2.и регистра 3, связаны со входами четырехразрядного выходного сумматора с групповым переносом 6, , выходы которого под.ключены ко входам дешифратора 7, . Первый,второй и третий выходы дешифратора 7,подключены к выходу 10, , а также соответственно к цепям выдачи дополнительного,прямого и удвоенного прямого кодов коммутатора 5.(входы первого коммутатора 5подключены ко входной шине 9), а первыйвыход дешифратора 7. , кроме того, соединенсо входами дешифратора 7.+ 1, Четвертыйи пятый выходы дешифратора 7.связанысо входами первого и второго разрядов сумматора 1,соответственно. Выходы ц-разрядного регистра коэффициентов .4,подключеныко входам коммутатора 5,1, выходы которогоподключены ко входам ц младших разрядовсумматора 11. Каждый .й выход блока 8синхронизации связан с цепями приема кодана регистры 2,и 3, ,Дешифратор 7,содержит логические элементы И, ИЛИ, связанные между собой в где иНдексы функций соответствуют размерамвыходов дешифратора 7. , индексы аргументов Я - номерам разрядов сумматора 6Ь - вход дешифратора 7, , связанный с первым выходом- 1-го дешифратора 7,Блок синхронизации 8 содержит и разрядный сдвиговый регистр и и двухвходовыхэлементов И. Выход -го разряда регистра сое20динен с первым входом -го элемента И, выход которого является -м выходом блокасинхронизации, Кроме того, вход первого разряда регистра связан с входом логическойединицы, цепи сдвига регистра соединены стактирующим входом, а тактирующий входсвязан со вторыми входами элементов И,Устройство работает по следующему алгорит.Му:В исходном состоянии30 "о -т ф)6) 1В каждом к-м цикле (К:1,1,0+1)М " : у " ) ,. и-)1к где Ч "Е,0,1 Д- цифра к-го разрядечисла УВ исходном состоянии в соответствии с выражением (2) в каждом регистре суммы2,записано - В .В регистре коэффициентов 4, записан коэффициент А., В регистрах3 переносов записаны нули.В каждом к-м цикле вычисления происходит сдвиг регистра блока синхронизации, ана вход 9 поступает цифра к-го разряда числа 1 О М которая с помощью коммутатора(0)5 Л управляет выдачей в младшие разряды 50 сумматора 1.1 содержимого регистра 4,1 таким образом, что в соответствии с выражением (3) на сумматор 1,1 выдается дополнительный код, если цифра У равна 1, прямойкод, если она равна 1 удвоенный прямой 55 код, если цифра равна 2 и код не выдается,если соответствующая цифра равна нулю, Одновременно с этим выходной сумматор 6,1881737 содержимого четырех старших разрядов регистров суммы 2,1 и переносов 3,1. Анализируя полученную сумматором 6,1 сумму, де. шифратор 7, ) формирует цифру ю ,которая(И выдается из устройства на выход 10,1 и аналогичным образом управляет выдачей кода с регистра 4,1 + 1 на сумматор 1. ) + 1. Кроме того, на каждый сумматор 1) поступают в соответствии с выражением (3) следу. ющие величины: удвоенный код содержимого регистров 2,1 и 3,1 (2 йх,) ) и код с13)выхода дешифратора 7, 1 2 Ч (выдается14) в два старших сумматора). После окончания переходного процесса сформированный на вы ходе сумматора 1,1 код принимается в виде поразрядных сумм и переносов на регистры суммы 2.1 и переносов 3. ). Для вычисления всех функций Ч: А Ч 1.,)++ В(1 = 1, и) с точностью до ц цифр не.обходимо выполнить и + и + 1 циклов вы.чи слепня.Предлагаемое устройство позволяет вычислить результат с разрядностью о за и + и + 1циклов. Длительность цикла вычисления впредлагаемом устройстве состоит из временисуммирования без распространения переноса,времени срабатывания дешифратора и коммутатора и времени приема кода на регистры2 и 3, Округляя в сторону увеличения, можно принятьи,идеал.= +ф сВ,где 7 - время суммирования в одноразряд.ном сумматоре;- время приема кода на регистрсв(время сдвига),В известном устройстве длительность цикла .состоит из времени суммирования в с 1-разрядном сумматоре с распространением переносаи времени сдвига, т.е, )гьВ=сь+ 1 сдв,,Можно принять 10 В = 0,5 Г, тогда предлагаемое устройство, обладая более широкимифункциональными возможностями, дает вы.игрыш в быстродействии по сравнению с известным в1 ЧВВ и щ) 0,5)Рс 1 Ъ,идеал. ,5 (и+ +Например, при разрядности ц : 24 ии = 3 предлагаемое устройство позволяет вычислять функции Ув 25,2 раэ быстрееизвестного. 6Формула изобретенияУстройство для вычисления функции Ч, АЧ; + В,содержащее .и суммато. . ров коэффициентов (и - количество вычисляемых значений), и реп)стров сумм, и ком. мутаторов, первый регистр коэффициентов и блок синхронизации, выход которого подключен к управляющим входам регистров 1 О сумм, выход первого регистра коэффициентовсоединен с первым входом первого коммута.тора, выходы коммутаторов подключенык первым входам соответствующих суммато.ров коэффициентов, вторые входы которых15 соединены с выходами соответствующих регистров сумм, первые выходы сумматоровкоэффициентов соединены со входами соответствующих регистров сумм, о т л и ч а ющ е е с я тем, что, с целью повышения20 быстродействия, в него введены и - 1 регистровкоэффициентов, и регистров переносов, и выходных сумматоров и и дешифраторов, при.чем второй вход первого коммутатора соединен со входом устройства и с первым вхо 25 дом первого дешифратора, выходы регистровкоэффициентов со второго до и-го соединеныс первыми входами соответствующих коммутаторов, управляющие входы регистров переносов соединены с выходом блока синхрони 30зации, вторые выходы сумматоров коэффициентов соединены со входами соответствующихрегистров переносов, выходы которых соеди нены с третьими входами соответствующихсумматоров коэффициентов, выход -го дешифратора (1 = 1, 2 и - 1) соединен счетвертым входом 1-го сумматора коэффици.ентов, вторым входом (1+1)-го коммутатораи первым входом (1+1)-го дешифратора,выход и-го дешифратора соединен с четвертым входом и-го сумматора коэффициентов,40 выходы старших разрядов регистров сумми переносов соединены с первыми и вторымивходами соответствующих выходных сумматоров, выходы которых соединены с входамисоответствующих дешифраторов, выходы кото 45 рых являются выходами устройства.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССР Иф 575647,кл. 6 06 Е 7/38, 1977.50 2. Авторское свидетельство СССР У 451088,кл. 6 06 Е 15/20, 1973 (прототип),881737 оставительехред М,Го ж 748 Подпитвенного комитета СССРетений и открытий.- 35, Раушская наб., д, 4/5 аз 9972/73 Редактор Н. Ромжа Тир ВНИИПИ Государ по делам изоб 113035, Москва, Ж

СмотретьЗаявка

2842070, 16.11.1979

КИЕВСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. 50 ЛЕТИЯ ВЕЛИКОЙ ОКТЯБРЬСКОЙ СОЦИАЛИСТИЧЕСКОЙ РЕВОЛЮЦИИ

ЖАБИН ВАЛЕРИЙ ИВАНОВИЧ, КОРНЕЙЧУК ВИКТОР ИВАНОВИЧ, КОЗАК ВЛАДИМИР СИДОРОВИЧ, КОЗЛОВ ЮРИЙ ВЛАДИМИРОВИЧ, ПОКАРЖЕВСКИЙ АЛЕКСАНДР СЕРГЕЕВИЧ, СКОЧКО АЛЕКСАНДР ПЕТРОВИЧ, ТАРАСЕНКО ВЛАДИМИР ПЕТРОВИЧ, ЩЕРБИНА АЛЕКСАНДР АНДРЕЕВИЧ

МПК / Метки

МПК: G06F 7/544

Метки: 1в, вычисления, функции

Опубликовано: 15.11.1981

Код ссылки

<a href="https://patents.su/4-881737-ustrojjstvo-dlya-vychisleniya-funkcii-u-a-u-1v.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления функции у =а у -1+в</a>

Предыдущий патент: Устройство для поиска чисел в заданном диапазоне

Следующий патент: Комбинированный функциональный преобразователь

Случайный патент: Привод транспортного средства