Устройство для моделирования быстропротекающего случайного процесса

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

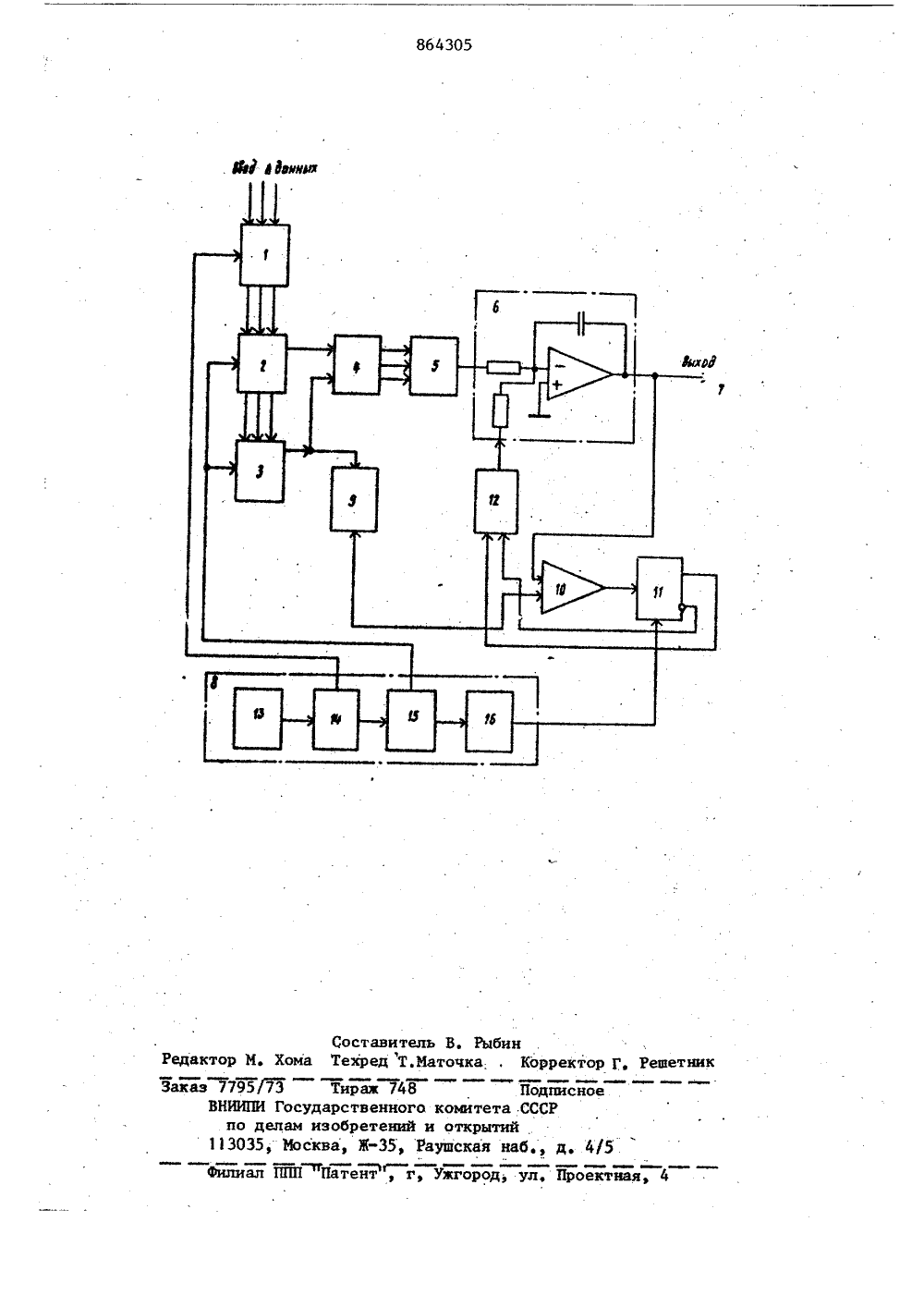

ОП ИСАНИВ ИЗОБРЕТЕНИЯ К АЭТОУСКОММ СВМДИВЛЬСЗО Союз Сов втсниаСоцнаянстнчвсннервспубянн р 1, 864305(51,) М. Кл. СО 667 ИВ с присоединением эаявнн,%в 9 аферствввй кенатат СССР ее аюен юебретеееФ н еткумтей(54) УСТРОЙСТВО ДЛЯ ИОДЕЛИРОВАНИЯ БЫСТРОПРОТЕКАЮЩЕГ СЛУЧАЙНОГО ПРОЦЕССА ако это устройство имеет очную точность воспронзв гналов большей длительно к ошибка интегратора по смещения и току смещения ного усилителя приводит евой линии моделируемого едостания. снтак ка т ап опе- ухо- сигжениюрадоду нулнала,о ь изобретения - повышени моделирования случайного н Пост авлчто в устбыстропро цесса, со минающииявляет"яинформацизапоминаформациора, выходвому входго соедин.разователя ющ ннь напрани ации 12 Изобретение относится к аналоговой вычислительной технике и может быть использовано для точного воспроизведения быстропротекающих случайных процессов.Известно устройство для кусочно" линейной аппроксимации функций, содержащее регистры, преобразователи "код-напряжение", интегратор, аналоговое вычитающее устройство 1 11.носОднако это устройство имеет не- ла.19 достаточную точность воспроизведения быстропротекающих случайных процессов так как необходимо время сброса интегратора или переключения одногоИ, интегратора на другой.Наиболее близким по технической сущности к изобретению является устройство, содержащее оперативное запоминающее устройство, устройство .вво" да данных, два. регистра, цифровой вычитатель, преобразователь, "кодряжение" интегратор, блок синхенная цель достигается тем, ойство для моделирования екающего случайного продержащее оперативный запоя лок, группа входов которого руппой входов устройства, нные выходы оперативного его блока соединены с инви входами первого регисткоторого подключен к первычитателя, выход которон со входом первого преобкода в напряжение, выход864305 10 вызванную напряжением смещения или током смещения, напряжение на выходе 5 20 25 ЗО 35 40 45 50 55 Устройство содержит оперативный запоминающий, блок 1, регистры 2,3, вычитатель 4, первый преобразователь кода в напряжение 5, интегратор 6, клемму 7 вьюоду устройства блока 8 синхронизации, второй преобразователь 9 кода в напряжение, компаратор 10, триггер 1,1, источник 12 двуполярного опорного напряжения. Блок 8 синхронизации содержит генератор тактовой частоты 13 и последовательно соединенные три одновибратора 14-16. Выход генератора тактовой частоты 13 подключен ко входу одновибратора 14, первый выход которого является первым выходом блока 8. Второй выход одновибрйтора 14 подключен ко входу одновибратора 15, первый выход которого является вторым выходом блока 8. Второй выход одновибратора 15 подключен ко входу одновибратора 16, выход которого является третьим выходом блока 8. которого подключен к первому суммирующему входу интегратора, выход которого является выходом устройства,к управляющему входу оперативного запоминающего блока подключен первыйвыход блока синхронизации, второйвыход которого соединен с управляющими входами первого и второго регистров, информационные выходы первого регистра подключены к информационным входам второго регистра выход которого соединен со вторым входом вычитателя, введены второй преобразователь кода в напряжение, источник двуполярного опорного напряжения, компаратор и триггер, причемвыход второго регистра подключенко входу второго преобразователякода в напряжение, выход которогоподключен к первому, входу компаратора, выход которого соединен с первым входом триггера, прямой выходкоторого подключен к первому входудвуполярного источника опорного напряжения, выход которого соединенсо вторым суммирующим входом интегратора, выход которого подключен ковторому входу компаратора, третийвыход блока синхронизации соединенсо вторым входом триггера, инверсныйвыхоц которо;о подключен ко второмувходу двуполярного источника напряжения,На чертеже изображена схема предлагаемого устройства,4 Устройство работает следующим об разом. Входные данные об ординатах моделируемого сигнала поступают в опе ративный запоминающий блок 1 и хранятся там, До начала формирования сигнала регистры 2,3 находятся в нулевомсостоянии. В связи с тем, что интегратор 6 имеет ошибку интегрирования,интегратора 6 не равно нулю, поэтомукомпаратор 1 О в соответствии с разницей напряжений на выходе второго преобразователя 9 кода в напряжение и интегратора 6 устанавливает триггер 11по команде от блока синхронизации8 в соответствующее положение так,что его выход устанавливает соответствующую полярность управляемого ис, точника 12 двуполярного опорного напряжения таким образом, чтобыуменьшить величину ошибки интегратора 6.По началу формирования сигналакод первой ординаты поступает в первый регистр 2, В то время во второйрегистр 3 переписывается нуль, Таккак на выходе второго регистра 3 записан нуль, то на выходе второго преобразователя 9 кода в напряжениетакже нулевое напряжение, Поэтомузаряд емкости интегратора 6 на первомшаге моделирования осуществляется сцелью этой компенсации,Далее в соответствии с разностьюкодов двух регистров 2,3 вычитатель4 устанавливает на выходе первогопреобразователя 5 кода в напряжение,которое приводит к линейному зарядуемкости интегратора 6. Через время,определяемое интервалами между ординатами из оперативного запоминающегоблока 1, поступает значение кода второй ординаты в (буферный) регистр 2,а значение кода первой ординаты перепишем по команде от блока 8 синхронизации во второй регистр 3, Навтором шаге моделирования в соответствии с разностью кодов второй и первой ординат, записанных соответственно в регистры 2,3 вычитатель 4устанавливает на выходе преобразователИ кода в напряжение 5 напряжение,которое приводит к дальнейшему заряду емкости интегратора 6, Так женачалу второго шага моделированияСпроисходит сравнение выходного напряжения первой ординаты, снимаемо86430 0 15 20 30 35 5го с выхода преобразователя 9 кодав напряжение, с выходным напряжениеминтегратора 6 на компараторе 10, который через триггер 11 устанавливаетпо команде от блока 8 синхронизациисоответствующую полярность управляемого источника 12 двуполярного опорного напряжения, при этом на второмэтапе измерения корректируется ошибка интегратора, полученная на первомэтапе,В предлагаемом устройстве устраняется ошибка интегрирования, оноподдерживает нуль на выходе при остановке оперативного запоминающегоблока и записи нуля в регистры 2,3,что позволяет установить нуль навыходе устройства автоматически,Формула изобретения Устройство для моделирования бы-: стропротекающего случайного процесса, содержащее оперативный запоминающий блок, группа входов которого является группой входов устройства, информационные выходы оперативного запоминающего блока соединены с информационными входами первого регистра, выход которого подключен к первому входу вычитателя, выход котооого соепинн со входом первого преобразователя кода в напряжение, выход которого подключен к первому суммирующему входу интегратора, выход которого является выходом уст- . ройства, к управляющему входу оперативного запоминающего блока под 5 6ключен первый вьход блока синхронизации, второй выход которого соединен с управляющими входами первого и второго регистров, информацнон"ные выходы первого регистра подключены к информационным входам второго регистра, выход которого соеди. нен со вторым входом вычитателя,о т л и ч а ю щ е е с я тем, что,с целью повышения точности моделирования, в него введены второй преобразователь,кода в напряжение, иисточник двуполярного опорного напря"жения, компаратор и триггер, причемвыход второго;регистра подключенко входу второго преобразователякода в напряжение, выход которогоподключен к первому входу компаратора, выход которого соединен с первым входом триггера, прямой выходкоторого подключен к первому входудвуполярного источника опорного напряжения, выход которого соединенсо вторым суммирующим входом интегратора, выход которого подключен ковторому входу компаратора, третийвыход блока синхронизации соединенсо вторым входомтриггера, инверсный обратный выход которого подключен ко второму входу двуполярногоисточника напряжения.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРУ 570070, кл. 6 06 6 7/48, 1975.2, Патент Великобритании 91404587,кл, 6 4 6 , опублик. 975, (прототип).864305 7795/73 Тираж 748 одписноНИИПИ Государственного комит СРпо делам изобретений и открытий13035, - Москва, Ж, Раушская наб., д. 4/5Филиал ППП Патент г, Ужгород, ул, Проектная,е к Составитель В. Рыбин Редактор М. Хома Техред Т.Иаточка . Корректор Г, Решетник

СмотретьЗаявка

2880666, 05.12.1979

БЕЛОРУССКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ИМ. В. И. ЛЕНИНА

ЯМНЫЙ ВИТАЛИЙ ЕВГЕНЬЕВИЧ, ПОДОЛЬНЫЙ ЭДУАРД ИОВОВИЧ, ЧУЯСОВ ВЛАДИМИР НИКОЛАЕВИЧ

МПК / Метки

МПК: G06G 7/48

Метки: быстропротекающего, моделирования, процесса, случайного

Опубликовано: 15.09.1981

Код ссылки

<a href="https://patents.su/4-864305-ustrojjstvo-dlya-modelirovaniya-bystroprotekayushhego-sluchajjnogo-processa.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для моделирования быстропротекающего случайного процесса</a>

Предыдущий патент: Устройство для моделирования виброзащиты оператора

Следующий патент: Устройство для моделирования механической передачи

Случайный патент: Способ контроля давления в цилиндре пресса при прессовании, например, электродных масс