Последовательно-параллельный аналого-цифровой преобразователь c коррекциейпогрешности

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

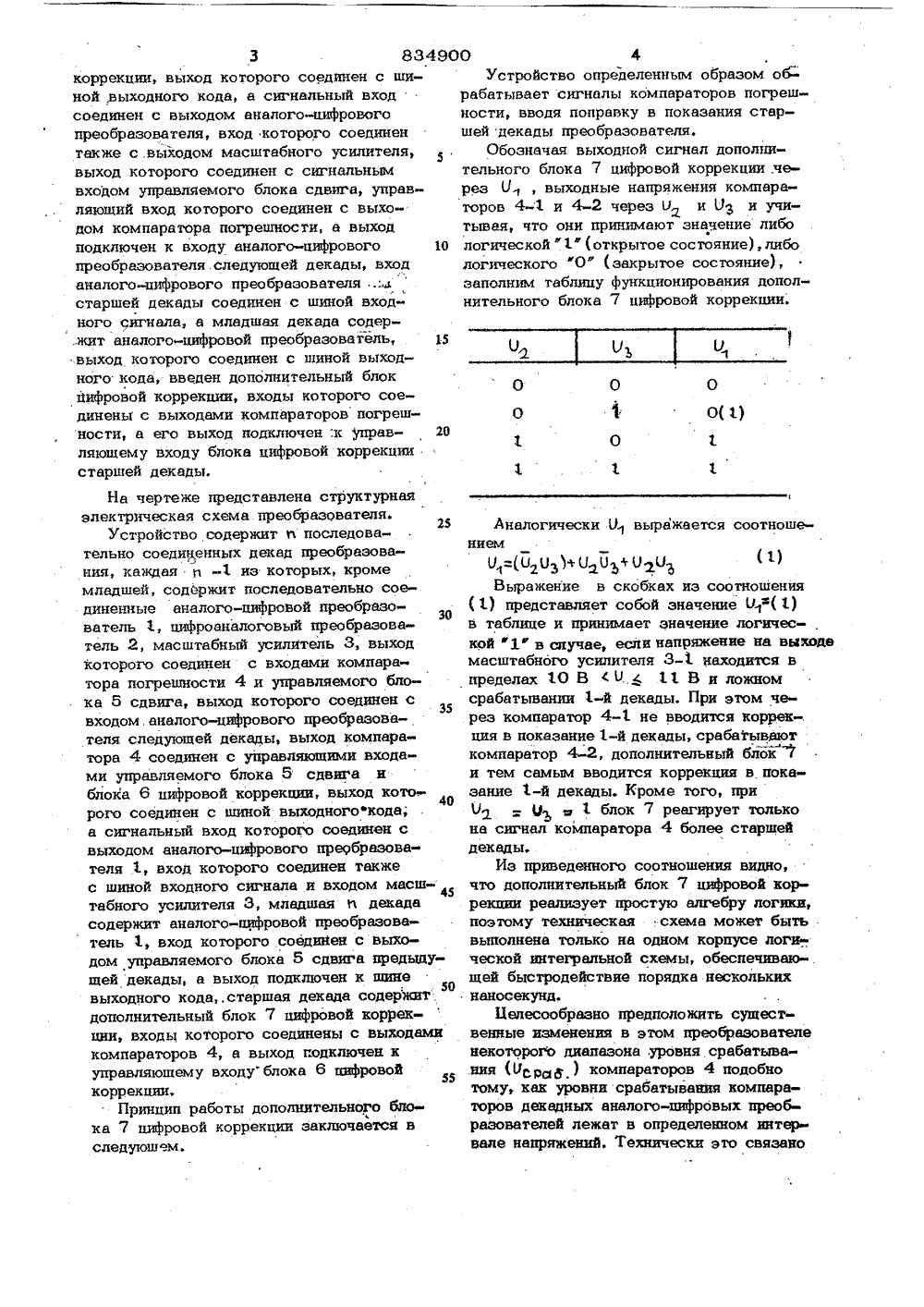

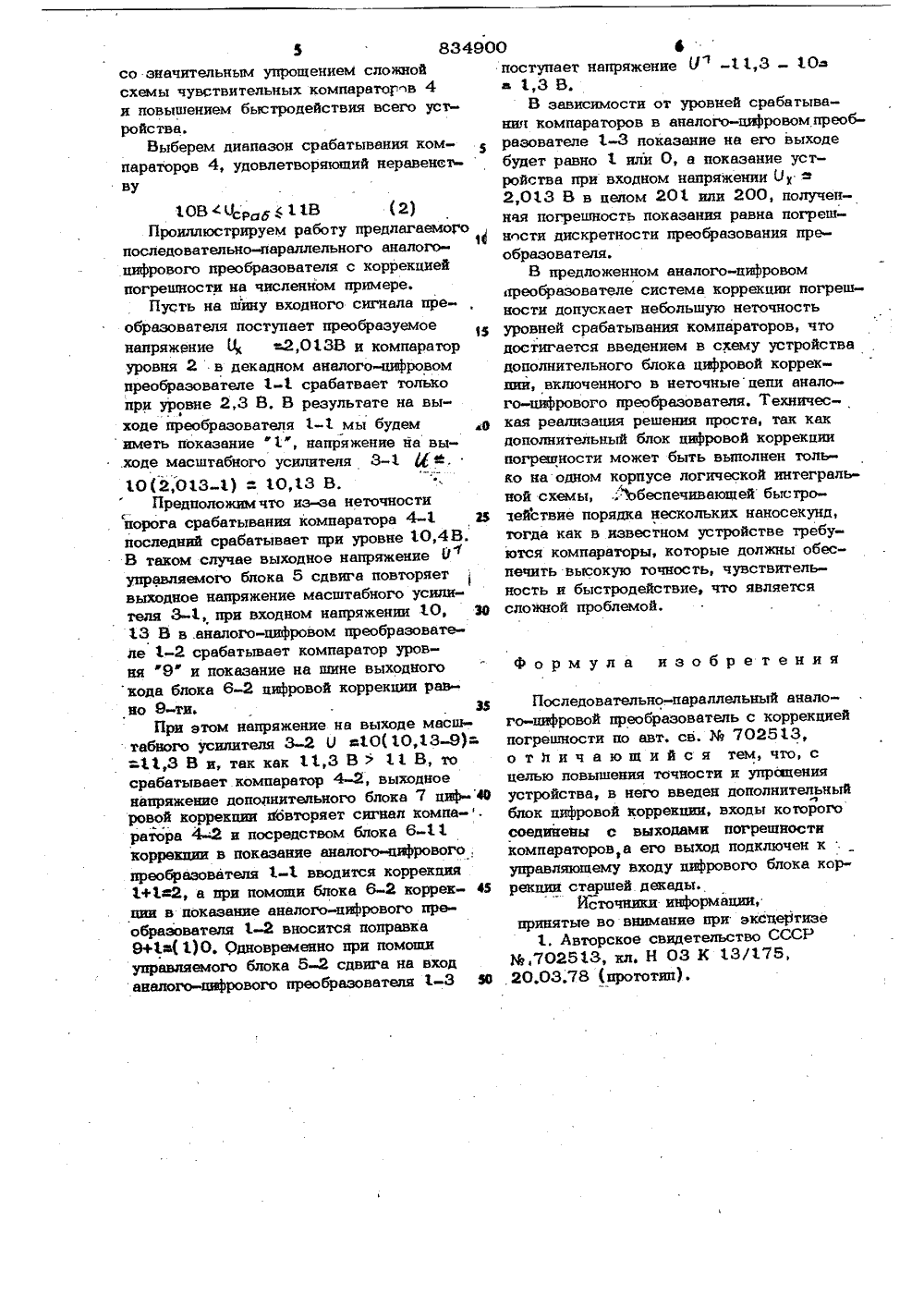

ОП ИСАНИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советски кСоциапистичесииаРеспублик и 1834900(23)приоритет Опубликовано 30,05.81 Бюллетень Лй 20Дата опубликования описания 03,06.81 па девви взвбветенвв н вернтяй,Ф ее,. Изобретение относится к приборостроению и предназначено для использования в качестве быстродействующего аналогоцифрового преобразователя в приборах и системах для измерения различных быст 5 ропротекающих пропессов, а также в системах автоматического управления и контроля.По основному автсв. % 70253.3 известно устройство, содержащее и последовательно соединенных декад преобразования, каждая т. -3, из которых состоит из. последовательно соединенных аналогоцифрового, цифроаналогового преобразователей, масштабного усилителя, компат 5 ратора погрешности и блока цифровой коррекции, соединенного также с выходом аналого-пифрового преобразователя, и управляемого блока сдвига, а младшая декада состоит из аналого-цифрового пре- о образователя, причем выход управляемого блока сдвига каждой предыдущей декады соединен с входом аналого-цифрового преобразователя последующей декады 1,2Недостатком такого устройства является возможность неверного срабатывания компараторов погрешности, котораяможет быть устранена с помощью высокочувствительных компараторов, Однако создание компараторов, обладающих одновременно высокой чувствительностью и быстродействием, является сложной задачей.Таким образом, в цепом недостаткомизвестного устройства является невысокаяточность и сложность.Цель изобретения - повышение точности и упрощение устройства,Поставленная цель достигается тем,что в последовательно-параллельный аналого-цифровой преобразователь с коррекцией погрешности, содержащий и последовательно соединенных декад преобразования, каждая )т -1 из которых состоитиз последователЬно соединенных аналогоцифрового, цифроаналогового преобразователей, масштабного усилителя и компаратора погрешности, выход которого соединен с управляющим входом блока цифровой834900 4и- Устройство определенным образом об-"рабатывает сигналы компараторов погрешности, вводя поправку в показания старшей декады преобразователя.Обозначая выходной сигнал дополнительного блока 7 цифровой коррекции .чьв- реэ О, выходные напряжения компараторов 4-1 и 4-2 через О и 0 и учитывая, что они принимают значение либо10 логической "1" (открытое состояние), либологического "О" (закрытое состояние),заполним таблицу функционирования дополнительного блока 7 цифровой коррекции. О л коррекции, выход которого соединен с ш ной,выходного кода, а сигнальный вход соединен с выходом аналого-цифрового преобразователя, вход которого соединен также с.выходом масштабного усилителя выход которого соединен с сигнальным входом управляемого блока сдвига, упра ляющий вход которого соединен с выходом компаратора погрешности, а выход подключен к входу аналого-цифрового преобрвзователя . следующей декадывход аналого-цифрового преобразователя,.с старшей декады соединен с шиной входного сигнала, а младшая декада содер.жит аналого-цифровой преобразователь, 15 выход которого соединен с шиной выходного кода, введен дополнительный блок Йифровой коррекции, входы которого соединены с выходами компараторов погрешности, а его выход подключен:к управ ляюшему входу блока цифровой коррекции старшей декады.На чертеже представлена структурная электрическая схема преобразователя.25Устройство содержит ь последовательно соединенных декад преобразования, каждая и -1 из которых, кроме младшей, содьржнт последовательно соединенные аналого-цифровой преобразо 30 ватель 3 цифроаналоговый преобразователь 2, масштабный усилитель 3, выход которого соединен с входами компаратора погрешности 4 и управляемого блока б сдвига, выход которого соединен с входом. аналого-цифрового преобразователя следующей декады, выход компара" тора 4 соединен с управляющими входами управляемого блока 5 сдвига и блока 6 цифровой коррекции, выход кото-. рого соединен с шиной выходногофкода; а сигнальный вход которого соединен с выходом аналого-цифрового преобразователя 1, вход которого соединен также с шиной входного сигнала и входом масштабного усилителя 3, младшаядекада содержит аналого-цифровой преобразователь 1, вход которого соедипен с выходом управляемого блока 5 сдвига предыдущей декады, а выход подключен к пане, 50 выходного кода,.старшая декаде содержит дополнительный блок 7 цифровой коррекции, входы которого соединены с выходами компараторов 4, а выход подключен к управляющему входу блока 6 цифровой коррекции,Принцип работы дополнительного блока 7 цифровой коррекции заключается в с едуюшем. АналогичесниемМО 2 ЦЗ+ ЦЬОт"( )Выражение в скобках иэ соотношения( 4.) представляет собой значение Оф( 1)в таблице и принимает значение логической ф 1 ф в случае, если напряжение нв выходемасштабного усилителя 3-1 находится впределах 10 ВО. ( 11 В и ложномсрабатывании 1-й декады. При этом через компаратор 4-1 не вводится коррек-.ция в показание 1-й декады, срабатываюткомпаратор 4-2, дополнительный блок ")и тем самым вводится коррекция в показание 1-й декады. Кроме того, приО 2: Оъ1 блок 7 реагирует толькона сигнал компарвтора 4 более старшейдекады,Из приведенного соотношения видно,что дополнительный блок 7 цифровой коррекции реализует простую алгебру логики,поэтому техническая схема может бъ 1 тьвыполнена только на одном корпусе логической интегральной схемы, обеспечиваю-.щей быстродействие порядка несколькихнаносекунд.Белесообрвзно предположить существенные изменения в этом преобразователенекоторого диапазона,уровня срабатывания (Урс ) компараторов 4 подобнотому, как уровни срабатывания компараторов декадных анелого-цифровых преобразователей лежат в определенном интервале напряжений. Технически это связано ки Й выражается соотноше 183490 со значительным упрощением сложной схемы чувствительных компаратор в 4 и повышением быстродействия всего устройства.Выберем диапазон срабатывания компараторов 4, удовлетворяющий неравенст- ву Последовательно-.параллельный аналого-цифровой преобразователь с коррекциейпогрешности по авт, св. % 70253,3,о т л и ч а ю щ и й с я тем, что, сцелью повышения точности и упрощенияустройства, в него введен дополнительныйблок цифровой коррекции, входы которогосоединены с выходами погрешностикомпараторов,а его выход подключен куправляющему входу цифрового блока коррекпии старшей декады,Источники информации,принятые во внимание при эксцертизе1. Авторское свидетельство СССР%470253.3 ф клф Н 03 К 3.3/3.75,20.03,78 (прототип) . жвОсрр ( 3. 3.В (2)Проиллюстрируем работу предлагаемоГо11 последовательно-параллельного аналогоцифрового преобразователя с коррекцией погрешности на численном примере.Пусть на шину входного сигнала преобразователя поступает преобразуемое напряжение Ок а 2,03.3 В и комператор уровня 2 в декадном аналого-цифровом преобразователе 3-3. срабатвает только при уровне 2,3 В. В результате на выходе преобразователя 1-3. мы будем6 иметь показание 1", напряжение на вы,ходе масштабного усилителя 3-1 3,0(2,03.3-3,) й 30,3.3 В.Предцоложим что иза неточности порога срабатывания компаратора 4-1 О последний срабатывает при уровне 3.0,4 В. В таком случае выходное напряжение 0 управляемого блока 5 сдвига повторяет выходное напряжение масштабного усилителя 3-1, при входном напряжении 3.0, 39 3,3 В в.аналого-цифровом преобразователе 3-2 срабатывает компаратор уровня ф 9 ф и показание на шине выходного кода блока 6-2 цифровой коррекции равно 9-ти, 3При этом напряжение на выходе масштабного усилителя 3 2 О а 3.0(4,0,3.3 9) =3.1,3 В и, так как 3.3.,3 В ) 3. 1 В, то срабатывает компаратор 4-2, выходное напряжение дополнительного блока 7 циф 49 ровой коррекции повторяет сигнал компа-, ретора 4-2 и посредством блока 6-3.3, коррекции в показание аналого-пифрового. преобразователя 3. 1 вводится коррекция 1+М 2, а при помощи блока 6-2 коррек ции в показание аналого-цифрового преобразователя 3.-2 вносится поправка 9+М( 1) О, Одновременно при помощи управляемого блока 5-2 сдвига на вход аналого-шафрового преобразователи 1-3 6 0 Споступает напряжение У 1 3.,3 3.0 а1а 33 В,В зависимости от уровней срабатывания компараторов в аналого-цвфровомпреобразователе 3.-3 показение на его выходебудет равно 3. или О, а показание устройства при входном напряжении О -й2,03.3 В в целом 203. или 200, полученная погрешность показания равна погрешности дискретности преобразования преобразователя.В предложенном аналого-цифровомпреобразователе система коррекции погрешности допускает небольшую неточностьуровней срабатывания компараторов, чтодостигается введением в схему устройствадополнительного блока цифровой коррекции, включенного в неточныецепи аналого-цифрового преобрезоветеля. Техническая реализация решения проста, так какдополнительный блок цифровой коррекциипогрешности может быть выполнен только на одном корпусе логической интегральной схемы, . Ъбеспечивеюшей быстроействие порядка нескольких наносекунд,тогда как в известном устройстве требуются компараторы, которые должны обеспечить высокую точность, чувствительность и быстродействие, что являетсясложной проблемой,формула изобретенияСоставитель И. С томРедактор Н. Кешеля Техред ЕХавраюещко Корректор М, Шароз 43.3.7/85 Гираж 988 Подписно ВНИИПИ Государственного комитета ССС по делам изобретений и открытий 113035, Москва, Ж 35, Раушская наб., д. 4 ПП Патент, г. Ужгород, ул. Проектная, 4

СмотретьЗаявка

2501187, 01.07.1977

ПРЕДПРИЯТИЕ ПЯ Г-4934

ПИЛЬВ МЕХИС АРПОВИЧ, АЛЕКСЕЕВ ПАВЕЛ ПАВЛОВИЧ

МПК / Метки

МПК: H03K 13/175

Метки: аналого-цифровой, коррекциейпогрешности, последовательно-параллельный

Опубликовано: 30.05.1981

Код ссылки

<a href="https://patents.su/4-834900-posledovatelno-parallelnyjj-analogo-cifrovojj-preobrazovatel-c-korrekciejjpogreshnosti.html" target="_blank" rel="follow" title="База патентов СССР">Последовательно-параллельный аналого-цифровой преобразователь c коррекциейпогрешности</a>

Предыдущий патент: Аналого-цифровой преобразователь

Следующий патент: Преобразователь напряжения вовременной интервал

Случайный патент: Электродное устройство