Устройство кодирования и декодирования видеоинформации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 743227

Автор: Попашенко

Текст

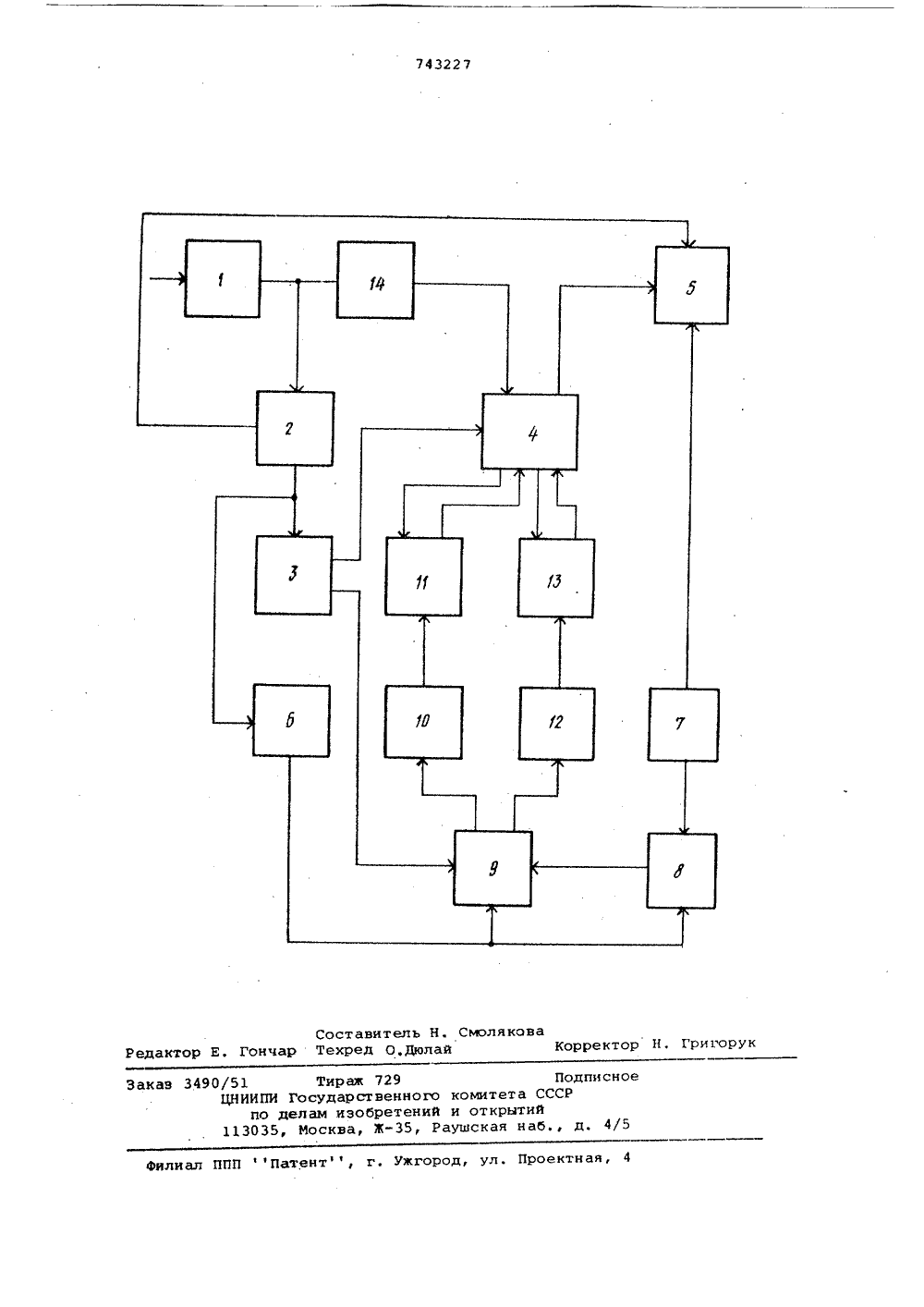

Союз Советсиик Социалистических Республик(51)М. Кл. с присоединением заявки М Н 04 М 7/16 Государственный комитет СССР по делам изобретений и открытий(71) Заявитель 54) УСТРОЙСТВО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ВИДЕОИНФОРМАЦИИ Изобретение относится к области телевидения.Известно устройство кодирования и декодирования видеоинформации, содержащее, последовательно включенные 5 входной согласующий усилитель, селектор синхросигнала, блок упранления, коммутатор сигнала иэображения и, выходной согласующий усилитель, второй вход которого соединен с вторым выходом селектора синхросигнала, выход которого подключен к входу генератора импульсов тактовой частоты 1)Однако известное устройство обла 15 дает недостаточно высокой помехоустойчивостью и степенью маскировки видеои н формации .Целью изобретения является повышение степени маскировки видеоинфор мации и помехоустойчивости.Для этого в устройство кодирования и декодирования видеоинформации, содержащее последовательно включенные входной согласующий усилитель, 25 селектор синхросигнала, блок управления, коммутатор сигнала изображе- . ния и выходной согласующий усилитуль, второй вход которого соединен с вторым выходом селектора синхросмтнала 30 выход которого подключен к входугенератора импульсов тактовой частоты, внедены пос,зедовательно включенные блок выбора кода, генератор последовательности псевдослучайных чисел, второй вход которого соединенс выходом генератора импульсон тактовой частоты, коммутатор адресногосигнала, соединенный, вторым и третьим входами соответственно с выходомгенератора импульсов тактовой частоты и с вторым выходом блока управления, первый адресный регистр ипервый блок памяти, второй вход которого и выход соединены соответственно с вторым выходом и вторымвходом коммутатора сигнала изображения, последовательно включенные нторой адресный регистр, соединенныйвходом с вторым выходом коммутатораадресного сигнала, и второй блокпамяти, второй вход и выход которо-го соединены соответственно с третьим выходоМ и третьим нходом коммутатора сигнала иэображения, аналогоцифровой преобразователь, вход ивыход которого соединены соответственно с входом селектора сивхросигнала и с четвертым входом коммутатора сигнала иэображения, причемвторой выход блока выбора кода соединен с третьим входом выходногосогласующего усилителя,Н а чертеже предст авлен а структурная электрическая схема предложенного устройства.устройство кодирования и декодирования вицеоинформации содержитпоследовательно включенные входнойсогласующий усилитель 1, селекторсийхросигнала 2, блок управления3, коммутатор 4 сигнала изображенияи выходной согласующий усилитель 5,второй вход которого соединен свторым выходом селектора синхросигнала 2. Выход последнего подключенк входу генератора импульсов тактовой частоты б. Кроме того устройствокодирования содержит блок 7 выборакода, генератор 8 последовательности псевдослучайных чисел, коммутатор 9 адресного сигнала, первый адресный регистр 10 и первый блок памяти 11, второй адресный регистр 12и второй блок памяти 13, аналогоцифровой преобразовател,Второй вход генератора 8 последовательности псевдослучайных чисел соединен с выходом генератора б импульсов тактовой частоты. Второй и третий входы коммутатора адресного сигнала 9 соединены соответственнос выходом генератора б импульсов .тактовой частоты и с вторым выходом блока управления 3, Второй вход и выход первого блока памяти 11 соединены соответственно с вторым выходом и вторым входом коьиутатора 4 сигнала иэображения. Вход второго адресного регистра 12 соединен с вторым выходом коммутатора 9 адресного сигнала. Второй вход и выход второго блока памяти ),3 соединены соответственно с третьимвыходом и третьим входом коммутатора 4 сигнала изображения. Вход и выход аналогоцифрового преобразователя 14 соедийены соответственно с входам селектора синхросигнала 2 и с четвертым входом коммутатора сигнала изображе,ния 4, Второй выход блока 7 выбора кода соединен с .третьим входом выходного согласующего усилителя 5.В режиме кодирования устройство работает следующим образом.Исходный полный видеосигнал через входной согласующий усилитель 1 поступает на вход селектора синхросигнала 2. Выделенный им сигнал синхронизации поступает на блок управления 3 и генератор б импульсов тактовой. частоты. В последнем сигнал синхронизации осуществляет фазирование последовательности импульсов тактовой частоты. Выход входного согласующего усилителя 1 соединен также через аналого-цифровой преобразователь 14 с четвертым входом коммутатора 4 сигнала изображения, осуществляющего последовательное (через кадр) подключение выходного сигнала аналого-цифрового пре, образователя 14 к входам либо первого блока памяти 11, либо второгоблока памяти 13, Последовательностьпереключения задается поступающимна коммутатор 4 сигнала изображения сигналом .блока управления З,Входы блоков памяти 1 и 13 соединенысоответственно с выходами адресныхрегистров 10 и 12, на входы которыхпоступают выходные сигналы с коммутатора 9 адресного сигнала, такжеуправляемого блоком управления 3.15 На второй вход коммутатора поступает последовательность импульсов тактовой частоты от генератора б импульсов тактовой частоты, на первыйпоследовательность псевдослучайных 29 чисел от генератора 8 последовательности псевдослучайных чисел, Последовательность содержит числаот единицы до И, где Ичисло номинальных элементов раз ложения в исходном видеосигнале.Порядок следования чисел в последовательности определяется сигналомуправления, поступающим на управляющий вход генератора от блока выбора ЗО кода 7. Код последовательности псев-дослучайных чисел поступает на выходной согласующий усилитель 5 длязамешивания в зашифрованный видеосигнал в интервалах обратного хода.На выходной согласующий усилитель 5подаются также синхросигнал с выхода селектора синхросигнала 2 и зашифрованный видеосигнал с выходакоммутатора 4 сигнала изображения.Коммутаторы 4 и 9 работают синфазнотак, что в том кадре, в котором напервый блок памяти 11 поступаетисходный видеосигнал, первый адресный регистр 10 соединяется с генератором б импульсов тактовой часто ты, В этом же интервале временивторОй блок памяти 13 соединяетсясвоим выходом через коммутатор 4сигнала иэображения с входом выходного согласующегоусилителя 5, а навторой адресный регистр 12 (работающий при этом в режиме прямой установки числа, а не в режиме счета)поступает последовательность псевдослучайных чисел. В следующем кадревыход первого блока памяти 11 будетподключен коммутатором к входу выходного согласующего усилителя 5первый адресный регистр 10 - к выходу генератора 8 последовательности псевдослучайных чисел и поле па- бО мяти блока памяти 11, заполненноепо закону развертки исходного видеосигнала, будет считываться попсевдослучайному закону. В этом жеинтервале времени второй блок памя ти 13 будет соединен своим входом743227 50 с выходом аналого-цифрового преобразователя 14, а второй адресный регистр 12 - с выходом генератора импульсов тактовой частоты 6. После памяти блока памяти 13 будет заполняться по закону развертки исходнО- го видеосигнала.Работа устройства в режиме декодирования отличается от описанной тем, что при работе блока памяти в режиме записи на его адресный регистр поступает,через коммутатор 9 адресного сигнала последовательность псевдослучайных чисел. Порядок следования . чисел в последовательности, как и при кодировании, определяется сигналом управления от блока 7 выбора 15 кода. При этом адрес ячейки памяти, в которую записывается мгновенное значение сигнала иэображения, будет соответствовать адресу ячейки памяти кодируюшего устройства на пере дающем конце, из которой это мгновенное значение сигнала изображения извлечено при передаче. В результате по истечении интервала прямого хода по кадру после памяти будет 25 заполнено в той последовательности мгновенных эн ачений си гнала изображения, которая соответствует исходному изображению, Для считывания декодированного сигнала с блока памяти его адресный регистр коммутатором 9 адресного сигнала подключается к генератору б импульсов тактовой частоты и считывание производится по закону развертки исходного видеоси гн ала.Из описания режимов кодирования и декодирования очевидно, что различие между ними состоит только во взаимной фазировке коммутаторов 4 и 9. В режиме кодирования к адресному регистру блока памяти 11 или 13 должен быть подключен генератор б импульсов тактовой частоты, а к адресному регистру считываемого блока памяти должен быть подключен генера тор 8 последовательности псевдослучайных чисел. В режиме декодирования на адресный регистр заполняемого блока памяти должен быть подключен генератор 8 последовательностейпсевдослучайных чисел, а к адресному регистру считываемого блока памяти должен быть подключен генератор б импульсов тактовой частоты.Переход от режима кодирования к режиму декодирования осуществляетсявнутренней коммутацией в блоке управления 3. Возможность использования одного и того же устройства и напередающей и на приемной стороне спереключением режима прием-передачаф дает значительные техническиепреимушества при эксплуатации аппаратуры. Формула изобретения Устройство кодирования и декодирования видеоинформации, содержащеепоследовательно включенные входнойсогласующий усилитель, селекторсинхросигнала, блок управления, коммутатор сигнала изображения и выходной согласующий усилитель, второйвход которого соединен с вторым выходом селектора синхросигнала, выходкоторого подключен ко входу генератора импульсов тактовой частоты,о т л и ч а ю щ е е с я ,тем, что,с целью повышения степени маскировки видеоинформации и помэхоустойчивости, введены последовательно включенные блок выбора кода, генераторпоследовательности псевдослучайныхчисел, второй вход которого соединенс выходом генератора импульсов тактовой частоты, коммутатор адресногосигнала, соединенный вторым и третьим входами соответственно с выходомгенератора импульсов тактовой частоты и с вторым выходом блока управления, первый адресный регистр и первый блок памяти, второй вход которого и выход соединены:соответственнос вторым выходом и вторым входомкоммутатора сигнала иэображения, последовательно включенные второй адресный регистр, соединенный входомс вторым выходом коммутатора адресного сигнала, и второй блок памяти,второй вход и выход которого соединены соответственно с третьим выходом и третьим входом коммутаторасигнала изображения, аналого-цифровой преобразователь, вход и выходкоторого соедийены соответственно,с входом селектора синхросигнала ис четвертым входом коммутатора сигнала иэображения, причем. второй выход блока выбора кода соединен стретьим входом выходного согласующего усилителя.Источники информации,принятые во внимание при экспертизе1. Патент Японии Р 51-12483,кл. 97 (5) А 15, 1976 (прототип.743227 лякова Составитель Ндактор Е. Гончар Техред О,Дюла Корректор Н, Григо одписи о ак д. 4/5 илиал ППППатент ф, г. Ужгород, ул. Проектная, 4 90/51ЦНИИ ПИПО113035 Тиражосударстлам изоИосква,729венного комитета Сретений и открытийЖ, Раушская наб

СмотретьЗаявка

2548153, 28.11.1977

ПРЕДПРИЯТИЕ ПЯ В-2645

ПОПАШЕНКО ЮРИЙ ИВАНОВИЧ

МПК / Метки

МПК: H04N 7/16

Метки: видеоинформации, декодирования, кодирования

Опубликовано: 25.06.1980

Код ссылки

<a href="https://patents.su/4-743227-ustrojjstvo-kodirovaniya-i-dekodirovaniya-videoinformacii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство кодирования и декодирования видеоинформации</a>

Предыдущий патент: Устройство для преобразования телевизионного сигнала

Следующий патент: Декодирующее устройство приемника цветного телевидения системы “секам”

Случайный патент: Способ получения гамма-(3-индолил) масляной кислоты