Каскадный процессор спектральной обработки сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

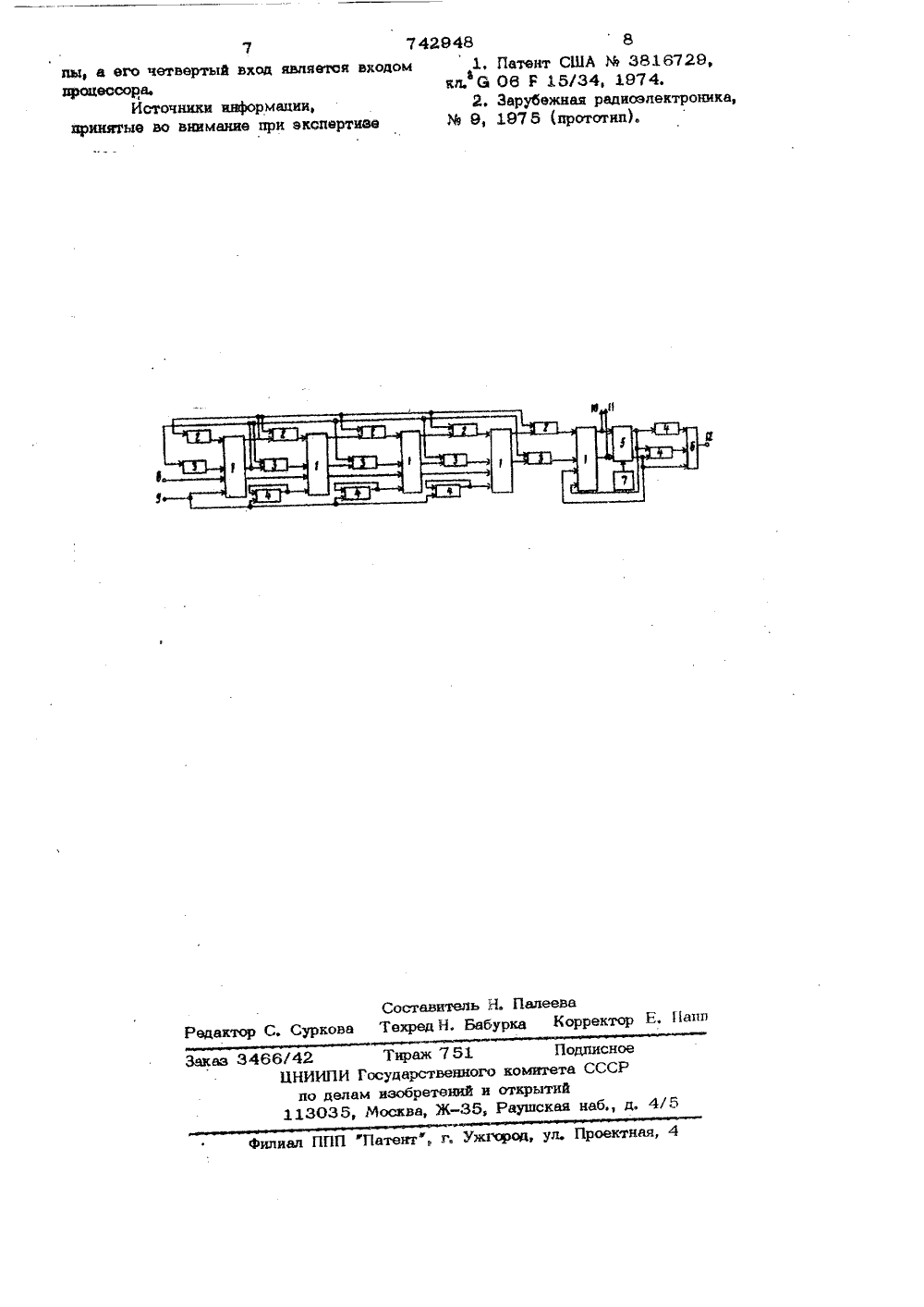

ОП ИСАНИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик и,742948(51)М, Кл. 5 06 Р 15/Э 4 с присоединением заявки РЙ Веударстеенньи комитет(23)Приоритет ао делам нзебретеннй н открытий(54) КАСКАДНЫЙ ПРОЦЕССОР СПЕКТРАЛЬНОЙ ОБРАБОГКИ СИГНАЛОВ Изобретение относится к вычислительной технике и может быть использованов различных цифровых вычислительныхсистемах обработки информации,Известно каскадное устройство быстрого преобразования Фурье, содержашее )1блоков памяти, соединенных последовательно, )1 арифметических блоков, каждыйиз которых соединен входом (выходом)с выходом (входом) соответствующевроблока памяти 11.Наиболее близким по технической сущности и достигаемому результату к изобретению является каскадный процессор,содержашийарифметических блоков,две группы по И блоков памяти последовательного доступа, 1 -ые блоки памятипоследовательного доступа соединены соответственно со входами 1 -го арифметического блока, выходы которого соединеньт 2 сс первыми входами ( ч + 1)-ых блоковпамяти последовательного доступа, выход 1-го арифметического блока соединен с третьим входом ( 1 + 1)-го арифме 2тического блока, четвертый вход 1 -го арифметического блока является входом ввода констант, при этом входы первых блоков памяти и третий вход первого арифметического блока соединены со вхо-ь дом процессора (21.Недостатком этих устройств являются узкие функциональные возможности, которые заклю таятся в следующем:их структура рассчитана на одну длину исходного массива, что сушественно снижает применяемость таких процессоров;ввод исходного массива информации и вывод массива результата проводятся в различном порядке следования операндов массивов, что при значительном быс тродействии каскадных процессоров выливается в дополнительное оборудование для переиндексации массивов;невозможность на том же оборудовании производить весовую обработку и вычиоление корреляционных функций.Цель изобретения - расширение функциональных возможностей за счет вьтчислв742948 ния корпекционных функций, а также засчет возможности вводе и вывода информации в любом порядке,Это достигается тем, что в каскадный процессор спектральной обработки сигналов, содержащий Р арифметических блоков, две группы по и блоков памяти последовательного доступа, выходы-х блоков памяти последовательного доступа то первой и второй групп соединены СООТ ветственно с первым и вторым входами 1 -го арифметического блока, первый ч второй выходы которого (кроме й,-го) соединены с первыми входами (+1)-х блоков памяти последовательного доступа соответственно первой и второй группы, третий выход-го арифметического блока, кроме ( п)-го и -го арифмет.г-;еских блоков, подключен к третьему входуЛВ+1)-го арифметического блоке, третий вход первого арифметического блока соединен СО ВХОДОМ ВВОДа КОНСтаНт ПРОПЕССОРат ВВЕ- денЫ коммутатор блок памяти произвольного доступа, индексный блок памяти, третья группа из р блоков памяти ттосл - довательного доступа, причем вход вводе констант процессоре соединен с первыми входами (т 1-2)-х блоков памяти последовательного доступа третьей группь:, выходы которых соединены соответственно со своими вторыми входами и с - :етвертыми входами ( 1+1-х арифметических блоков, первый выход блока памяти произвоЛьного доступа соединен через35 ( т 1 -1) ый блок памяти произвольного доступа третьей группы с первым входом коммутаторе, через Р-ый блок памяти произвольного доступа третьей Группы со Вторым Входом коммутатора и непосредственно с третьим входом 11 -го арифметического блока, первый н;О- рой выходы которого соединены соответственно с первым и вторым входека; блоке памяти пООИЗВОльнОГО доступа и с первым и вторыми выходами процессора, третий выход блока памяти произвольного дссту,. - подключен ко второму входу -го блоке памяти последовательнбго доступа третьод: груп 1 ты, к четвертому .входу И-го ерифметьческого блока и к третьему входу коммутатора, выход которого является третьим выходом процессоре, первый и второй выход первого арифметического блока соединены со Вторыми входами Ь блоков памяти последовательного доступе соответственно первой и второй Группы, а его четвертый вход является входом процессоге. ф.На чертеже приведена блок-схемакескеднОГО ппоцессоре спектральной Обработки сигналов,Процессор содержит арифметическиебЛСКИ 1 блтОК; 2 3 и 4 Памятн, ПОСЛЕдоттатель ого доступа, блок 5 памяти про".Л:ОГО ДССТУПЕ, КОММтУТатоР 6, ИНДЕК;-,-,:. 7, Вход 8 процессора, Вход Ьстент процесс,тра, Выходы 1(:,процессоре, Приведенный вари-.:Отл;"тт"Р т ГЕС" ЧИТЕН На МЕ К ттМаЛЬНУтотЦЛКНУ ВХОДНОГО Массява В Я = 64 ТОЧКИ.а кадтный процессор работает следую:.О Входу 8 В процРссОр подается:.:.СХОДКЬттй МЕ"С:.Вт КОтОРЫй ПЕРВЫМ аРИфМЕ;-,; Е ., тт тт,тпттк, М умножаЕТС я НЕ КонстаиГЫ .СВОБОЙ т;Утн,Цтин, ПОСТУПаЮЩИЕ ПО ВХодуЛа зтоже Входу 9 ВО Время ВессВт,.т обработки В первом арифметическомблоке в процтессор поступают необхоДИтта.Е КОНСТЕНТЫ ДЛЯ ПРОВЕДЕНИЯ ПРЯМОГОле.;О обратноГС преобрезОВения тттурье,сти консгепты постугеют в блоки 4 памяти псследовательного доступа.У: От -"-СОВОЙ ООРЯоотки В пеРВОмартитт,ттетттческом блоке по первому и втсоот.тл вьтходт етого блока респредел.=;етсяВ соответст.едующие блохи 2 и 3 памяти последоветельно 1 с доступе. 10 рядок поступЛ=ння ЗЛЕ;тЕНттов (ОтдЕЛЬНЫХ ОПЕрапдОВт, .сттого массиве может быть любым,В ТОМ ЧИСЛЕ .тцн МОГут ПОСтуПатЬ В ЕСТЕС- ствепном порядке. В какой конкретно блок памяти из 3 н 4-ой группы будут зеписывагься Очередные операнды определяют:-. блоком управления всего устройства, который на чертеже не показан. Для того, чтобы процессор мог приступить к своей ссновной опеРацттщт В его блоках памнти ДОЛЖ:-ти НЕХОДИТЬСЯ Сам ИСХОДНЫЙ МаССИВи на весовую функцию) ., (;:. "; = 9,:т, Ят -1 и массив конт";ЛО": , ;-т(. т;, тто ОтЗВСЛ тдт тго лО тЧ 7 ГЕ ПОД тцпаВ уннтв М ИНДЕКСНС 1 О СттОКа МНО:-,т-,ческчй бло11 оследи два блоке 4 памяти послеДОВЕТЕт.; - НотО ДОСТУПЕ СОВМЕСТНО С КОММУ.- . е"тттвеют вылечу ре ултата (ДИСКРЕТттОГО СПЕКтРа ФУРЬЕ) В ЕСТЕС:.Пенном порядке следования., три НЕОбкзт-.1 тмости Вт Чттс ттЕНтия Веанмней тт тоттт 1 Е.ЧттИО:тНО;: фУНтцпНРЕОтЕТСЯ ООЕСПВ -ВыЧИСЛЕ-Пте; ПРЯМОВ ДттскРОТнОе ПРЕ74294 Каскадный процессор может работать и с меньшими массивами исходной информации, Если процессор содержит 11 ариф 30 метических блоков, то это значит максимальный размер массива комплексных чисел, с которым он может работать, равен 21 . В случае подачи на его вход мечьшего массива, он устройством управления распределяется в старшие бло 35 ки памяти второй группы (нвчвлв счета блоков со входа процессоре). Работа процессора в этом случае по реализации алгоритма быстрого преобразования фурье46 длится во столько раз быстрее, во сколько раз исходный массив меньше максимального, нв который расчитан каскадный процессор. фТаким образом, изобретение позволяет существенно расширить практически на том же оборудовании функциональные возможности каскадного процессора. Каскадный процессор может вычислять спектр и корреляционные функции с любым массивом исходной информации не превышающим 2, где И- число каскадов вИ+процессоре. Ввод и вывод информации обеспечивается в процессоре в естественном порядке. Расширение функциональных возможностей каскадного процессора спектральной обработки сигналов позволяет расширить область его применения,5образование фурье, результат умножить на опорный спектр и нвхонец провести обратное дискретное преобразование фурье от произведения. Так, результат с промежуточных выходов 10, 11 5 можно сразу завести на вход 8 и вводить через первое арифметическое устройство, которое к этому моменту времени закончило свою работу по прямому дискретному преобразованию Фурье а (первый этап).На втором этапе это арифметическое устройство обеспечит умножение результата первого этапа на опорный спектр и устройство управления разнесет произве дение по соответствующим блокам памяти второй группы. Далее процессор обеспечивает выполнение обратного дискретного преобразования Фурье.Автокорреляционная функция вычисля ется аналогично, только в начале второго этапа вычислений первый арифметический блок от каждого комплексного значения в массиве результата первого этапа определит модуль.258фор мула 6изобретения Каскадный процессор спектральной обре ботки сигналов,содержащЫ л арифметических блоков, две группы по И блоков памяти последовательного доступа, выходы 1 -х блоков памяти последовательного доступа первой и второй групп соединены соответственно с первым и вторым входами 1 -го арифметического блока, первый и второй выходы каждого (кроме И -го), соединены с первыми входами (+1)-х блоков памяти последовательного доступа соответственно первой и второй группы, третий выход 1 -го арифметического блока, кроме ( И)-го арифметических блоков, подключен к третьему входу (1 +1)-го арифметического блока, третий вход первого арифметического блоха соединен со входом ввода констант процессора, о т л и ч а ю ш и й с я тем, что, с целью расширения функциональных возможностей за счет вычисления корреляционных функций, а также за счет возможности ввода и вывода информации в любом порядке, в него введены коммутатор, блок памяти произвольного доступа, индексный блок памяти, третья группа из И блоков памяти последовательного доступа, причем вход ввода констант процессора соединен с первыми входами ( И)-х блоков памяти последовательного доступа третьей группы, выходы которых соединены соответственносо своими вторыми входами , и с четвертыми входами ( 1 + 1 ) - х ариФметических блоков, первый выход блока памяти произвольного доступа соединен через(й -1 ) ый блок памяти произвольного доступа третьей группы с первым входом коммутатора, через ц-ый блок памяти произвольного доступа третьей группы со вторым входом коммутатора и непосредственно с третьим входом о го арифметического блока, первый и второй выходы которого соединены соответственно с первым и вторым входами блока памяти произвольного доступа и с первым и вторым выходами процессора, третий выход блока памяти произвольного доступа подключен ко второму входу ; -го блока памяти последовательного доступа третьей группы, к четвертому входу-го арифметического блока и к третьему входу коммутатора, выход которого является третьим выходом процессора, первый и второй выход первого арифметического. блока соединены со вторыми входами И блоков памяти последовательного доступа соответственно первой и второй груп7 742948 8пж, а его четвертый вход являетоя входом 1, Патент США М 3816729,процеооорае кл. З О 6 Р 15/34, 1974.Источники информедии, 2. Зарубежная радиоэлектроника,принятые во внимание при экспертизе Ж 9, 1978 (прототип). Составитель Н. Палеевактор С, Суркова Техред Н. Бабурка Корректор Е. 11 ап Закю 34 дписн ССабд. 4/5 П Патент", г. Ужгород, ул. Прое 42 ТиражНИИПИ Государстло делам иеобрете13035, Москва,нного комитетний и открытий 35, Раушская

СмотретьЗаявка

2568029, 06.01.1978

ПРЕДПРИЯТИЕ ПЯ Г-4677

ГРИБКОВ ИГОРЬ ГЕОРГИЕВИЧ, КОШЕЛЕВ ВЛАДИМИР ПАВЛОВИЧ, МОШКОВ АЛЕКСЕЙ АЛЕКСЕЕВИЧ, МУСАТОВ ИГОРЬ ФЕДОРОВИЧ, СТЕПУКОВА ТАМАРА ЛЕОНИДОВНА

МПК / Метки

МПК: G06F 17/14

Метки: каскадный, процессор, сигналов, спектральной

Опубликовано: 25.06.1980

Код ссылки

<a href="https://patents.su/4-742948-kaskadnyjj-processor-spektralnojj-obrabotki-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Каскадный процессор спектральной обработки сигналов</a>

Предыдущий патент: Цифровой функциональный преобразователь

Следующий патент: Цифровой фильтр

Случайный патент: Устройство для заряда накопительного конденсатора