Интегратор азимутных импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 691877

Автор: Чеботарев

Текст

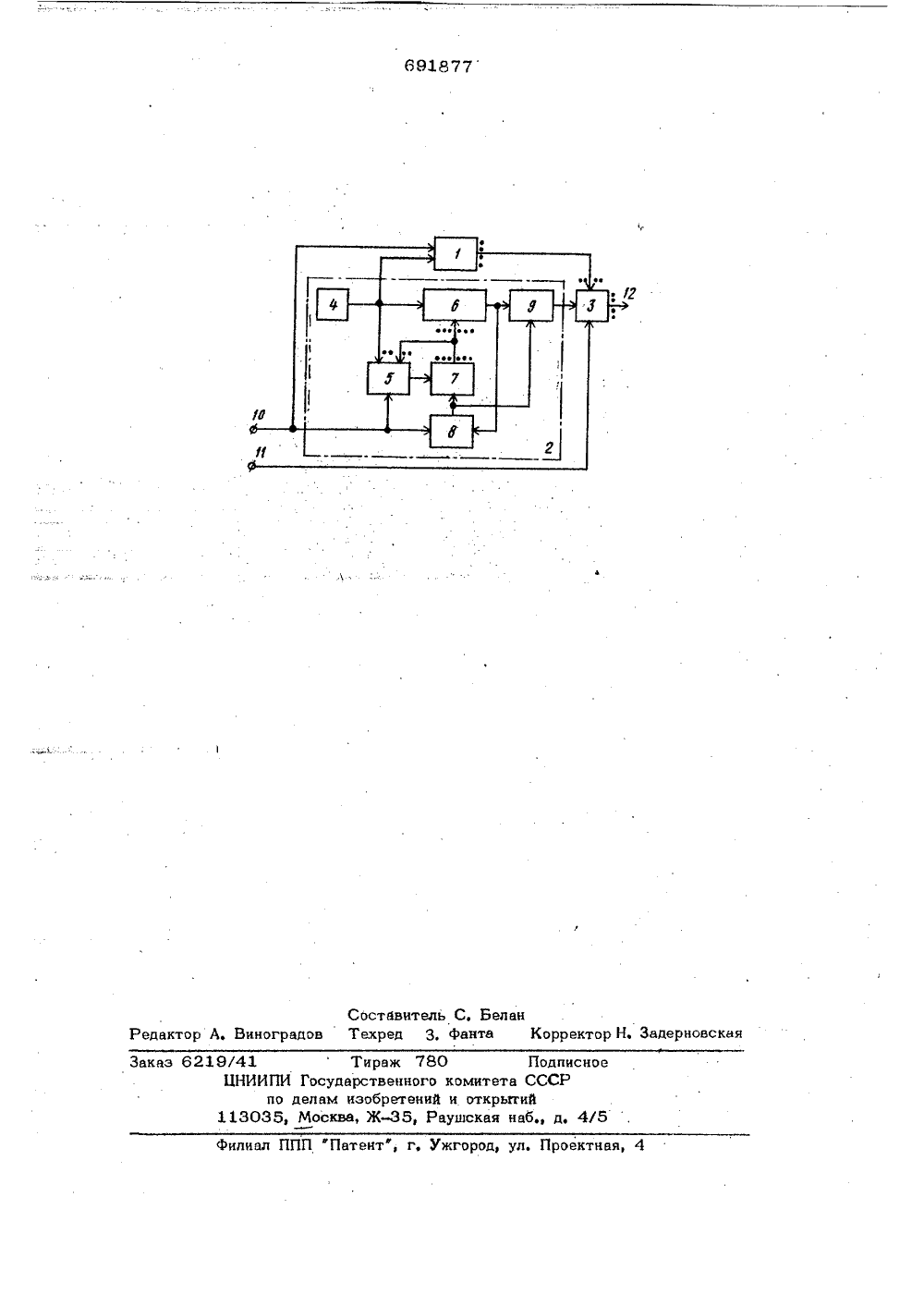

1) Заявят 54) ИНТЕГРАТОР АЗИМУТНЫХ ИМПУЛЬСОВ втожет бъри ди Изобретение относится к области а матики и вычислительной техникй, мосбыть использовано для воспроизведения значения угла вращения инерционнйх о ектов или для воспроизведения других плавно изменяющихся процессов, информация о которых передается методом приращений, в системах с цифровой обработкой информации.По основному авт. св. Ж 572785. известен интегратор, содержащий управляемый делитель частоты, один из входов которого соединен с генератором импульсов, а другой - подключен к выходу блока управления. Первый вход блока управления соединен с выходом блэка коррекции, состоящего из счетчика, логического элемента И и триггера, причем счетный вход счетчика соединен с выходом логического элемента И, управляющий вход - с шиной входного сигнала, а суммирующий входс выходом блока управления. Первый вход логического элемента И подключен к выходу генератора импульсов, а второй вход через триггер соединен с шиной азимутных импульсов. Второй вход триггера подключен к выходу счетчика, а выход логического элемента И является выходом блока коррекции. Второй вход блока уп равления соединен с выходом измерителя рассогласования, два входа которого подключены к шине азимутных импульсов и к выходу управляемого делителя частоты соответственно, а выход соединен также с входом компенсатора фазовой ошибки.Два других входа компенсатора подключены к выходу генератора импульсов и управляемого делителя частоты соответственно, а выход соединен с входом счетчика, другой вход которого подключен к шине юстировочного импульса, В интеграторе осуществляется умножение входных азимутных импульсов на целое наперед заданное число таким образэм, чтона выходе, управляемого делителя частоты формируются импульсы пэвьвиеннэй частоты, равномерно расположенные внуодных азимутных импульз 6918сов. Импульсы повышенной частоты подсчитываются счетчиком, выходные разряды которого образуют параллельный цифровой код. При изменении периода азимутных импульсов изменяется количество импульсов повышйнной частоты с выходауправляемого делителя частоты, что приводит к динамической ошибке внутри дискрета входных импульсов. Требуемое вэтом случае изменение частэты импульсов повышенной частоты осуществляетсяизменением коэффициента деления (с )управляемого делителя частоты черезблок управления и блок коррекции по результатам подсчета количества импульсов повышенной частоты за период между соседними входными азимутными импульсами в измерителе рассогласованияи с учетом частоты азимутных импульсов таким образом что - д. - величина 20(эпостоянная, Интегратор аэимутных импульсов с таким управлением хорошо отсле живает изменейие частоты взимутныхимпульсов в широком диапазоне частотс сохранением точности воспроизведенияугла. Компенсатор фазовой ошибки устраняет ошибку по фазе добавлением или вычитайием из выходной последовательности имйульсов повышенной частоты требу"емого количества импульсов. Значение уг 30ла поворота в двоичнэм" параллельном коде получается интегрированием имульсои повышенной частоты счетчиком, сбрасываемым в исходное состояниЕ однй разза оборот юстировочным импульсом.Однако в этом устройстве невозможноучитывать".направления изменения инерционного .процесса.Цель изобретения - расширение дйайа 40зона изменения входйьх сигналов.Это достЯгается тем, чтои устройствовведен анализатор частоты, первый входкоторого подключен к входу азимутныхимпульсов, интегратора, второй вход соеди45нен с выходом генератора импульсов,а выход подключен к третьему входу счетчика. На чертеже представлена структурная схема интеграторе азимутных импульсов.Интегратор содержит анализатор 1 частоты, следящий умножитель 2 частоты, реверсивный счетчик 3, генератор импульсов 4, блок коррекции 5, управля 55 емый делитель 6 частоты, блок управления 7, измеритель рассогласования 8, компенсатор фвзовой ошибки 9, вход азимутных импульсов 10 интегратора,77 4вход юстировэчных импульсов 11 и выходустройства 12,Устрэйство работает следующим образом.При передаче угла вращения (или информации о плавно изменяющемся процессе) по каналу связи на вход 10 передается последовательность взимутных импульсэв, следующих через равные угловыеинтервалы, и на вход 11 - юстировочный импульс, Интегратор осуществляетэкстраполяцию точного углового положения вала на интервале азимутных импульсов, используя инерционные свойства вращающегося объекта, Азимутные импульсы умножаются на целое наперед заданное число таким образом, что на выходеуправляемого делителя 6 частоты формируются импульсы повышенной частоты,равномерно расположенные внутри дискрета азимутных импульсов, Импульсы повышенной частоты через компенсатор фазовой ошибки 9 подсчитываются реверсивным счетчиком 3, выходные разряды которого образуют параллельный цифровой .код угла поворота. При изменении периода азимутных импульсов изменяется количество импульсов повышенной частотыс выхода управляемого делителя 6 частоть, что приводит к динамической ошибке внутри дискрета входных импульсов.Изменение частоты импульсов повышенной частоты осуществляется изменениемкоэффициента деления ( управляемого делителя 6 частоты через блок уйравления7 "и блок корреций 5 по результатамЙодсчета количесгва импульсов повышенной частоты за период между соседнимивыходными азимутными импульсами в измерителе рассогласования 8, с учетом частоты азимутных импульсов. Это обеспечивает сохранение точности воспроизведения угла в широком диапазоне входных частот езимутных импульсов. Импульсы повышенной частоты интегрируются реверсивным счетчиком 3, запускаюшимся каждым юстировочным импульсом,Инерционные свойства вращающегося объекта позволяют повысить разрешающуюспособность интегратора путем умножения частоты вэимутных импульсэв. Контур, состоящий из генератора импульсов4, управляемого делителя 6 частоты, измерителя рассогласования 8, блок управления 7, блока коррекции 5, кэмпенсатэра фвзовой ошибки 9 осуществляет слежуние за частотой входных азимутных импульсов и ее кратное умножение (выполиал ППП Патент, г, Ужгород, ул. Проектная, 4 9/41Тираж 780 БНИИПИ Государственного комитпо делам изобретений и от 113035, Москва, Ж, Раушск Подписноеа СССРгтийнабд. 4

СмотретьЗаявка

2509602, 21.07.1977

ПРЕДПРИЯТИЕ ПЯ А-3327

ЧЕБОТАРЕВ ОЛЕГ ЕГОРОВИЧ

МПК / Метки

МПК: G06G 7/18

Метки: азимутных, импульсов, интегратор

Опубликовано: 15.10.1979

Код ссылки

<a href="https://patents.su/4-691877-integrator-azimutnykh-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Интегратор азимутных импульсов</a>

Предыдущий патент: Устройство для дифференцирования частотно-импульсных сигналов

Следующий патент: Цифровое интегрирующее устройство

Случайный патент: Способ получения, -диметил -( -этоксифенил) тиомочевины