Устройство для возведения в квадрат чисел, представленных в унитарном коде

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

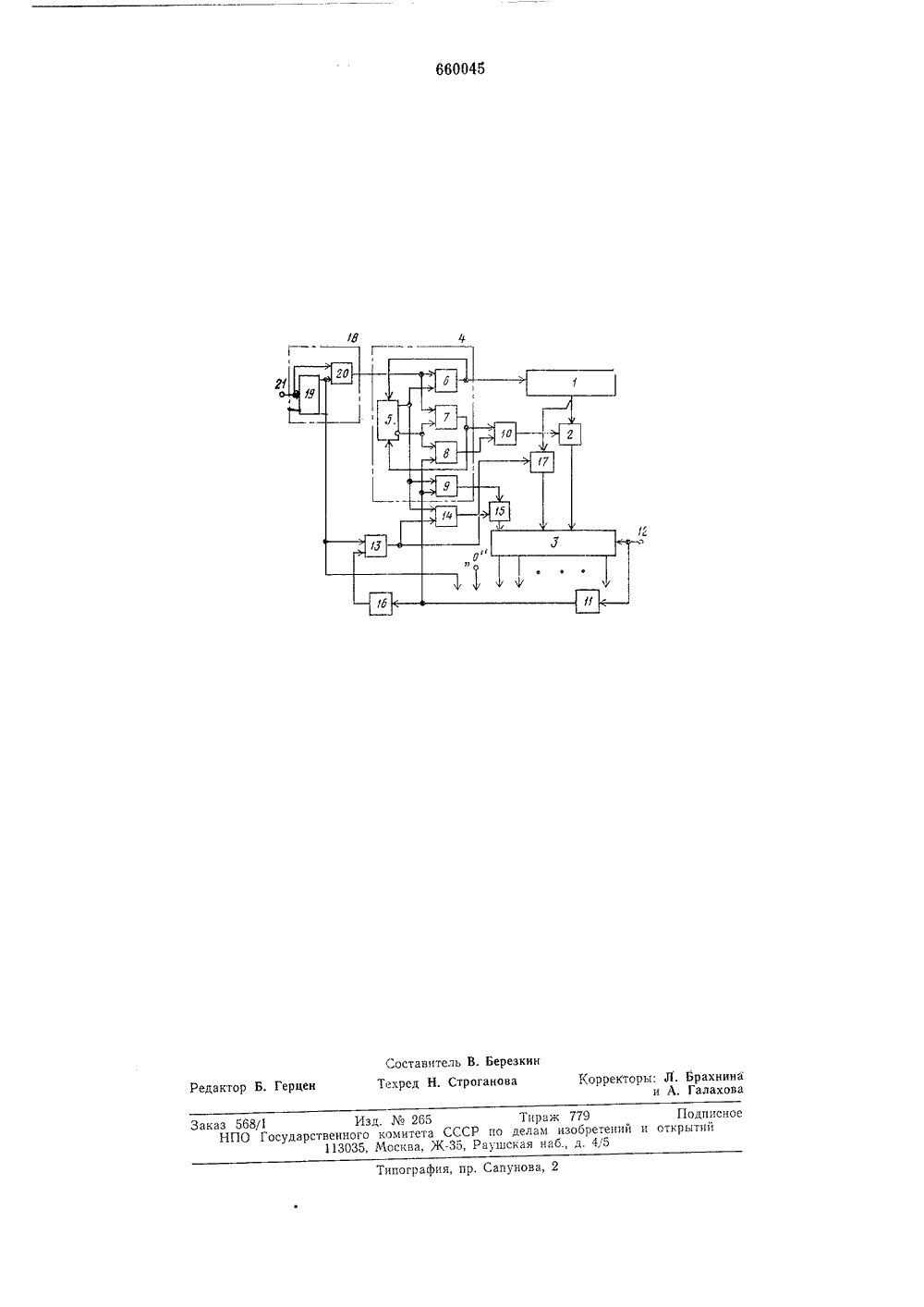

п)66 ОО 45 Сава Советских Социалистических Республик) М. Кл.6 06 Г 7/ 22) Заявлено 23,03.76 (21) 2337582/18-24 исоединением заявки Ю сударственный комитет СССР о делам изобретений и открытий(45) Дата опубликования описания 30.04,79 УДК 681.3272) Авторы изобретен Е, ф, Тощева В,Э, Пет 1) Заявител ДРАТ ЧИКОДЕ НИЯ В ИТАРН 4) УСТРОЙСТВО ДЛЯ ВОЗ П РЕДСТАВЛ ЕН Н ЫХ Изобретение относится к области вычислительной техники и может найти широкое применение в специализированных вычислительных устройствах дискретного действия и электроизмерительных приборах.Известно устройство для возведения в квадрат числа, представленного в унитарном коде, содержащее два сумматора, два счетчика, элементы И и триггер Ц.Недостатком его являются сравнительно большие затраты оборудования на реализацию устройства.Наиболее близким к изобретению является устройство для возведения в квадрат чисел, представленных в унитарном коде, содержащее сумматор, счетчик, группу элементов И, элемент ИЛИ, элемент задержки и дискриминатор четности, состоящий из триггера, прямой выход которого через первый и второй элементы И связан с первым и вторым выходами дискриминатора четности, а инверсный выход через третий и четвертый элементы И - с третьим и четвертым выходами дискриминатора четности, причем другие входы первого и третьего элементов И соединены с первым входом дискриминатора четности, а другие входы второго и четвертого элементов И - со вторым входом дискриминатора четности, выходы первого и третьего элементов И соединены соответственно со входами установки триггера дискриминатора четности в единичное и нулевое состояние, первый выход дискриминатора четности соединен 5 со счетным входом счетчика, третий и четвертый выходы дискриминатора четности соединены с входами элемента ИЛИ, второй вход дискриминатора четности через элемент задержки связан с управляющим 10 входом сумматора и с управляющим входом устроиства, первые входы группы элементов И соединены с выходом элемента ИЛИ, вторые входы - с выходами разрядов счетчика, а выходы - со входами раз рядов сумматора, начиная с третьего 2.Недостатком этого устройства являетсясравнительно низкое быстродействие.Целью изобретения является повышение быстродействия.20 Поставленная цель достигается тем, чтов устройство введены делитель частоты, состоящий из счетного триггера и элемента И, вторая группа элементов И, второй элемент задержки, второй элемент ИЛИ, пя тый и шестои элементы И, причем входустройства подключен ко входу делителя частоты, который соединен со счетным входом счетного триггера и первым входом элемента И делителя частоты, второй вход 30 элемента И делителя частоты подключен(5) и цаи,: -2 .) Тогда 55 60 При вышеприведенных вычислениях (5),обеспечиваемых при четном и счетным триггером 19, который находится в нулевом состоянии, закрывающем элемент И (2) 65 13, в сумматоре фиксируется значение т, е, п =. 41 г 2,для и. нечетных ад -- 1,т, е. и =. 1+4:г, +4 и 2,к прямому выходу счетного триггера, а выход к Выходу делителя частоты, который соединен с первым входом дискриминатора четности, прямой выход счетноготриггсра подключен также к первом входу 511 ятоО э, 1 сх 1 с 1 та И 11 к е 1 ыходу 11 ср ВОГОразр 5 да , стройства, Второй Вход итогоэлсмснта И через второй элемент задержки подключен к выходу первого элементазадержки, а выход - к первому входу шестОГО Злсмснте 1 И и к псОВым Входам элемстов И Второй группы, второй вход шестого элемента И соединен с прямым выходом триггера дискриминатора четности,а Выход - через второй элемент ИЛИ совместно со вторым Выходом деСкриминатора четности соединен со входом первогоразряда сумматора, выходы разрядоз счетчика сосдггнены с Вторыми входами элемсгггов И второй группы, выходы которых 20соединены со входами разрядов сумматора,начиняя со Второго, Выход второго разрядаустройства подключен к шине логическогонуля, Выходы разрядов сумматора являются вы.Одами разрядов хстройства, начиная с третьего.5 сроейгстВО, 11 рсдставлспе 10 с на черГсгкс,содсржиг счетчик 1, группу 2 элементов И,сумматор 3, дискриминатор 4 четности,триггер О, элементы И б, 7, 8, 9, элемент д 0ИЛИ 10, элсмснт 11 задержки, управляюн;ий Вход 12 устройства, элементы И 13 и14, элемент ИЛИ 15, элемент 1 б задержки,группу 17 элементов И, делитель 18 частоты, содержащий счстный триггер 19 и элемент И 20, вход 21 устройства,Устройство работает следующим образом. Бозводг.5 Ос в квадрат число импульсов поступает на вход 21 устройства.Зту 1 ослсдовательность и. импульсов 40можно представить в впдси: а,2+ а,2++ а 2",где а;член последовательности, принимающий значение ноль или еди ница при 1=0, 1, 2,п.После деления входной последовательности на делителе частоты 18 на его выходе образуется последовательность импульсов, 11 а Вид 5 50 и=а, +2 и,. Розвсдсх обе части равенства в квадрат; и - (а, + 2 г,) - . а 2+ 4 аагг, + 4 и,. Для и четных ао=0, 4Если подать гг на вход устройства, в сумматоре зафиксирустся: для и счетных и и, чсгпых импульсов;и 1 - ;4 1+2 - ,ггг (4) для гг нечетных и и нсчстных.Учитывая выражения (1), (3), (4) работу устройства можно представить в виде зависимости для гг четныхдля и нечетных, и, четныхдля п нечетных, п, четных Перед началом работы все элементы, обладающие памятью, сбрасываются в нулеВое состоянис.После деления на два, осуществляемое в делителе 18 частоты, последовательность и импульсов поступает на вход дискриминатора 4 четности. который выделяет на элементах И 7 и ИЛИ 10 нечетные импульсы, поступающие на управляющий вход группы 2 элементов И, что осуществляет перснос кода счетчика 1 в сумматор 3, а четные импульсы, формируемые в дискриминаторе 4 па элементе И б, поступают па вход счетчика 1. После прохождения последовательности импульсов выделяется сигнал конца последовательности, который удваивает число в сумматоре 3 и, если последовательность п, четная, т. е. триггер 5 находится в состоянии единица, прибавляет к содержимому сумматора 3 значение счетчика 1 путем записи его через группу 17 элементов И импульсом конца последовательности, проходящим по цепи первого и второго элементов 11 и 16 задержки и элемента И 13, открытого триггером 19.Если же последовательность и, импульсов нечетная, то импульс конца последовательности пройдя по цепи элементов 11 задержки, И 9, ИЛИ 15 поступит на вход первого разряда сумматора и прибавит единицу к его содержимому.Таким образом, в сумматоре фиксируется код числа и 2, а в счетчике код числаи иг - 1- или22и=4 П, так как суммирование значения содержимого счетчика производится со сдвигом на три разряда влево.Если последовательность и нечетная, а и, - четная, то элемент И 13 открыт, и сумматор 3 фиксирует значение, определяемое зависимостью (5)1+4 2 - +иПри нечетных последовательностях и и и, дополнительно открыт элемент И 14 и импульс конца последовательности, пройдя элемент ИЛИ 20, прибавляется к содержимому сумматора: 151+4 1+2+и,При возведении любого числа в квадрат,второй его разряд всегда содержит ноль, 20так какА = (а,2+ а,2++а 2")фгде а,= 0 или 1 при 1= О, 1, 2,и,Раскрывая скобки и собирая члены при 25 2, получима,а,2 + а,а,2 = 1,1,2.Исходя из изложенного, выход второгоразряда устройства подключен к шине логического нуля, а первый разряд устройства соединен с выходом триггера четности делителя частоты,Введение делителя частоты, элементов И,ИЛИ с их связями, позволило уменьшить 35частоту поступления импульсов на счетчик1, исключить при этом один разряд счетчика 1 и уменьшить разрядность сумматораза счет замены его первых разрядов значением триггера четности и логического 40нуля, что позволило повысить общее быстродействие устройства и расширить диапазон воспроизводимой им функции,Формул а изобретения45Устройство для возведения в квадрат чисел, представленных в унитарном коде, содержащее сумматор, счетчик, группу элементов И, элемент ИЛИ, элемент задержки и дискриминатор четности, состоящий 50 из триггера, прямой выход которого через первый и второй элементы И связан с первым и вторым выходами дискриминатора четности, а инверсный выход через третий и четвертый элементы И - с третьим и 55 четвертым выходами дискриминатора четности, причем другие входы первого и третьего элементов И соединены с первым входом дискриминатора четности, а другие входы второго и четвертого элементов 60 И - со вторым входом дискриминатора чстности, выходы первого и третьего элементов И соединены соответственно со входами установки триггера дискриминатора четности в единичное и нулевое состояние, первый выход дискриминатора четности соединен со счетным входом счетчика, третий и четвертый выходы дискриминатора четности соединены с входами элемента ИЛИ, второй вход дискриминатора четности через элемент задержки связан с управляющим входом сумматора и с управляющим входом устроиства, первые входы группы элементов И соединены с выходом элемента ИЛИ, вторые входы - с выходами разрядов счетчика, а выходы - со входами разрядов сумматора, начиная с третьего, отл и ч а ю щеес я тем, что, с целью увеличения быстродействия, в устройство введены делитель частоты, состоящий из счетного триггера и элемента И, вторая группа элементов И, второй элемент задержки, второй элемент ИЛИ, пятый и шестой элементы И, причем вход устройства подключен ко входу делителя частоты, который соединен со счетным входом счетного триггера и первым входом элемента И делителя частоты, второй вход элемента И делителя частоты подключен к прямому выходу счетного триггера, а выход - к выходу делителя частоты, который соединен с первым входом дискриминатора четности, прямой выход счстного триггера подключен также к первому входу пятого элемента И и к выходу первого разряда устройства, второй вход пятого элемента И через второй элемент задержки подключен к выходу первого элемента задержки, а выход - к первому входу шестого элемента И и к первым входам элементов И второй группы, второй вход шестого элемента И соединен с прямым выходом триггера дискриминатора четности, а выход - через второй элемент ИЛИ совместно со вторым выходом дискриминатора четности соединен со входом первого разряда сумматора, выходы разрядов счетчика соединены с вторыми входами элементов И второй группы, выходы которых соединены со входами разрядов сумматора, начиная со второго, выход второго разряда устройства подключен к шине логического нуля, выходы разрядов сумматора являются выходами разрядов устройства, начиная с третьего.Источники информации,принятые во внимание при экспертизе 1, Авторское свидетельство СССР М 475619, кл, 6 06 Г 7/38, 1973.2. Авторское свидетельство СССР М 39907, кл. 6 06 Г/38, 1971.Техред Н. Строганова Редактор Б. Герцен Типография, пр. Сапунова, 2 Заказ 568/1 Изд,265 Тираж 779 Подписное НПО Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 475

СмотретьЗаявка

2337582, 23.03.1976

ПРЕДПРИЯТИЕ ПЯ М-5728

ПЕТРОВ ВЛАДИМИР ЭМИЛЬЕВИЧ, ТОЩЕВА ЕЛЕНА ФЕДОРОВНА

МПК / Метки

МПК: G06F 7/38

Метки: возведения, квадрат, коде, представленных, унитарном, чисел

Опубликовано: 30.04.1979

Код ссылки

<a href="https://patents.su/4-660045-ustrojjstvo-dlya-vozvedeniya-v-kvadrat-chisel-predstavlennykh-v-unitarnom-kode.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для возведения в квадрат чисел, представленных в унитарном коде</a>

Предыдущий патент: Устройство для сравнения чисел

Следующий патент: Устройство для деления двоичных чисел

Случайный патент: Способ балансировки гибких роторов