Микропрограммный процессор с восстановлением при сбоях

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

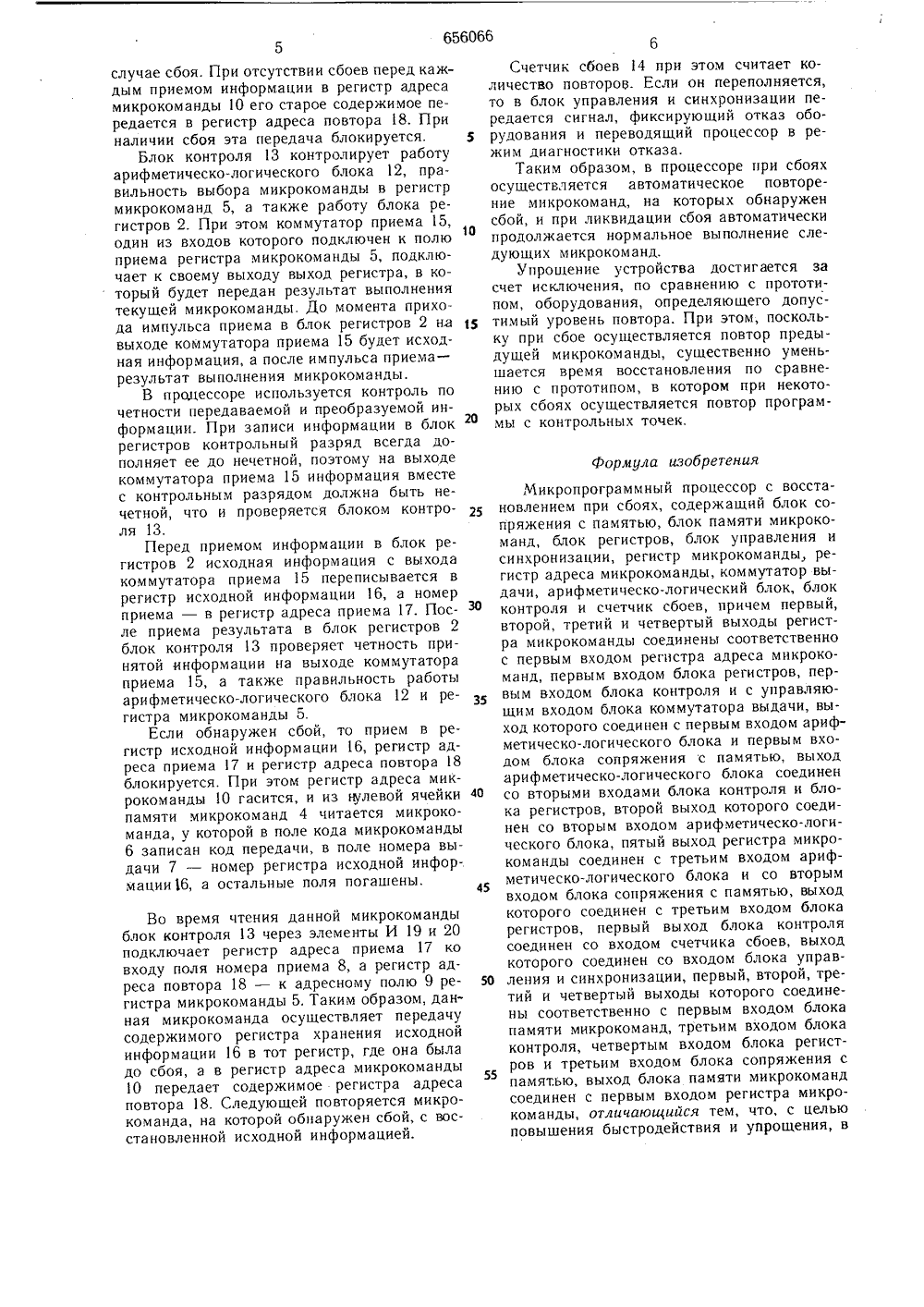

ю 656066 ОП ИСАНИ ИЗОБРЕТЕН И К АВТОРСКОМУ СВИДЕТЕЛЬСТВ Союз Советских Социалистических Реслубл(61) Дополнительное к авт. (22) Заявлено 21.12.77 (21) ид-ву -58012/18-2 1) М.Кл еб 06 Г 5/00 б 06 Г 11/00 рисоединением заявки-Государственный комнтет СССР по делам нэаоретеннй н открытнйта опубликования описания 05.04.7Изобретение относится к вычислительной технике и может быть использовано, в частности, при проектировании процессоров с контролем.Известен микропрограммный процессор с восстановлением при сбоях, содержащий блок регистров, блок сопряжения с памятью, блок управления и синхронизации, память микрокоманд с регистром микрокоманды и регистр адреса микрохоманды 11. Однако такое устройство имеет низкое быстродействие.1 ОНаиболее близким по технической сущности к изобретению является микропрограммный процессор с восстановлением при сбоях 2, содержащий блок регистров, первый выход которого через коммутатор выдачи соединен с первым входом блока сопряжения с памятью и первым входом арифметическо-логического блока, второй вход которого соединен со вторым выходом блока регистров, а выход - с первым входом блока контроля и первым входом блока регистров, второй вход которого соединен с полем приема регистра микрокоманды. Поле выдачи соединено со входом коммутатора выдачи, поле кода микрокоманды - с третьим входом арифметическо-логического блока и вторым входом блока сопряжения с памятью, поле адреса - с первым входом регистра адреса микрокоманды, выход которого соединен с первым входом памяти микрокоманд, второй вход которой соединен с первым выходом блока управления и синхронизации, а выход - со входом регистра микрокоманды, Выход последнего соединен со вторым входом блока контроля, третий вход которого соединен со вторым выходом блока управления и синхронизации, а первый выход - со входом счетчика сбоев. Выход счетчика сбоев соединен со входом блока управления и синхронизации, третий выход которого соединен с третьим входом блока сопряжения с памятью, выход которого соединен с третьим входом блока регистров, а четвертый вход - с четвертым выходом блока управления и синхронизации. Однако в известных устроиствах при обнаружении сбоя повтор микрокоманды не всегда возможен, так как имеются микрокоманды, в которых результат передается в регистр, хранивший исходный операнд.При обнаружении сбоя в таких микрокомандах в известных устройствах организуется повтор команды или повтор программы с контрольных точек, организованных при составлении программы. Это усложняет устройство и замедляет его работу.Целью изобретения является повышениебыстродействия и упрощение устройства.Поставленная цель достигается тем, чтов предложенный микропрограммный процессор с восстановлением при сбоях, содержащий блок сопряжения с памятью, блок памяти микрокоманд, блок регистров, блок управления и синхронизации, регистр микро- команды, регистр адреса микрокоманды, ком.мутатор выдачи, арифметическо-логический блок, блок контроля, счетчик сбоев, причем первый, второй, третий и четвертый выходы регистра микрокоманды соединены соответственно с первым входом регистра адреса микрокоманд, с первым входом блока регистров, с первым входом блока контроля, с управляющим входом коммутатора выдачи, выход которого соединен с первым входом арифметическо-логического блока и первым входом блока сопряжения с памятью, выход арифметическо-логического блока соединен со вторыми входами блока контроля и блока регистров, второй выход которого соединен со вторым входом арифметическологического блока, пятый выход регистра микрокоманды соединен с третьим входом арифметическо-логического блока и со вторым входом блока сопряжения с памятью, выход которого соединен с третьим входом блока регистров, первый выход блока контроля соединен со входом счетчика сбоев, выход которого соединен со входом блока управления и синхронизации, первый, второй, третий и четвертый выходы которого соединены соответственно с первым входом блока памяти микрокоманд, с третьим входом блока контроля, с четвертым входом блока регистров, с третьим входом блока сопряжения с памятью, выход блока памяти микро- команд соединен с первым входом регистра микрокомады, введены коммутатор приема, первый и второй элементы И, регистр адреса приема, регистр исходной информации, регистр адреса повтора. Первый выход блока регистров соединен с первым входом коммутатора приема, выход которого соединен с четвертым входом блока контроля и первым входом регистра исходной информации. Второй выход регистра микрокоманды соединен со вторым входом коммутатора приема и первым входом регистра адреса повтора, выход которого соединен с первым входом первого элемента И. Выход первого элемента И соединен со вторым входом регистра микрокоманды. Второй выход блока контроля соединен со вторыми входами регистра адреса приема, регистра исходной информации и регистра адреса микрокоманды и с первым входом регистра адреса повтора, выход которого соединен с первым входом второго элемента И. Выход второго элемента И соединен с третьим входом регистра микрокоманды. Выход регистра адреса микрокоманды соединен со вторым входом регистра адреса повтора, Третий выход блока контроля соединен со вторыми входами первого и второго элементов И, а выход регистра исходной информации - с пятым входом блока регистров.Структурная схема микропрограммногопроцессора показана на чертеже1 Процессор содержит блок сопряжения спамятью 1, блок регистров 2, блок управления и синхронизации 3, память микрокоманд 4, регистр микрокоманды 5 с полями кода микрокоманды 6, номера выдачи 7, номера приема 8, адресного поля 9, регистр адреса микрокоманды 10, коммутатор выдачи 11, арифметическо-логический блок 12, блок контроля 13, счетчик сбоев 14, коммутатор приема 15, регистр исходной информации 16, регистр адреса приема 17, регистр адреса повтора 18, первый элемент И 19 и второй элемент И 20.При работе процессора команды и данные считываются из памяти через блок сопряжения с памятью 1 и передаются в блок регистров 2, в котором также хранятся про- ЗО межуточные результаты вычислений. Блокуправления и синхронизации 3 организует временную диаграмму работы блока сопряжения с памятью 1, а также тактирует работу блока регистров 2 и других блоков про цессораВ процессоре используется микропрограммный принцип управления. Микрокоманды хранятся в памяти микрокоманд 4 и считываются в регистр микрокоманд 5, который имеет несколько полей, Поле кода микродв команды 6 управляет блоком сопряжения спамятью 1 и арифметическо-логическим блоком 12, один из входов которого соединен с регистром операнда блока регистров 2, а ко второму входу может быть подключен любой регистр блока регистров 2 с помощью коммутатора выдачи 11. Номер подключаемого регистраопределяется полем выдачи 7 регистра микрокоманды 5.Обработанная в арифметическо-логическом блоке 12 информация может быть 50 передана в любой регистр блока регистров2, номер которого определяется полем номера приема 8 регистра микрокоманды 5.Адресное поле 9 определяет адрес следующей микрокоманды и передается в регистр адреса микрокоманды 10, который управляет выборкой информации из памяти микрокоманд 4. Регистр адреса повтора 18 хранит адрес предыдущей микрокоманды, необходимый для повтора микрокоманды вслучае сбоя. При отсутствии сбоев перед каждым приемом информации в регистр адреса микрокоманды 10 его старое содержимое передается в регистр адреса повтора 18. При наличии сбоя эта передача блокируется.Блок контроля 13 контролирует работу арифметическо-логического блока 12, правильность выбора микрокоманды в регистр микрокоманд 5, а также работу блока регистров 2. При этом коммутатор приема 15, один из входов которого подключен к полю приема регистра микрокоманды 5, подключает к своему выходу выход регистра, в который будет передан результат выполнения текущей микрокоманды. До момента прихода импульса приема в блок регистров 2 на выходе коммутатора приема 15 будет исходная информация, а после импульса приема- результат выполнения микрокоманды.В процессоре используется контроль по четности передаваемой и преобразуемой информации. При записи информации в блок регистров контрольный разряд всегда дополняет ее до нечетной, поэтому на выходе коммутатора приема 15 информация вместе с контрольным разрядом должна быть нечетной, что и проверяется блоком контроля 13.Перед приемом информации в блок регистров 2 исходная информация с выхода коммутатора приема 15 переписывается в регистр исходной информации 16, а номер приема - в регистр адреса приема 17. После приема результата в блок регистров 2 блок контроля 13 проверяет четность принятой информации на выходе коммутатора приема 15, а также правильность работы арифметическо-логического блока 12 и регистра микрокоманды 5,Если обнаружен сбой, то прием в регистр исходной информации 16, регистр адреса приема 17 и регистр адреса повтора 18 блокируется, При этом регистр адреса микрокоманды 1 О гасится, и из нулевой ячейки памяти микрокоманд 4 читается микрокоманда, у которой в поле кода микрокоманды 6 записан код передачи, в поле номера выдачи 7 - номер регистра исходной информации 16, а остальные поля погашены. Во время чтения данной микрокоманды блок контроля 13 через элементы И 19 и 20 подключает регистр адреса приема 17 ко входу поля номера приема 8, а регистр адреса повтора 18 - к адресному полю 9 регистра микрокоманды 5. Таким образом, данная микрокоманда осуществляет передачу содержимого регистра хранения исходной информации 16 в тот регистр, где она была до сбоя, а в регистр адреса микрокоманды 10 передает содержимое регистра адреса повтора 18. Следующей повторяется микро- команда, на которой обнаружен сбой, с восстановленной исходной информацией.5 10 15 20 Счетчик сбоев 14 при этом считает количество повторов. Если он переполняется, то в блок управления и синхронизации передается сигнал, фиксирующий отказ оборудования и переводящий процессор в режим диагностики отказа.Таким образом, в процессоре при сбоях осуществляется автоматическое повторение микрокоманд, на которых обнаружен сбой, и при ликвидации сбоя автоматически продолжается нормальное выполнение следующих микрокоманд.Упрощение устройства достигается за счет исключения, по сравнению с прототипом, оборудования, определяющего допустимый уровень повтора. При этом, поскольку при сбое осуществляется повтор предыдущей микрокоманды, существенно уменьшается время восстановления по сравнению с прототипом, в котором при некоторых сбоях осуществляется повтор программы с контрольных точек. Формула изобретенияМикропрограммный процессор с восстановлением при сбоях, содержащий блок сопряжения с памятью, блок памяти микрокоманд, блок регистров, блок управления и синхронизации, регистр микрокоманды, регистр адреса микрокоманды, коммутатор выдачи, арифметическо-логический блок, блок контроля и счетчик сбоев, причем первый, второй, третий и четвертый выходы регистра микрокоманды соединены соответственно с первым входом регистра адреса микрокоманд, первым входом блока регистров, первым входом блока контроля и с управляю 35щим входом блока коммутатора выдачи, выход которого соединен с первым входом арифметическо-логического блока и первым входом блока сопряжения с памятью, выход ариф метическо-логического блока соединен 40 со вторыми входами блока контроля и блока регистров, второй выход которого соединен со вторым входом арифметическо-логического блока, пятый выход регистра микро- команды соединен с третьим входом арифметическо-логического блока и со вторым45входом блока сопряжения с памятью, выход которого соединен с третьим входом блока регистров, первый выход блока контроля соединен со входом счетчика сбоев, выход которого соединен со входом блока управ ления и синхронизации, первый, второй, третий и четвертый выходы которого соединены соответственно с первым входом блока памяти микрокоманд, третьим входом блока контроля, четвертым входом блока регистров и третьим входом блока сопряжения с памятью, выход блока памяти микрокоманд 55соединен с первым входом регистра микро- команды, отличающийся тем, что, с целью повышения быстродействия и упрощения, в656066 Составитель И. СигалРедактор Л. Утехина Техред О. ЛуговаяЗаказ 527/40 Тираж 779ЦНИИПИ Государственного комитета Спо делам изобретений и открыт1 3035, Москва, Ж, Раушская наб.,филиал ППП Патент, г. Ужгород, ул. П орректор Е. ДичинскаяодписноеР 4/ ектная,него введены коммутатор приема, первый и второй элементы И, регистр адреса приема, регистр исходной информации и регистр адреса повтора; первый выход блока регистров соединен с первым входом коммутатора приема, выход которого соединен с четвертым входом блока контроля и первым входом регистра исходной информации; второй выход регистра микрокоманды соединен со вторым входом коммутатора приема и первым входом регистра адреса повтора, выход которого соединен с первым входом первого элемента И; выход первого элемента И соединен со вторым входом регистра микрокоманды; второй выход .блока контроля соединен со вторыми входами регистра адреса приема, регистра исходной информации и регистра адреса микрокоманды и первым входом регистра адреса повтора, выход которого соединен с первым входом второго элемента И; выход второго элемента И соединен с третьим входом регистра микрокоманды; выход регистра адреса микрокоманды соединен со вторым входом регистра адреса повтора; третий выход блока контроля соединен со вторыми входами первого и второго элементов И, а выход регистра исходной информации - с пятым входом блока регистров. Источники информации, принятые во внимание при экспертизе1, Патент Англии1444175, кл, 6 4 А,15 1976.2. Патент США3618042,кл. 340 - 172,8, 1972.

СмотретьЗаявка

2558012, 21.12.1977

ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ПРЕДПРИЯТИЕ ПЯ Г-4128

ДОЛКАРТ ВЛАДИМИР МИХАЙЛОВИЧ, ПУРЭ РУДОЛЬФ РОБЕРТОВИЧ, СТЕПАНОВ ВИКТОР НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: восстановлением, микропрограммный, процессор, сбоях

Опубликовано: 05.04.1979

Код ссылки

<a href="https://patents.su/4-656066-mikroprogrammnyjj-processor-s-vosstanovleniem-pri-sboyakh.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный процессор с восстановлением при сбоях</a>

Предыдущий патент: Многоканальное устройство тестового контроля цифровых узлов электронных вычислительных машин

Следующий патент: Устройство для моделирования сетевого графика

Случайный патент: Вибратор для предотвращения слипания угля и других обезвоженных материалов в выгрузочной камере непрерывно действующих осадительных центрифуг