Имитатор ошибок в групповом тракте цифровых систем передачи

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 646459

Автор: Селезнева

Текст

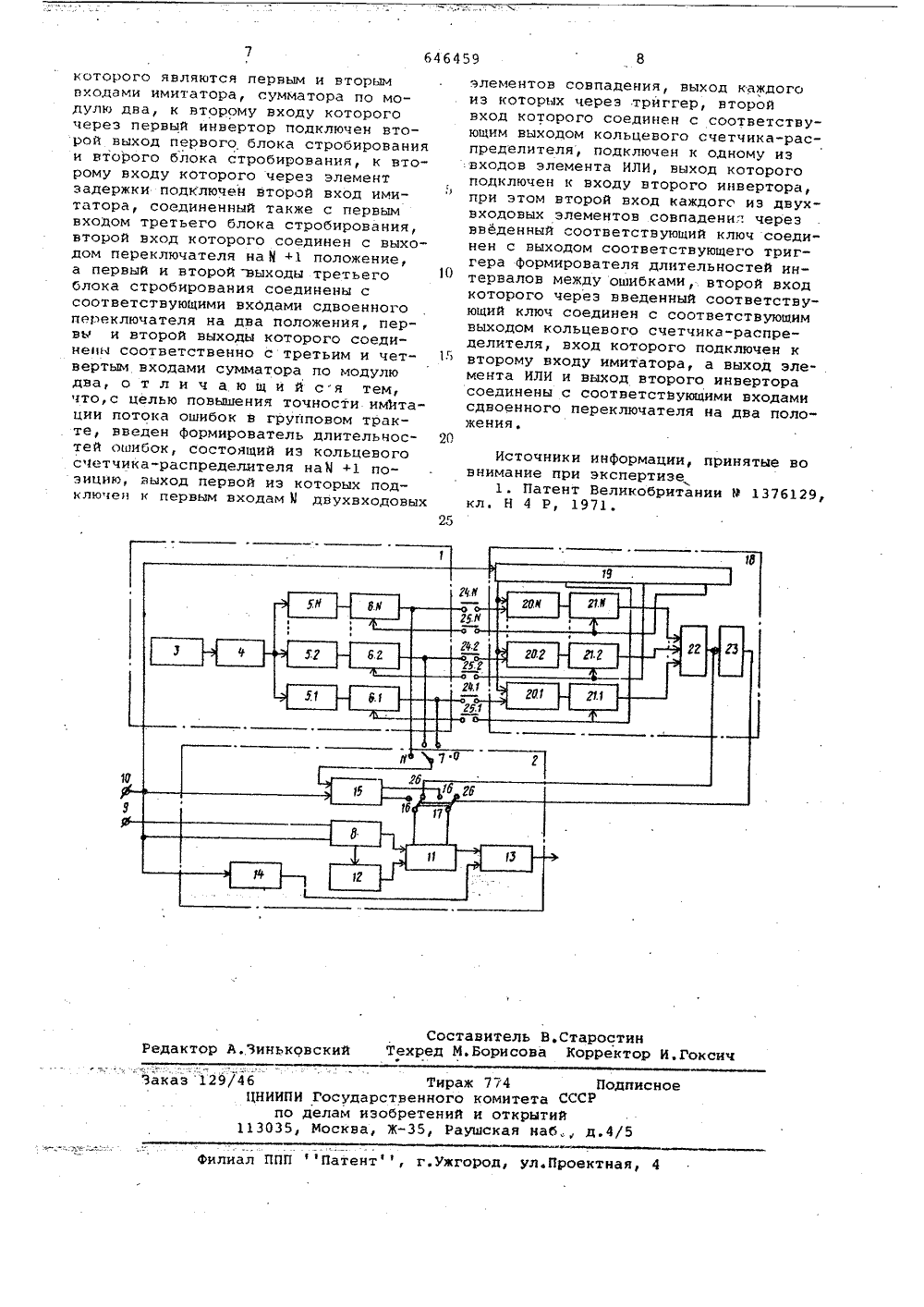

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советскнк Социалистических Республик(н 1646459 61) Дополнительное к авт. свиа(22) 3 лено 04,0 б 7 б (23) 23 б 8002/18-0 М. Кл Н 04 Ь 23/ Н 04 В 3/ пением заявкис при рственный комнтеСССРлам изобретенийи открытийорите иковано Об 0279 Бюллетень5 Щ УЛК 621.327.8 1088. 8) Лата опубликования описания 05027(72) Автор изобретения Селезне Ь:)ТБ3:ОРП 3) ИМИТАТОР ОШИБОК В ГРУППОВОМ ТРАКТ ЦИФРОВЫХ СИСТЕМ ПЕРЕДАЧИИзобретение относится к электросвязи н может быть использовано для проведения настройки и испытаний цифровых систем передачи.Известен имнтатор ошибок в групповом тракте цифровых систем передачи, содержащий формирователь длительностей интервалов между ошибками и блок для ввода ошибок в цифровой поток, причем формирователь длительности интервалов между ошибками состоит иэпоследовательно соединенных генератора модулирующего сигнала и делителя напряжения, выход которого подключен к М цепям, каждая из которыхсостоит из последовательно соединенных порогового блока и триггера, выход которого соединен с соответствующим входом переключа- З) теля на И +1 положение, а блок для ввода ошибок в цифровой поток состоит из последовательно соединенных первого блока стробирования, первый и второй входы которого являются И первым и вторым. входами имитатора, сумматора по модулю два, к второму входу которого через первый инвертор подключен второй выход первого блока стробирования, и второго бло- а 0 ка стробирования, к второму входу которого через элемент задержки подключен второй вход имитатора, соединенный также с первым входом третьего блока стробирования, второй вход которого соединен с выходом переключателя на М +1 положение, а первый и второй Выходы третьего блока стробирования соединены с соответствующими входами сдвоенного переключателя на два положения, первый н второй выходы которого соединены соответственно с третьим и четвертым входами сумматора по модулю два 11,Однако известный имитатор ошибок в групповом тракте цифровых систем передачи имеет низкую точность имитации потока ошибок в групповом тракте.Целью изобретения является повышение точности имитации потока ошибок в групповом тракте.Для этого в имитатор ошибок в групповом тракте цифровых систем передачи, содержащий Формирователь длительностей интервалов между ошибками Н блок ввода ошибок в цифровой поток, причем формирователь длительностей интервалов между ошибками состоит"из последовательно соединенных гене. - ратора модулирующего сигнала и делителя напряжения, выход которого подключен к И цепям, каждая з которых состоит из последовательно соединенных порогового блока и триггера, выход которого соединен с соответствующим входом переключателя на М +1 положение, а блок ввода ошибок в цифровой поток состоит из последовательно соединенных первого блока стробирования, первый и второй входы которого являются первым и вторым входами имитатора, сумматора по модулю два, к второму входу которого через первый инвертор подключен второй выход первого блока стробирования, и второгоблока стробирования, к второму входу которого через элемент задержкиподключен второй вход имитатора, соединенный также с первым входом третьего блока стробирования, второй входкоторого соединен с выходом переключателя на Я +1 положение, а первый ивторой выходы третьего блока стробирования соединены с соответствующимивходами сдвоенного переключателя надва положения, первый и второй выходыкоторого соединены соответственно стретьим и четвертым входами сумматора по модулю два, введен формирователь длительностей ошибок, состоящийиэ кольцевого счетчика-распределителяна 0 +1 .позицию, выход первой из кото"рых подключен к первым входам Й двухвходовых элементов совпадения, выходкаждого из которых через триггер,второй, вход которого соединен с соответствующим выходом кольцевого счетчика-распределителя, подключен к одному из входов элемента ИЛИ, выходкоторого подключен к входу второгоинвертора, при этом второй вход каждого из двухвходовых элементов совпадения через введенный соответствующий ключ соединен с выходом соответствующего триггера Формирователя длительностей интервалов между ошибками,второй вход которого через введенныйсоответствующий ключ соединен с соответствующим выходом кольцевого счетчика-распределителя, вход которогоподключен к второму входу имитатора,а выход элемента ИЛИ и выход второгоинвертора соединены с соответствующими входамй сдвоенного переключателя на два положения.На чертеже приведена структурнаяэлектрическая схема имитатора,Имитатор ошибок в групповом тракте цифровых систем передачи содержитФормирователь 1 длительностей интервалов между ошибкгми и блок 2 дляввода ошибок в цифровой поток, причем формирователь 1 длительностейинтервалов между ошибками состоитиэ последовательно соединенныхгенератора 3 модулирующего сигнала и делителя 4 напряжения, вход которого подключен к 8 цепям, причем-я цепь состоит из последовательносоединенных порогового блока 5,Ьи триггера 6,1, где- 1,2 ЙВыход триггера 6, соединен с соответствующим входом переключателя 7найф 1 положение, Блок 2 для вводаошибок в цифровой поток состоит изпоследовательно соединенных первого блока стробирования 8, первый ивторой входы которого являются первым 10 и вторым входами 9 и 10 имитатора,сумматора по модулю два 11, к второмувходу которого через первый инвертор12 подключен второй выход первого.блока стробирования 8, и второго бло ка стробирования 13, к второму входукоторого через элемент задержки 14подключе, второй вход 10 имитатора.Второй вход 10 имитатора соединентакже с первым входом третьего блока 20 стробирования 15, второй вход которого соединен с выходом переключателя 7на 8 +1 положение, а первый и второйвыходы третьего блока стробирования15 соединены с соответствующими входами 16 сдвоенного переключателя 17на два положения, первый и второйвыходы которого соединены соответственно с третьим и четвертым входамисумматора по модулю два 11, Кроме 30 того, имитатор ошибок в групповомтракте цифровых систем передачи содержит Формирователь длительностейошибок 18, состоящий из кольцевогоначетчика-распределителя 19 наИ +1позицию, выход первой из которыхподключен к первым входам М двухвходовых элементов совпадения 20.120.Й, а выход двухвходового элементасовпадения 20.1, где-1,2 ,И, 40через триггер 21, второй вход которого соединен с соответствующимвыходом кольцевого счетчика-распределителя 19, подключен к одному извходов элемента ИЛИ 22, выход которого подключен к входу второго инвертора 23, при этом второй вход двух 4 г, входового элемента совпадения 20.1через введенный соответствующий ключ24, соединен с выходом соответствующего триггера 6, формирователя 1длительностей интервалов между ошибками,второй вход которого через введенный соответствующий ключ 25.соединен с соответствующим выходомкольцевого счетчика-распределителя19, вход которого подключен к второ му входу 10 имитатора, а выход эле мента ИЛИ 22 и выход второго инвертора 23 соединены с соответствующимивходами 26 сдвоенного переключателя17 на два положенияИмитатор ошибок работает следующим образом.При формировании потока ошибок, 6 содержащего импульсы, длительность) 1 О 20 25 3( 5) Ц Формула изобретения 45 гг )з) 60 которых равна одному периоду тактовой частоты искажаемого цифровогопотока, ключи 24,1 и 25.1 замкнуты,а ключи 24,2 - 24.Й и 25.2 - 25.0разомкнуты, Сдвоенный переключатель17 на дна положения замкнут на входы26, а переключатель 7 на М +1 положение находится н положении О. Сигналс выхода генератора 3 модулирующегосигнала через делитель 4 напряженияпоступает на вход порогового блока5.1, на выходе которого формируетсяимпульсная последовательность, определяемая пересечением уровнейвходного модулирующего напряжения ипороГом срабатывания порогового блока 5,1. Через ключ 24,1 сигнал с выхода триггера 6.1 поступает на второйвход двухвходового элемента совпадения 20.1, на выходе которого в моментсовпадения сигнала с выхода триггера 6,1 и импульса первой позициикольцевого счетчика-распределителя19 Формируется сигнал, запускающийтриггер 21.1. Установка в 0 триггеров 6,1 и 21.1 производится импульсом второй позиции кольцевого счетчика-распределителя 19,Таким образом, длительность импульса, сформированного на выходетриггера 21.1, равна одному периодутактовой частоты искажаемого цифрового потока. Этот сигнал поступает наодин из входов элемента ИЛИ 22,Аналогичным образом Формируютсяпотоки ошибок, содержащие импульсыдлительностью в 2, 3, ,И,)периодовтактовой частоты искажаемого цифрового потока,При замыкании ключей 241 - 24,йи 25.1 - 25.Й на выходе элементаИЛИ 22 формируется поток ошибок., содержащий импульсы длительностью в-1, 2, , М периодов тактовой частоты,Частота появления импульсов н потокеошибок и их длительности определяются как уровнем модулирующего сигнала,так и значениями порогов срабатывания пороговых элементов 5,1 - 5.Мкоторые управляют формированием импульсон определенной длительностив потоке ошибок,В блоке ввода ошибок в цифровойпоток 2 сумматор по модулю два 11осуществляет поразрядное суммирование по модулю два цифрового потокасистемы передачи и потока ошибокНа третий и четвертый входы сумматора по модулю два через сдвоенныйпереключатель 17 подается поток ошибок в прямом и инверсном видах,вырабатываемый третьим блоком стробирования 15 или элементом ИЛИ 22. Напервый и второй входы су)юатора помодулю два 11 подается прямой и инверсный потоки системы предачи свыходов первого блока стробирования8 и первого инвертора 12, На первый и нторой входы первого блока строгрования 8 с первого н второго вход9 и 10 имитатора поступают соответственно цифровой сигнал и сигнал тактовой частоты. Сигнал с выхода сумматора по модулю два 11 поступает напервый .вход второго блока стробирования 13, на второй вход которогочерез элемент задержки 14 подаетсясигнал тактовой частоты с второговхода 10 имитатора. Элемент задержкв14 служит для компенсации временныхзадержек, вносимых элементами имитатора,В частном случае имитатор можетФормировать потоки ошибок, в которыхдлительности импульсов и интервалымежду ними распределены по нормальному закону. При работе в этом режимеключи 241 - 24.Н и 25,1 - 25,Юразомкнуты, переключатель 7 находитсяв одном из М положений, а сдвоенныйпереключатель 17 находится в положении,когда замкнуты его входы 16. Сигналс выхода генератора 3 модулирующегосигнала через делитель 4 напряженйяПоступает на входы пороговых блоков5.1 - 5.И, имеющих различные порогисрабатынания. С выходов пороговыхблоков 5.1 - 5,Н сигналы поступают на счетные входы триггеров6.1 - б,я с выхода одного из которых через переключатель 7 сигнал подается на второй вход третьего блокастробирования 15, первый вход которого явЛяется вторым входом 10 имитатора. Предложенный имитатор ошибок в групповом тракте цифровых систем передачи отличается повышенной точностью имитации потока ошибок и позволяет Формировать этот поток по любому заданному закону с любым распределением длительностей пачек ошибок,Имитатор ошибок н групповом тракте цифровых систем передачи, содержащий Формирователь длительностей интервалов между ошибками и блок ввода ошибок в цифровой поток, причем Формирователь длительностей интервалов между ошибками состоит иэ последовательнО соединенных генератора модулирующего сигнала и делителя напряжения, выход которого подключен кцепям, каждая из которых состоит из последовательно соединенных порогового блока и триггера, выход которого соединен с соответствующим входом переключателя на 14.1 положение, а блок ввода ошибок в цифровой поток состоит из последовательно соединенных первого блока стробиронания, первый и второй нХоды646459 Составитель В,Старостинехред М.Борисова Корректор И,Гокс Редактор АЗиньковс Тираж ПИ Государственного к о делам изобретений и 5, Москва, Ж, Рауш 74митета СССоткрытийкая наб. Подпис Заказ 129/46ЦНИИ 5 Филиал ППП Патент, г.ужгород, ул.Проектная, 4 которого являются первым и вторым входами имитатора, сумматора по модулю два, к второму входу которого через первый инвертор подключен второй выход первого блока стробирования и второго блока стробирования, к второму входу которого через элемент задержки подключен второй вход имитатора, соединенный также с первым входом третьего блока стробирования, второй вход которого соединен с выходом переключателя на 8 +1 положение, а первый и второй -выходы третьего блока стробирования соединены с соответствующими вхОдами сдвоенного переключателя на два положения, первы и второй выходы которого соединены соответственно с третьим и четвертым входами сумматора по модулю два, о т л и ч а ю щ и й с я тем, что,с целью повышения точности имитации потока ошибок в групповом трак. те, введен формирователь длительностей ошибок, состоящий иэ кольцевого счетчика-распределителя най +1 позицию, выход первой из которых подключен к первым входам И двухвходовых элементов совпадения, выход каждогоиз которых через триггер, второйвход которого соединен с соответствующим выходом кольцевого счетчика-распределителя, подключен к одному из:входов элемента ИЛИ, выход которогоподключен к входу второго инвертора,при этом второй вход каждого из двухвходовых элементов совпадени черезвведенный соответствующий ключ соеди"нен с выходом соответствующего триггера формирователя длительностей интервалов между ошибками, второй входкоторого через введенный соответствующий ключ соединен с соответствующимвыходом кольцевого счетчика-распределителя, вход которого подключен квторому входу имитатора, а выход эле- .мента ИЛИ и выход второго инверторасоединены с соответствующими входамисдвоенного переключателя на два положения,Д( Источники информации, принятые вовнимание при экспертизе1. Патент Великобритании Р 1376129,кл. Н 4 Р, 1971.26

СмотретьЗаявка

2368002, 04.06.1976

ПРЕДПРИЯТИЕ ПЯ М-5619

СЕЛЕЗНЕВА ВАЛЕНТИНА ПЕТРОВНА

МПК / Метки

МПК: H04L 23/00

Метки: групповом, имитатор, ошибок, передачи, систем, тракте, цифровых

Опубликовано: 05.02.1979

Код ссылки

<a href="https://patents.su/4-646459-imitator-oshibok-v-gruppovom-trakte-cifrovykh-sistem-peredachi.html" target="_blank" rel="follow" title="База патентов СССР">Имитатор ошибок в групповом тракте цифровых систем передачи</a>

Предыдущий патент: Устройство для передачи информации

Следующий патент: Стартстопный передатчик

Случайный патент: Устройство для очистки гусеницы транспортного средства