Устройство для контроля логических блоков цвм

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 633019

Автор: Быданов

Текст

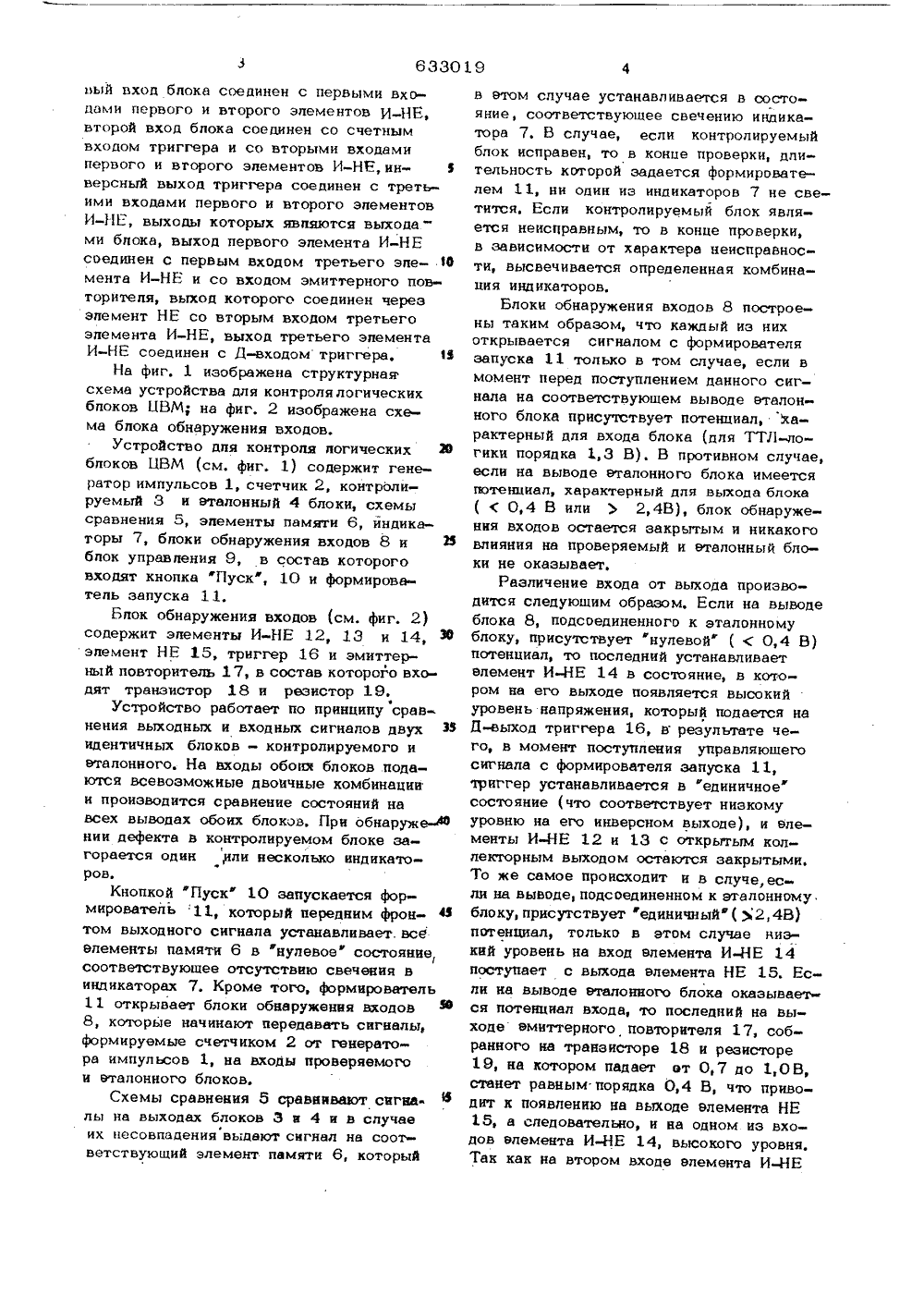

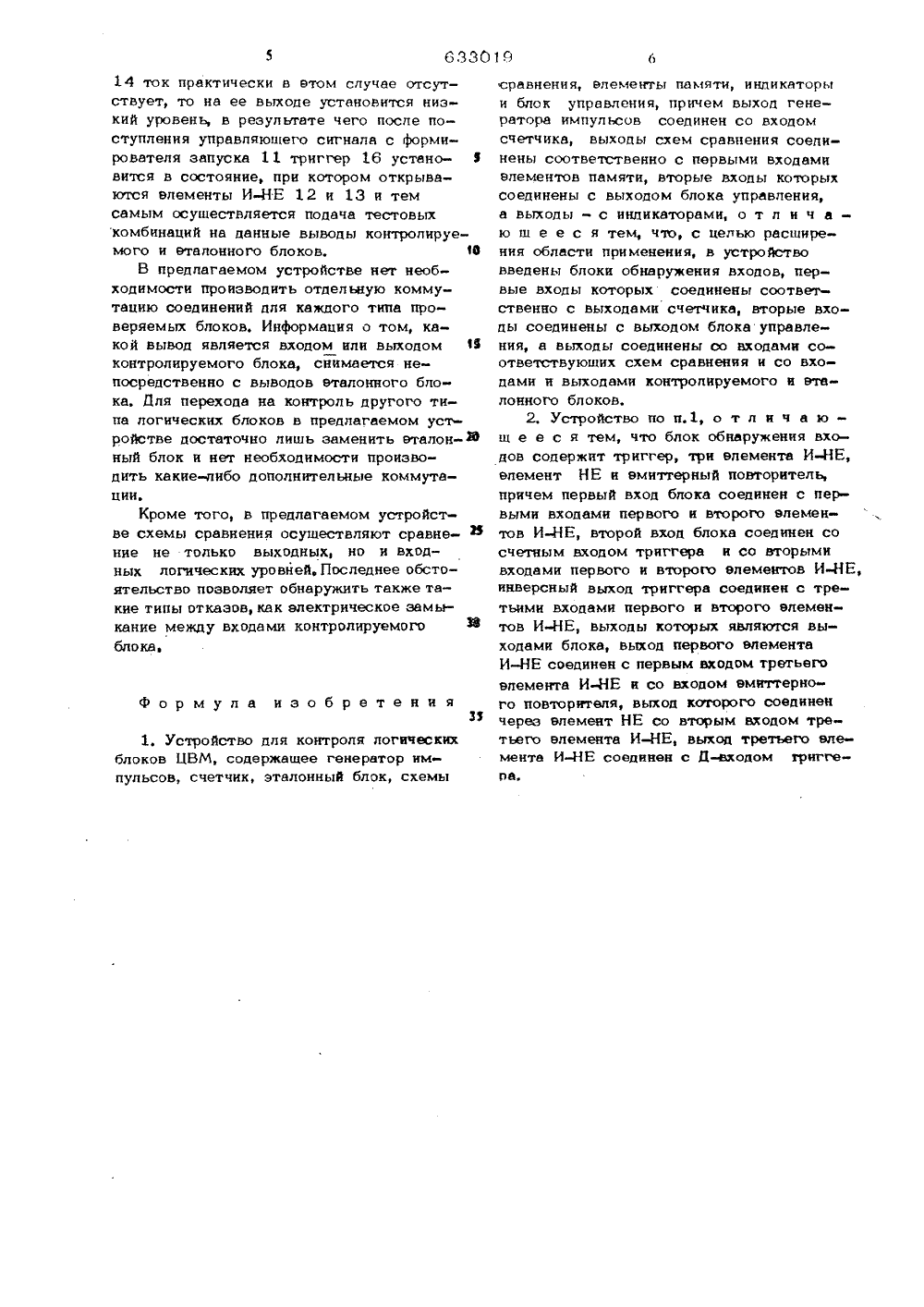

Союз Советских Социалистичеснии РеспубликОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВМДЕТЕЛЬСТВУ 11633019(5) М. Кл, 5 06 Г 11 98 926 18-2 соединением заявкиосударстееннмй номиСоеета Министрое СССпо делам изобретениин открытий(45) Дата опубликования описания 28.1 53) Ъ 68 1,326 .7 (088.8 2) Автор изобрет В. В, Бьщанов(71) Заяви 54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧ БЛОКОВ 1 ВМИзобрвычнсспопьзов В известных устройствах дпя проверки каждого типа блоков необходимо иметь карты вкпючення коммутационных шнуров, в соответствии с которыми необходимо осуществлять соединения с выхода счетчика проверяемого н эталонного блоков. Данная процедура существенно усложняет процесс контроля рвзпнчных типов блоков.11 епью настоящего изобретенияявляеч- ся рвщнрение области применения устройства за счетобеспечения возможности контроля различных типов блоков.Постввленная цель достигается тем к автомат может бытьправностн ци ровых контроля и нп действия Извес гнческнх которого ненни снгнаного блоков н Ф блок, схемы пов проверяемого которое содержит сравнения н нндн эта тало ры аиболе лнзким т изобрете хническим решен ем к данному ройство для к ляется устских блоков онтропяашее генонный б огич в бнару- сое- счетЦВМ, содержсчетчик, этания, элемент импул ьсов, мы сравневторы н бпо ен к, схе индик инены памя чика, в дом бло правления,ульсов соед дивыходы схе сравнения соеди первыми входам ны соот эпеменсравне ветственно стов памяти,пннены с вых лнр м, чт жит три НЕ нэм выходы(22) За я влено 23.08. 76 етение относится лнтельной технике вно для контроля интегральных сх тно устройство д бпокоа ЦВМ при .основан на срав вчем выход генератораен со входом счетчика торые входы которых соеодом блока управления, внднкаторами стройство введены блокиодов, первые входы которыхсоответственно с выходамиторые входы - соединены ска упрввлен 1 гя, а выходывходами соответствующих я н со входамн н выходами конт ого н эталонного блоков, а такжеблок обнаружения входов содерггер, три элемента И-НЕ элемент иттерный повторитель, причем пералый вход блока соединен с первыми входами первого и второго элементов И-НЕ,второй вход блока соединен со счетнымвходом триггера и со вторыми входамипервого и второго элементов И-НЕ,ин- Уверсный выход триггера соединен с третьими входами первого и второго элементовИ-НЕ, выходы которых являются выходами блока выход первого элемента И-НЕсоединен с первым входом третьего эле- Фмента И-НЕ и со входом эмиттерного повторителя, выход которого соединен черезэлемент НЕ со вторым входом третьегоэлемента И-НЕ, выход третьего элементаИ-НЕ соединен с Д-входом триггера, 1На фиг, 1 изображена структурнаясхема устройства для контролялогическихблоков ЦВМ; на фиг. 2 изображена схема блока обнаружения входов.Устройство для контроля логических Мблоков ЦВМ (см. фиг. 1) содержит генератор импульсов 1, счетчик 2, контролируемый 3 и эталонный 4 блоки, схемысравнения 5, элементы памяти 6, йндикаторы 7, блоки обнаружения входов 8 и Иблок управления 9, в состав котороговходят кнопка Пуск, 10 и формирователь запуска 11.Блок обнаружения входов (см. фиг. 2)содержит элементы И-НЕ 12, 13 и 14,элемент НЕ 15, триггер 16 и эмиттерный повторитель 17, в состав которого входят транзистор 18 и резистор 19,Устройство работает по принципу сравнения выходных и входных сигналов двух Зфидентичных блоков - контролируемого иэталонного. На входы обоих блоков подаются всевозможные двоичные комбинациии производится сравнение состояний навсех выводах обоих блоков, При обнаруже нии дефекта в контролируемом блоке загорается один или несколько индикаторов,Кнопкой Пуск 10 запускается формирователь 11, который передним фрон- ффтом выходного сигнала устанавливает. всеэлементы памяти 6 и нулевое" состояниеIсоответствующее отсутствию свечения виндикаторах 7, Кроме того, формирователь11 открывает блоки обнаружения входов фе8, которые начинают передавать сигналы,формируемые счетчиком 2 от генератора импульсов 1, на входы проверяемогои эталонного блоков.Схемы сравнения б сравнивают сигна- флы на выходах блоков 3 и 4 я в случаеФих несовпадения выдают сигнал на соответствующий элемент памяти 6, который в этом случае устанавливается в состояние, соответствующее свечению индикатора 7, В случае, если контролируемыйблок исправен, то в конце проверки, длительность которой задается формирователем 11, ни один из индикаторов 7 не светится, Если контролируемый блок является неисцравным то и конце проверки,в зависимости от характера неисправности, высвечивается определенная комбинация индикаторов,Блоки обнаружения входов 8 построены таким образом, что каждый из нихоткрывается сигналом с формирователязапуска 11 только в том случае, если вмомент перед поступлением данного сигнала на соответствующем выводе эталонного блока присутствует потенциал, характерный для входа блока (для ТТЛ-логики порядка 1,3 В). В противном случае,если на выводе эталонного блока имеетсяпотенциал, характерный для выхода блока(0,4 В или ) 2,4 В), блок обнаружения входов остается закрытым и никакоговлияния на проверяемый и эталонный блоки не оказывает,Различение входа от выхода производится следуюшим образом, Если на выводеблока 8, подсоединенного к эталонномублоку, присутствует "нулевой" ( ( 0,4 В)потенциал, то последний устанавливаетэлемент И-НЕ 14 в состояние, в котором на его выходе появляется высокийуровень напряжения который подается наД-выход триггера 16, в результате чего, в момент поступления управляющегосигнала с формирователя запуска 11,триггер устанавливается в "единичное"состояние (что соответствует низкомууровню на его инверсном выходе), и элементы И-НЕ 12 и 13 с открытым коллекторным выходом остаются закрытыми,То же самое происходит и в случе,если на выводе подсоединенном к эталонномублоку, присутствует фединичный ( . 2,4 В)потенциал, только в этом случае низкий уровень на вход элемента И-НЕ 14поступает с выхода элемента НЕ 15. Если на выводе эталонного блока оказывается потенциал входа, то последний на выходе эмиттерного повторителя 17, собранного иа транзисторе 18 и резисторе19, на котором падает эт 0,7 до 1,0 В,станет равным порядка 0,4 В, что приводит к появлению на иьжоде элемента НЕ15, а следовательно, и на одном из входов элемента И-НЕ 14, высокого уровня,Так как на втором входе элемента И-НЕ14 ток практически в этом случае отсутствует то на ее выходе установится низкий уровень, в результате чего после поступления управляющего сигнала с формирователя запуска 11 триггер 16 устано- Увится в состояние, при котором открываются элементы И-НЕ 12 и 13 и темсамым осушествляется подача тестовыхкомбинаций на данные выводы контролируемого и эталонного блоков. 16В предлагаемом устройстве нет необходимости производить отдельную коммутацию соединений для каждого типа проверяемых блоков, Информация о том какой вывод является входом или выходом 1контролируемого блока, снимается непосредственно с выводов эталонного блока. Для перехода на контроль другого типа логических блоков в предлагаемом усчройстве достаточно лишь заменить эталон-Еный блок и нет необходимости производить какие-либо дополнительные коммутации,Кроме того, в предлагаемом устройстве схемы сравнения осушествляют сравне- ффние не только выходных, но и входных логических уровней. Последнее обстоятельство позволяет обнаружить также такие типы отказов, как электрическое замыкание между входами контролируемогоблока,формула изобретенияИ1, Устройство для контроля логических блоков ЦВМ содержащее генератор импульсов, счетчик, эталонный блок, схемы сравнения, элементы памяти, индикаторыи блок управления, причем выход генератора импульсов соединен со входомсчетчика, выходы схем сравнения соединены соответственно с первыми входамиэлементов памяти, вторые входы которыхсоединены с выходом блока управления,а выходы - с индикаторами, о т л и ч аю ш е е с я тем что с целью расширения области применения, в устройствовведены блоки обнаружения входов, первые входы которых соединены соответственно с выходами счетчика, вторые входы соединены с выходом блока управления, а выходы соединены со входами соответствуюших схем сравнения и со входами и выходами контролируемого и эталонного блоков,2, Устройство по п.1, о т л и ч а юш е е с я тем, что блок обнаружения входов содержит триггер, три элемента И-НЕ,элемент НЕ и эмиттерный повторитель,причем первый вход блока соединен с первыми входами первого и второго элементов И-НЕ, второй вход блока соединен сосчетным входом триггера и со вторымивходами первого и второго элементов И-НЕ,инверсный выход триггера соединен с третьими входами первого и второго элементов И-НЕ, выходы которых являются выходами блока, выход первого элементаИ-НЕ соединен с первым входом третьегоэлемента И-НЕ и со входом эмиттерного повторителя выход которого соединенчерез элемент НЕ со вторым входом третьего элемента И-НЕ, выход третьего элемента И-НЕ соединен с Д-еходом триггера,633019 Составительов Техрел Е. рыловаа Корректор Н, С Редактор П Тираж 784Подписное рственного комитета Совета Мини по делам изобретений и открытий ква, Ж, Раушская наб., д, 4/5 з 6555/39БНИИПИ Гос в СС 113035,илиал ППП "Патент, г. Ужгород, ул. Проектная,

СмотретьЗаявка

2398926, 23.08.1976

ПРЕДПРИЯТИЕ ПЯ Г-4115

БЫДАНОВ ВАЛЕРИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 11/277

Метки: блоков, логических, цвм

Опубликовано: 15.11.1978

Код ссылки

<a href="https://patents.su/4-633019-ustrojjstvo-dlya-kontrolya-logicheskikh-blokov-cvm.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для контроля логических блоков цвм</a>

Предыдущий патент: Устройство для контроля работоспособности счетчика

Следующий патент: Устройство для контроля двух параллельно работающих счетчиков

Случайный патент: Глушитель шума