Параллельно-последовательный аналогоцифровой преобразователь

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 573872

Автор: Беломестных

Текст

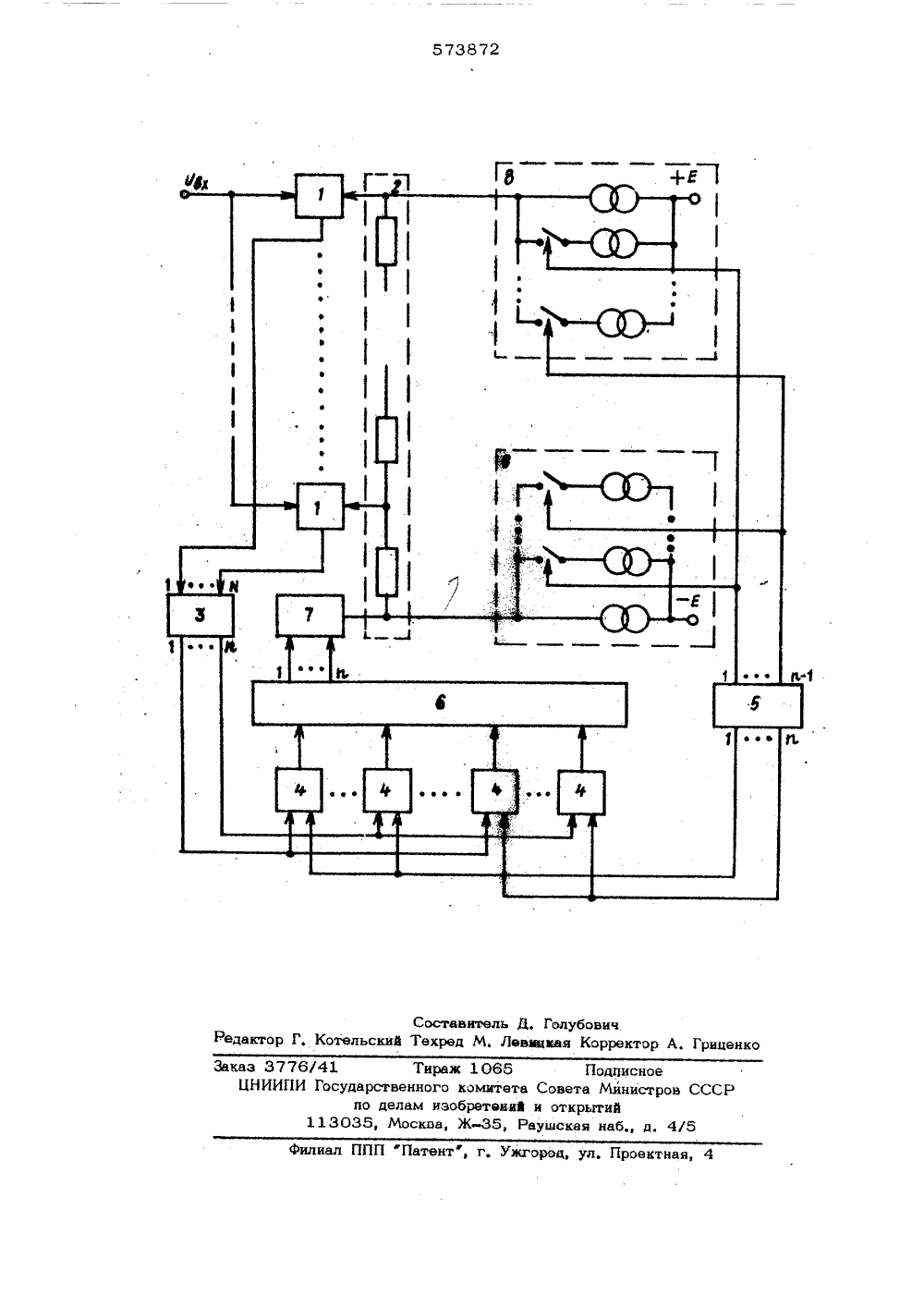

(и)573872 О П И С А ЙЯ"Е" ИЗОБРЕТЕНИЯ Союз Советских Социалистических Республик(45) Дата опубликования описания 20,10.77(61) М. Кл,я Н 03 К 13/08 Государственный коиитет Совета Министров СССР пе делам изобретений и открытий(71) Заявители Институт автоматики и электрометрии Сибирского отделенияАН СССР и Новосибирский государственный университет(54) ПАРАЛЛЕЛЬНО-ПОСЛБДОВАТЕЛЬНЫЙАНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ Изобретение относится к электроизмерительной и вычислительной технике и может быть использовано при исследованиях физики плазмы, радиолокационных сигналов и в ряде других случаев, когда требуются приборы, позволяющие автоматически измерять быстро протекающие процессы в реальном масштабе времени.Известен аналого-цифровой параллельно- последовательный преобразователь, содержаший блок компараторов, выходы которых подключены к шифратору, делитепь напряжения, включенный между одними входами компараторов и выходами цифро-аналоговых преобразователей, управляемых регистрами, распределитель импульсов, элементы НЕ и две группы элементов И, причем первые входы элементов И одной группы присоединены.к выходам элементов НЕ, входы которых подключены к выходам шифратора, йО выходы элементов И второй группы соединены с нулевыми входами регистра одного из цифро-аналоговых преобразователей, а единичные входы этого регистра - с выходами распределителя импульсов 11.26 Недостатком такого преобразователя является сравнительно большое количество оборудования и относительно низкие быстродействие и точность.Известен также аналого-цифровой преобразователь (АЦП), содержаший блок компараторов, одни из входов которых объединены шиной, соединенной с входом АЦП, а другие входы подключены к делителю напряжения, состоящему из одинаковых резисторов, число которых равно числу компараторов, Свободный вывод нижнего резистора подключен к обшей шине прибора, а верхнего - к входу младшего компаратора и выходу цифро-аналогового преобразователя (ЦАП). Верхний зажим делителя напряжения подключен к входу старшего компаратора и к выходу управляемого генератора тока. Выход каждого компаратора через шифратор соединен с одним из входов соответствуюшего элемента И. Вторые входы элементов И подключены к распределителю импульсов. Эти же шины распределителя соединены с входом управляемого генератора тока. Выходы элементов И подключепы к входу регистра, а выход последнего -к входу ЦАП 2,В этом преобразователе, как и в уФмянутом выше, сопротивление нагрузки ЦАПфункционально входит в состав делителя и бопределяет номинал его резисторов, изменение которого поэтому невозможно без нарушения работоспособности АЦП. Междутем от номинала резисторов делителя зависит число компараторов, обусловливаю Ощее в свою очередь воэможность увеличениябыстродействия АЦП. В известных преобразователях с увеличением числа компараторовувеличивается общее сопротивление делителя, что приводнт к возрастанию статнчес- Икой погрешности за" счет входных токовкомнараторов и к увеличению постояннойвремени их входной цепи, особенно при ра боте АЦП в условиях иэмейяющихся температур, сОЦелью изобретения является повышениебыстродействия и точности преобразователя.Поставленная цель достигается тем, чтов предлагаемый аналого-цифровой параллельно-последовательный преобразователь, содер- бжащий компараторы, выходы которых подключены к шифратору, соединенному с первымивходами алементов И, вторые входы которыхподключены к распределителю импульсов,делитель напряжения, включенный между од- Оними входами омпараторов и выходамиуправляемого генератора тока, регистр, подключенный к выходам елементов И, и цифроаналоговый преобразователь, соединенныйс выходом регистра, введен дополнительныйуправляемый генератор тока, входы которогоподключены к выходам распределителя импульсов, а выход - к нижнему зажиму делителя напряжения.На чертеже приведена функциональная схе-фома предлагаемого параллельно-последовательного АЦП.АЦП содержит Р 1 компараторов 1, однивходы которых присоединены к источникуизмеряемого сигнала, а другие - к выходамделителя 2 напряжения. Выходы компараторов 1 подключены к входу шифратора 3, выходы которого соответственно соединеныс одними из входов элементов И 4, Вторыевходы элементов И 4 подключены к выхоГ 7дам распределителя 5 импульсов, а выходкаждого элемента И - к одному иэ установочных входов триггеров регистра 6. Выход регистра 6 соединен с входом ЦА П 7, а выход последнего подключен к входу делители 2, К концам делителяодключены управляемые генераторы тока 8, 9, входы которых присоединены к распределителю 5 импульсовВыход 11 ЛП 7 может быть присоединен к6 О любой точке делителя, при этом икеняетсяисходное состояние триггеров регистра,оно должно быть строго определено для каждого случая.Параллельно-последовательный АЦП работает следующим образом.В исходном состоянии триггеры регистра6 находится в состоянии "О, соответственно и выходное напряжение ЦАП 7 тоже равно нулю. Генераторы 8, 9 вырабатываютмаксимальные по величине токи, причем этитоки равны между собой и противоположныпо направлению. Под воздействием токов генераторов 8, 9, протекающих через делитель 2, пороги срабатывания компараторов1 устанавливаются такими, что весь диапазон изменения входной величины оказывается,разбит на 2 " эон, где й, - число параллельно определяемых двоичных разрядов. По состоянию компараторов 1 определяется, в какой из эон находится входной сигнал.Шифратор 3 преобразует Я -разрядныйунитарный код в, в -разрядный двоичный,причем И 1 оуй ( М+ 1). Импульсами распределителя 5 через посредство элементовИ 4 и код старших разрядов заносится врегистр 6. На выходе ЦАП 7 устанавливается напряжение, аквивалентное значениюкода старших разрядов. Одновременно токи управляемых генераторов 8, 9 уменьшаются в К + 1 раэ, вследствие чегопадение напряжения на резисторах делителя2 уменьшается во столько же раз,Таким образом, на втором такте,после затухания переходных процессов в делителе, производится определение следующих й - разрядов двоичного кода, При атом преобразуемое напряжение сравнивается с напряжением на втором вХоде-го компаратора равнымЭЭ 1 др+Оц,где В - диапазон измерения входого напряжения; Цп - напряжение на выходе ЦАП 7. Ширина зоны срабатываниядвух соседних компараторов на втором такте равна -у-Г , а на последнем - в 2 ,0Я+ (Ы+цдПредпоследним импуль-ом распределителя5 код младших разрядов заноситя в триггеры регистра 6, не связанные с ЦАП 7.Наконец, последним импульсом распределителя 5 триггеры регистра 6 устанавливаются в исходное состояние.Число переключателей тока в управляемых генераторах 8, 9 на единицу меньшечисла тактов, поскольку минимальные токине коммутируются, Разность этих токов подбирается такой величины и знака, чтобыскомпенсировать суммарный входной ток компаратора.573872 СостРедактор Г, Котельский Техре ь Д, Голубович.Левицкая Корректо риценко атент, г. Ужгород, ул, Проектная, 4 ал ПП аз 3776/41 Тираж 1065 ПодписноеЦНИИПИ Государственного комитета Совета Министров СССпо делам изобретений и открытий113035, Москва, Ж, Раушская набд. 4/5

СмотретьЗаявка

2140904, 30.05.1975

ИНСТИТУТ АВТОМАТИКИ И ЭЛЕКТРОМЕТРИИ СО АН СССР, НОВОСИБИРСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ

БЕЛОМЕСТНЫХ ВИТОЛЬД АНДРЕЕВИЧ

МПК / Метки

МПК: H03K 13/08

Метки: аналогоцифровой, параллельно-последовательный

Опубликовано: 25.09.1977

Код ссылки

<a href="https://patents.su/4-573872-parallelno-posledovatelnyjj-analogocifrovojj-preobrazovatel.html" target="_blank" rel="follow" title="База патентов СССР">Параллельно-последовательный аналогоцифровой преобразователь</a>

Предыдущий патент: Цифровое измерительное устройство

Следующий патент: Аналого-цифровой преобразователь

Случайный патент: Транзисторный усилитель мощности