Вычислительная система для решения дифференциальных уравнений

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 565299

Авторы: Сулим, Танкелевич

Текст

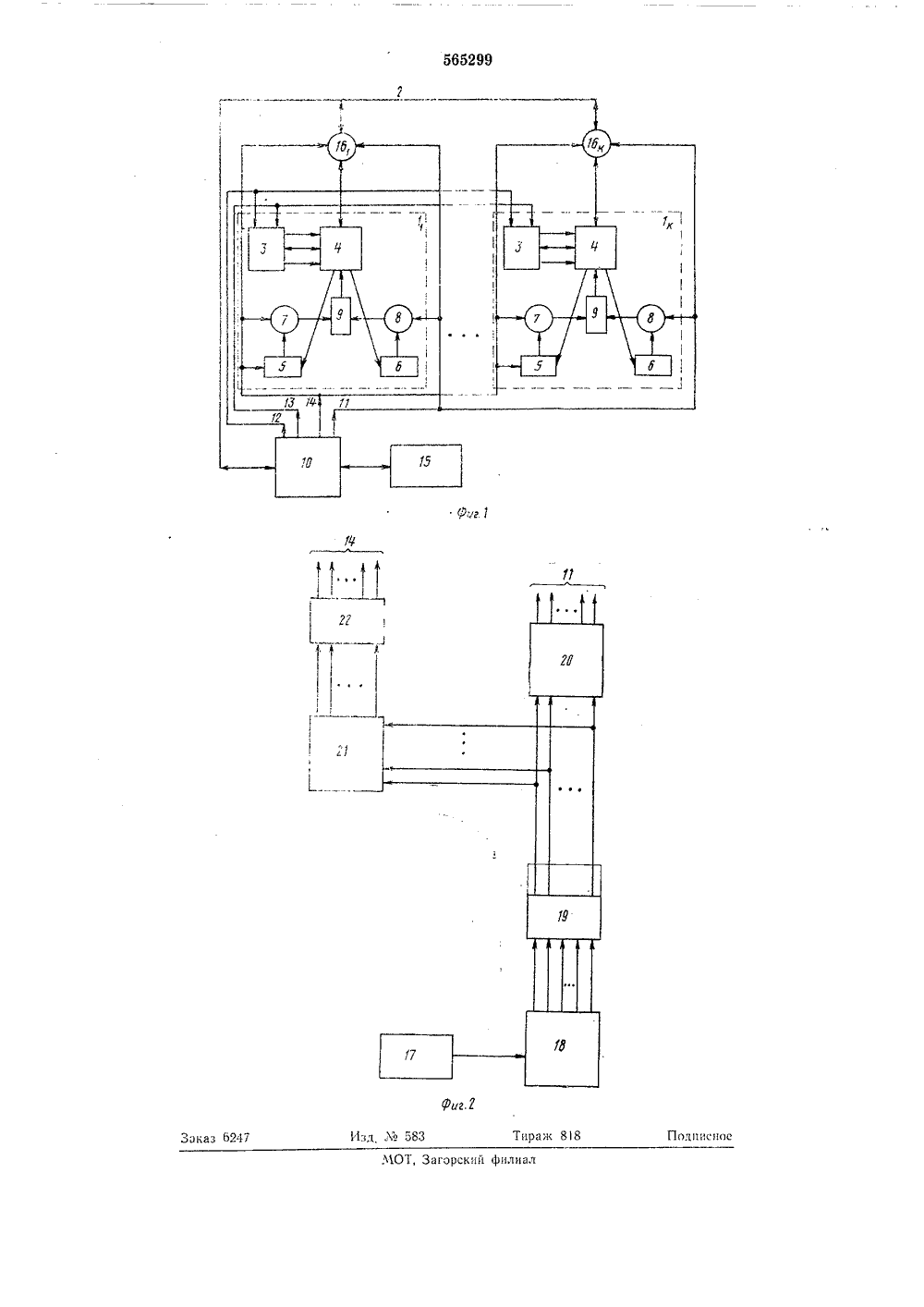

ИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 2) Заявлено 04.07.75 (21) 2153600/ 51) М. Кл. ки т с присоединением осударстеенный комитеСовета Министров СССРоа делам изобретенийи открытий 3) Прио 3) Опуб тет -Бюллетеньис а и ия 07,10.7 ковано 15.07,77(54) ВЫЧИСЛИТЕЛЬНАЯ СИ ДИФФЕРЕНЦИАЛЬНЬ ЕМА ДЛЯ РЕШЕНИУРАВНЕНИЙ 5 о 15 20 61) Дополнительное к ав 1тносится к вычислительной Изобретение отехнике.Известны аналоговые вычислительные машины 11, которые содержат грузину решаю. щих блоков, выполняющих определенные математические опер ации над переменньвми, представленными электрическими сигналами в аналоговой форуме, и соединеиных между собой в соответствии с решаемой системой дифференциальных уравнений. В состав решающих блоков входят интеграторы, сумматоры, масштабные устройства, нелинейелые устройства.Аналоговые машины обладают высоким быстродействием благодаря параллельному характеру выполнения всех математических операций, Однако они илеют ограниченную точность, требуют большого объема оборудования даже для частичной автоматизации ввода в машину исходных данных о задаче.Известны цифровые дифференциальные анализаторы 12, которые содержат группу интеграторов, выполняющих определенные математические операции пад переменными, прЕдставленными в цифровой форме, и связанных между собой в соответствии с решаемой систамой дифференциальных уравнений.Недостатками цифровых дифференциальных анализаторов являются неэффективность форьмул интегрирования, вследствие чего в них требуется применять малыи шаг интегрирования, что снижает быстродействие, и трудность автоматизации ввода схемы моделирования,Известна вычислительная система 13, содержащая решающие блоки, каждый из которых через соответствующий коммутаторсоединен двусторонними связями с инфорзлационной шиной, устройство управления, соединенное,двусторонними связями с устройством ввода-вьввода и с информационнои ши.ной.В данной системе используются решающие блоки, работающие параллельно, Каждый из блоков содержит соединенные междусобой процессор и запоминающее устройство.Недостатком такой системы является трудность осуществления полного распараллелнвасния процесса интегрирования,дифференциальных уравнений из-за необходимости прнменения большого количества процессоров,что ограничивает быстродействие системы икласс решаемых задач.Цель изобретения - повышение производительности и расширение функциональныхвозможностей вычислительнои системы. Дляэтого св предлагаемой .вычислительнойл системе каждый решающий блок содержит регистры чтения и заинеи, ключи, узел связи, .мпкропроцессор, соединенный двустороннимисвязями с заполинающим устройством, подключенным соответсввующим входом и выходом к входу и выходу решающего блока, соединенными с коммутатором, а выходами соответственно,к,входам регистров записи и чтения, Выходы последних через соответствующие ключи соединены с входами узла связи, выход которого подключен к соответствующему входу запоминающего ус 11 ройства. Управляющие входы микропроцессора, ключей, регистра записи каждого решающего блока и управляющие входы каждого коммутатора соединены с соответствующими выходами устройства управления.Микропроцессор предназначен для массового производства, является компактным универсальным элементом, лозволяющим упростить конструкцию, уменьшить габариты. Он может программно настраиваться на выпол. пение произвольных математических операций и использоваться в качестве решающего блока при организации параллельных структур. Применение микропроцессора позволяет ввести существенно большее количество решающих блоков,по сравнению с известной системой, что приближает такую структуру к структуре аналоговых вычислительных машинкоторая характеризуется болыпим быстродействием вслсдствие высокой степени распараллеливания, при сохранении возможности автоматического ввода схемы моделирования и ее параметров.Используемый в системе способ обмена информацией безразличен к количеству связей между блоками, что расширяет класс задач.Микропроцессор и запоминающее устройство в отличие от прототипа небольшие по объему, что упрощает конструкцию, Обращение к запоминающему устроиству при обмене информацией без программной обработки втого обращения увеличивает скорость обмена этой информацией, т. е. увеличивает быстродействие, Использование общего запоминаю щего блока в устройстве управления для хранения матрицы управления, коммутацией позволяет автом атизировать,соединения между чегцающими блоками, что расширяет кларисс задач и увеличивает производительность сиУменьшение гаоаритов устройства достигается также использованием минимально необходимого объема запоминаощего устройства для хранения информации о входных переменных решающих блоков, что достигается магазинной организацией памяти, управляе.мой непосредственно от устройства управления,На фиг. 1 представлена блок-схема вычислительной системы; на фиг, 2 - блок-схема устройства управления, пример реализации.Система содержит решающие блоки 1, - 1, подключенные к общей информационной шине 2. Каждый решающий блок содержит микропроцессор 3, запоминающее 5 О 15 20 25 30 35 40 45 50 60 65 4устройство 4, регистр записи 5, регистр чтения 6, ключи 7, 8, узел,связи 9. В состав системы входят также устройство управления 10 с управляюгцимн выходами 11 - 14,устройство ввода-,вывода 15, коммутаторы16, - 16,Устройство управления (см, фиг. 2) содержит генератор тактовых импульсов 17 счетч лк 18, запоминающий блок 19, дешифратор 20, запоминающий блок 21, информацион.ный регистр 22.Микропроцессор 3 н запоминающее устройство 4 обмениваются информацией по двусторонней информационной шине, адрес ячейки запоминающего устройства передается поадресной связи, состояние записи-чтения -по связи управления чтением-залисью. Сдругой стороны, сипналы записи-чтения мо.гут поступать с выходов 14 и 11 успройствауправления 10, а адрес - из узла 9 овязи,Информационные выходы запоминающегоустройства 4 используются для задания информации в регистры записи и чтения 5, 6.В ключение-,выключение микролроцессора производигся по сигналу, поступающему из устройства управления с выхода 12. Тактовыесигналы подаются на все микропроцессоры свыхода 13 устройства управления. Обмен информацией с шиной 2 производится с помощью коммутаторов. С помощью устройстваавода-вььвода информации 15 производитсязагрузчика решающих блоков исходными данными и программами, а а также вывод рсзультатов в процессе решения,Устройство управления 10 управляет работой системы в двух режимах: Подготовка и Работа.В режиме Подлотоака вводятся программы, При вводе программ последовательно включаются соответствующие коммутаторы, инструкции программ зада 1 огся по ши.не 2.В режиме Раббота циклически новторяются два такта: параллельной раооты решающих блоков и обмена информацией, В результате выполнения одной пары тактов производится очередной шаг итеративного процесса. Останов всей системы производится посигналу извне,В первом такте дается сигнал включениявсех микропроцессоров на время, необходимое для выполнения программы одного нтеративного шага в самом загружснном микропроцессоре. В конце такта все микропроцессоры находятся в исходпом состоянии. Вовтором такте микропроцессоры всех решающих блоков отключены от запоминающихустройств, Перед началом оомена ннфоръа.цией,в каждом итеративном цикле ло программе работы,данного решающего блошка врегистр чтения 6 заносится адрес выходнойпеременной, а в регистр 5 - адрес записи.Если из устройства управления посылаетсясигнал Чтение с выхода 11, то запоминающее устройство переводится в режиме Чте565299 1 О 15 20 25 зо 4 О иие; адрес, по,котороиу производится чтение, считывается из регистра 6 и в информационную магистраль выдается выходная пе.- ременная данного блока. Г 1 ри приходе сигнала За 1 пись с выхода 14 в регистр записи 5 добавляется 1 (регистр работает в режиме счетчика), запоминающее устройство переводится в режим Запись, а адрес, по которому производится запись, считывается из регистра 5. В запоминающее устройство из информационной шины заносится новое значение соопветствующей переменнной.Формирование сигналов Чтение и Запись производит схема управления, показанная на фиг, 2. В запоминающий блок, обращение к которому производится по адресам, вырабатываемым счетчиком, перед началом работы заносится матрица управления ком. мутацией, которая во втором такте построчно выводится на выход 14.Рассмотренная вычислительная система имеет те же области применения, что и аналоговые вычислительные машины общего назначения и цифровые модели, но выгодно от ппх отличается, Вычислительная система благодаря,наличию автоматизированной настройки на схемы моделирования может использоваться в составе автоматизированных вы. числительных систем. Помимо автоматизации ввода схем моделирования, система характеризуется высокой точностью и стабильностью благодаря применению цифровых принципав обработки информации. Примененный .способ обработчики информации обеспечивает достаточно высокое быстродействие, которое по предварительным оценкам находится на уровне быстродействия аналоговых вычислительных ма. шин при значительно более высокой точности (точность увеличена примерно,в 100 раз). По сравнению с,прототипом представленная система обладает большим быстродействием. Характерной особенностью системы является использование минимально необходимого объема запоминающего устройства для хранения входных и выходных переменных, что упрощает и удешевляет систему,Ми 1 кропроцессоры, являющиеся универсальной компонентной базой современной вычислительной техникипоказывают тенденцию к,резкому увеличению быстродействия и уменошению стоиьмости. Формула изобретения Вычислительная система для решения дифференциальных уравнений, содержащая решающее блоки, каждый из которых через соответствующий каммутатор соединен дну. сторонними связями с информационной ши. ной, устройство управления, соединеннное двусторонними .связями с устройством ввода- вывода н с информационной шиной, о т л ич а ющ а я тем, что, с целью повышения производительности и расширения функциональных возможностей, в ней каждый решающий блок содеркит регистры чтения и записи, ключи, узел связи, ммкропроцессор, соединенный двусторонними связями с запомпнающю устройством, подключенным соответствующим входом и выходом к входу и выхо ду решающего блока, соединенными с коммутатором, выходами соответственно к входам регистров записи и чтения, выходы которых через соответствующие ключи соединены с входами узла связи, выход которого подключен к соответствующему входу запомина ющего устройства, управляющие входы микропроцессора, ключей, регистра записи кажз; дого решающего блока и управляющие входы каждого коммутатора соединены с соответствующими выходами устройства управления.Источники информации,принятые во внимание прп экспертизе1, И, Витенберг Програ 1 ммирование аналоговых вычяслительных машин, Машиностроение, М 1972, с. 7.2. Л. В. Шилейко Цифровые модели,Энергия, М., 1964, с. 22 - 55.3. Зарубежная радиоэлектроника8,1973, с. 53 - 62 (прототип),565299 Фиг гПолписнопрап орский фил

СмотретьЗаявка

2153600, 04.07.1975

ПРЕДПРИЯТИЕ ПЯ В-2672

СУЛИМ МИХАИЛ КИРИЛЛОВИЧ, ТАНКЕЛЕВИЧ РОМАН ЛЬВОВИЧ

МПК / Метки

МПК: G06F 17/13

Метки: вычислительная, дифференциальных, решения, уравнений

Опубликовано: 15.07.1977

Код ссылки

<a href="https://patents.su/4-565299-vychislitelnaya-sistema-dlya-resheniya-differencialnykh-uravnenijj.html" target="_blank" rel="follow" title="База патентов СССР">Вычислительная система для решения дифференциальных уравнений</a>

Предыдущий патент: Резервированное устройство с управляемой структурой

Следующий патент: Цифровой нерекурсивный фильтр

Случайный патент: 372903