Логическое запоминающее устройство

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

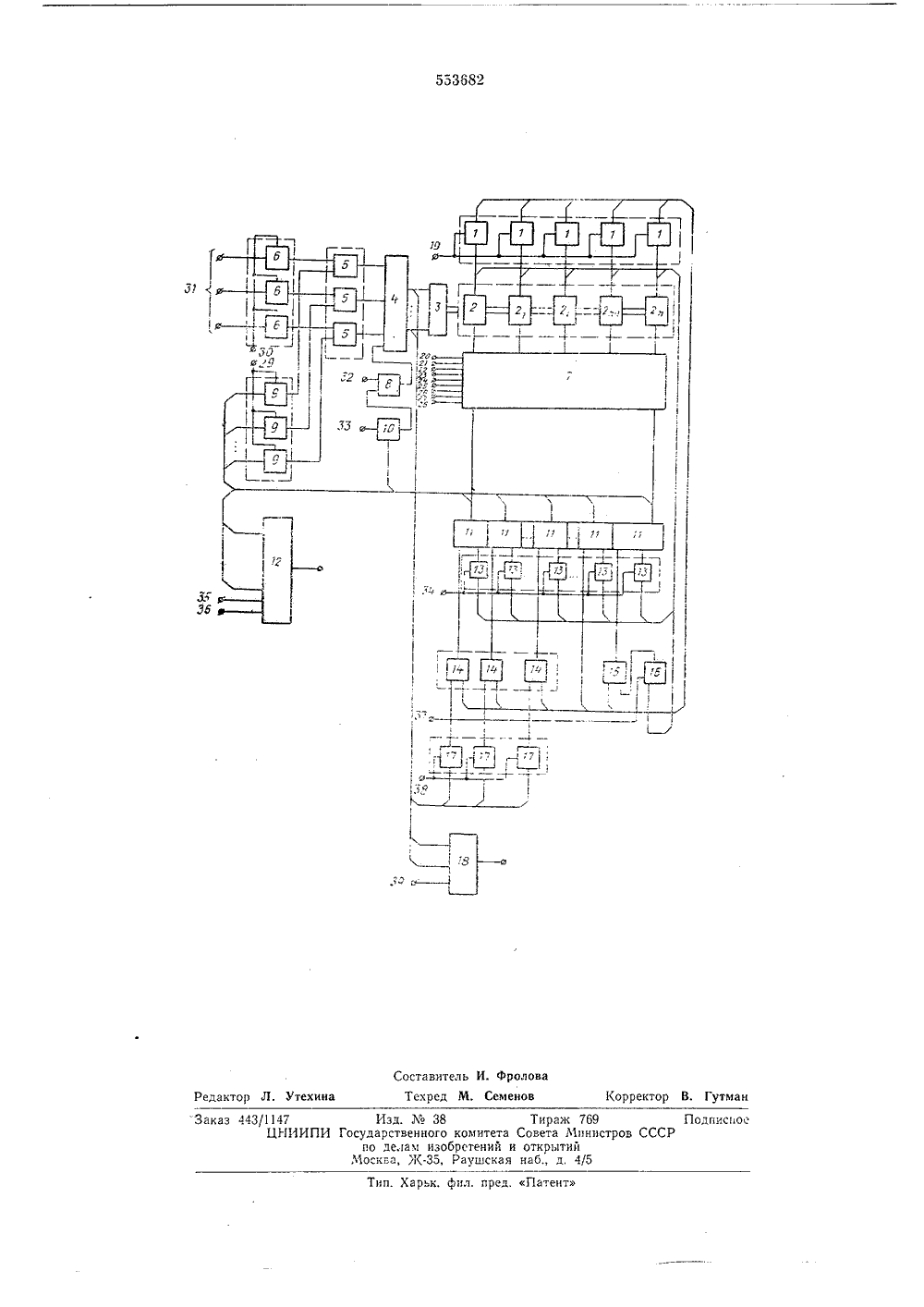

ОПИСАН И Е ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 11)553682 Союз Советских Социалистических Республик(45) Дата опубликования описания 25.07.77(51) М.Кл.-" б 11 С 15/00 Государственный комитет Совета Министров СССР по делам изобретенийн открытий 5 а) УДК 628.327.6(54) ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО3 Изобретение относится к области запоминающих устройств и может быть применено в системах хранения и обработки информациии.В настоящее время особое значение приобретают задачи увеличения помехоустойчивости, повышения достоверности передачи и обработки информации. Одним из методов решения этих задач является применение помехоустойчивых кодов в сочетании с синхронной передачей информации.Известны логические устройства, позволяющие производить фазирование по циклам с непрерывной передачей сообщений 11. В этих устройствах фазирующие символы передаются в течение передачи т кодовых комбинаций. Датчик фазирующей комбина ции, подключенный к одногиу из контактов передающего распределителя, за каждый цикл передает элемент фазирующей комбинации на приеме, к соответствующему контакту распределителя подключается дешифратор фазирующей комбинации, выход которого соединяется с устройством управления. При таком способе фазирования может потребоваться (2 т - 1) циклов. Поэтому, если в течение 2 т циклов с выхода дешифратора не поступит импульс, то под действием устройства управления фаза приемного распределителя смещается на один контакт и процесс поиска фазирующей комбинации продолжается. Такой режим сохраняется до тех пор, пока дешифратор не зафиксирует наличие фазирующей комбинации, Под действием импульса с дешифратора триггер переходит в состояние 1, блокируя устройство управления.Наиболее близким техническим решением к данному изобретению являются логические устройства, содержащие последовательно соединенные регистр и дешифратор адреса и и-разрядный блок памяти, регистр слова, подключенный к блоку управления и блоку анализа содержимого регистра слова, шины управления 2.Недостатком данной схемы является небольшая скорость обработки информации, кодирования, декодирования и невозможность выполнения синхронизации по циклам.Целью изобретения является расширение функциональных возможностей ЛЗУ для применения их при синхронизации по циклам.Поставленная цель достигается тем, что предложение ЛЗУ содержит элементы И и ИЛИ и дополнительный дешифратор адреса, один вход которого подключен к шине управления, а другие входы - к соответствующим выходам регистра адреса и через первую группу элементов И к первым входам элементов ИЛИ первой группы. Выходы эле5 10 15 20 25 30 35 40 45 50 55 ьо 65 ментов ИЛИ первой группы подключены и первым входам первой группы элементов регистра слова. Первый вход последнего элемент регистра слова через последовательно соединенные элементы ИЛИ и И подключен к соответствующему выходу и-разрядного блока памяти. Второй вход элемента И подключен к шине управления. Вторые входы элементов ИЛИ первой группы, первые входы второй группы элементов регистра слова и второй вход элемента ИЛИ подключены к соответствующим элементам И второй группы, Первые входы элементов И второй группы подключены к соответствующей шине управления, а вторые - к соответствующим выходам п-разрядного блока памяти, Вторые входы регистра слова через третью группу элементов И подключены к соответствующим выходам п-разрядного блока памяти. Вторые входы элементов И третьей группы подключены к соответствующей шине управления. Выходы регистра слова подключены к соот. ветствующим входам блока анализа содержимого регистра слова, другие входы которого подключены к шинам управления. Выходы первой группы элементов регистра слова через последовательно соединенные элементы И четвертой группы и ИЛИ второй группы подключены к входам регистра адреса, а вторые входы элементов ИЛИ второй группы через элементы И пятой группы и вторые входы элементов И четвертой группы подключены к соответствующим шинам управления. Выход первого элемента регистра слова подключен через последовательно соединенные элементы И и ИЛИ к соответствующему входу регистра адреса, а вторые входы элементов И и ИЛИ - к соответствующим шинам управления,На чертеже изображена схема предлагаемого ЛЗУ.Оно содержит элементы И второй группы 1 для прямого чтения, п-разрядный блок памяти 2, дешифратор адреса 3, регистр адреса 4, элементы ИЛИ второй группы 5, эле.менты И пятой группы 6 для приема кода адреса на регистр адреса из внешних устройств, блок управления 7, элемент ИЛИ 8, элементы И четвертой группы 9 для передачи на регистр адреса кода из регистра слова, элемент И 10 для передачи содержимого первого разряда регистра слова на вход регистра адреса, регистр слова 11, блок анали.за содержимого регистра слова 12, элементы И третьей группы И для выполнения суммирования по модулю два, элементы ИЛИ первой группы 14, элемент ИЛИ 15, элеменг И 16 для чтения из первого разряда блока памяти в п-й разряд регистра слова, элементы И первой группы 17 для передачи кода адреса на регистр слова, дополнительный ,чешифратор адреса 18, шины управления 19 - 39.Входы блока памяти 2 соединены с выходом дешифратора адреса 3, входы которого подключены к соответствующим выходам регистра адреса 4, каждый вход которого подключен к соответствующему выходу элементов ИЛИ второй группы 5. Первые входы этих элементов подключены к соответствующему элементу И пятой группы б, предназначенного для приема кода адреса из внеш. него устройства. Первые входы элементов И пятой группы б подключены к шине управления приема кода адреса 30, а вторыс входы - к входным шинам Л. Вторые входы элементов ИЛИ второй группы 5 подклю чецы к соответствующим элементам И четвертой группы 9, предназначенной для передачи кода адреса из регистра слова 11, пер. вые входы элементов И четвертой группы 9 подключены к шине передача кода из реги стра слова 29, а вторые входы - к соответ ствующим выходам первой группы элементов регистра слова 11. Второй вход первого разряда регистра адреса 4 подключен к выходу элемента ИЛИ 8, первый вход которого подключен к шине управления установка регистра адреса в следующее состояние 32, второй вход подключен к элементу И 10 передачи содержимого первого разряда регистра слова на вход первого разряда регистра адреса 4, первый вход которого подключен к шине управления передачей 33, а второй вход - к выходу первого разряда регистра слова. Вторые входы каждого разряда блока памяти 2 подключены к блоку управления 7, первые входы которого подключены к управляющим шинам 20 - 28. Вторые входы блока 7 подключены к выходам регистра слова 11. Выходы регистра слова 11 подключены к входам блока анализа состояния регистра слова 12, вторые входы которого, подключены к шине анализ состояния регистра слова 35, а третьи входы - к шине анализ состояния первого разряда Зб. Первые входы первой группы элементов регистра слова 11 подключены к соответствующим выходам элементов ИЛИ первой группы 14, первые входы которых подключены к соотвечствующему эле менту И первой группы 17, предназначенного для передачи кода адреса на регистр слова. Первые входы элементов И первой группгя 17 подключены к шине управления передача кода адреса на регистр слова 38, а вторые - к соответствующим выходам регистра адреса 4, которые одновременно подключены к дополнительному дешифратору адреса 18, другой вход которого подключен к шине управления опроса дешифратара 39. Первый вход последнего элемента регистра слова 11 почключен к выходу элемента И 15, первый вход которого подключен к элементу И 16, предназначенного для чтения первого разря. да блока памяти на и-й разряд регистра сло ва. Первый вход элемента И 16 подключен к шине управления чтением из первого разряда блока памяти на соответствующий разряд регистра слова 37, а второй - к выходу первого разряда блока памяти 2, Вторыевходы элементов ИЛИ первой группы 14, первые входы второй группы элементов ре. гистра слова 11 и второй вход элемента ИЛИ 15 подключены к соответствующим элемен. там И второй группы 1, предназначенным для прямого чтения. Первые входы этих эле ментов подключены к шине управления прямого чтения 19, а вторые - к соответствующим выходам элементов блока памяти 2, Вторые входы элементов регистра слова 11 подключены к соответствующим элементам И третьей группы 17, предназначенным для суммирования по модулю два. Первые входы этих элементов подключены к шине управления сумма по модулю два 34, а вто рые входы - к выходу соответствующих элементов блока памяти 2,ЛЗУ может выполнять операции синхро низации по циклам, циклическое кодирование, декодирование, левый логический сдвиг, правый логический сдвиг, прямую запись, прямое считывание и т. д.В качестве примера рассмотрим реализацию операции передача кода адреса на регистр слова. В исходном состоянии на ре. гистре адреса 4 хранится операнд Х, адрес ячейки А; и-разрядного блока памяти 2. При подаче управляющего сигнала на шину управления передачей кода на регистр сло ва 38 сигнал поступает на элементы И первой группы 17, При этом информационные сигналы с выходов регистра адреса 4 через элементы И первой группы 17 и элементы ИЛИ первой группы 14 поступают на входы регистра слова 11, записывая код операнда Х на регистр слова,Формула изобретенияЛогическое запоминающее устройство, содержащее последовательно соединенные ре гистр, дешифратор адреса и и-разрядный блок памяти, регистр слова, подключенный к блоку управления и блоку анализа содержимого регистра слова, шины управления, отличающееся тем, что, с целью расширения функциональных возможностей устройства, оно содержит элементы И и ИЛИ и дополнительный дешифратор адреса, один вход которого подключен к шине управления, а другие входы - к соответствующим выходам регистра адреса и через первую группу элементов И к первым входам элементов ИЛИ первой группы; выходы элементов ИЛИ первой группы подключены к первым входам первой группы элементов регистра слова; первый вход последнего элемента регистра слова через последовательно соединенные элементы ИЛИ и И подключен к соответствующему выходу и-разрядного бло ка памяти; второй вход элемента И подключен к шине управления; вторые входы элементов ИЛИ первой группы, первые входы второй группы элементов регистра слова и второй вход элемента ИЛИ подключены к соответствующим элементам И второй группы; первые входы элементов И второй группы подключены к соответствующей шине уп равления, а вторые - к соответствующим выходам и-разрядного блока памяти; вторые 2 о входы регистра слова через третью группуэлементов И подключены к соответствующим выходам п-разрядного блока памяти; вторые входы элементов И третьей группы подключены к соответствующей шине управления: выходы регистра слова подключены к соответствующим входам блока анализа содержимого регистра слова, другие входы которого подключены к шинам управления; вы.ходы первой группы элементов регистра слова через последовательно соединенные элементы И четвертой группы и ИЛИ второй группы подключены к входам регистра адреса, а вторые входы элементов ИЛИ второй группы через элементы И пятой группы и З 5 вторые входы элементов И четвертой группыподключены к соответствующим шинам управления; выход первого элемента регистра слова подключен через последовательно соединенные элементы И и ИЛИ к соответству ющему входу регистра адреса, а вторые входы элементов И и ИЛИ - к соответствую.щим шинам управления. Источники информации, принятые во вни.4 мание при экспертизе изобретения:1. Стифлер Дж. Дж. Теория синхроннойсвязи. Изд, Связь, М 1975 г.2. Авторское свидетельство по заявкеМ 2113 б 48/24, кл. б 11 С 15/00, 14.03.1975 г,553682 Составитель И. ФроловаУтехина Техред М. Семенов Корректор В. Гутма едакто 1 1147ЦНИИ одпис ое Заказ п. Харьк. фил. пред. Патент Изд.38Государственногопо де. ам изоМоск а, гК-Зэ,Тираж 769омитета Совета Министров Сетений и открытийаушская наб., д. 4/5

СмотретьЗаявка

2315158, 13.01.1976

ПРЕДПРИЯТИЕ ПЯ В-8828, ЛЕНИНГРАДСКИЙ ОРДЕНА ЛЕНИНА ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. И. УЛЬЯНОВА

БАЛАШОВ ЕВГЕНИЙ ПАВЛОВИЧ, ГОРДОНОВ АЛЕКСАНДР ЮРЬЕВИЧ, ЕРХОВА НИНА ВАСИЛЬЕВНА, КОЛЕНОВ ЕГОР ВАСИЛЬЕВИЧ, ПЕТРОВ ГЕННАДИЙ АЛЕКСЕЕВИЧ, СТЕПАНОВ ВИКТОР СТЕПАНОВИЧ, СУРОВЦЕВ ЮРИЙ АФАНАСЬЕВИЧ

МПК / Метки

МПК: G11C 15/00

Метки: запоминающее, логическое

Опубликовано: 05.04.1977

Код ссылки

<a href="https://patents.su/4-553682-logicheskoe-zapominayushhee-ustrojjstvo.html" target="_blank" rel="follow" title="База патентов СССР">Логическое запоминающее устройство</a>

Предыдущий патент: Логический запоминающий блок

Следующий патент: Устройство сдвига цифровой информации

Случайный патент: Устройство для получения слитков