Интерполятор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 479123

Автор: Шадский

Текст

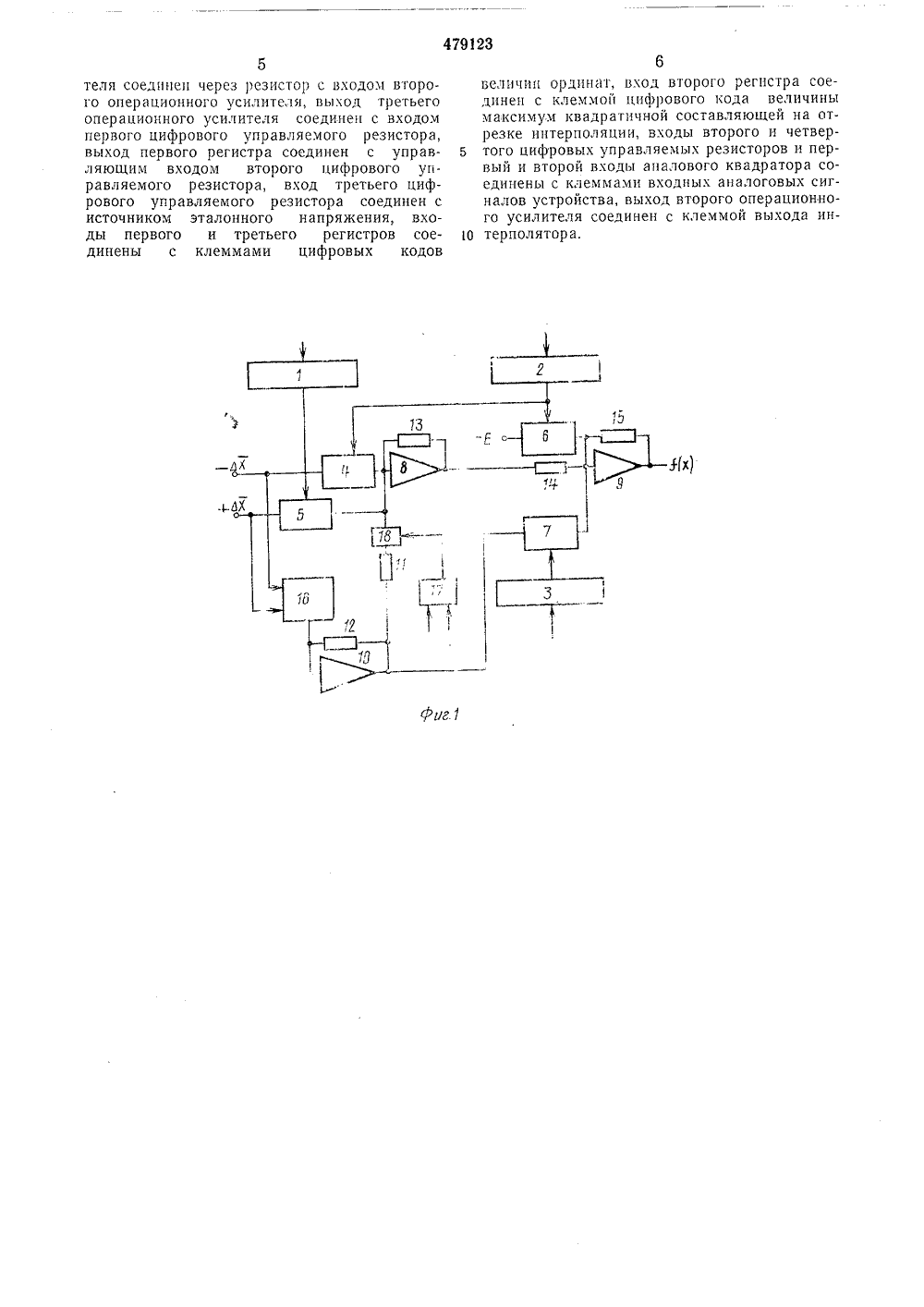

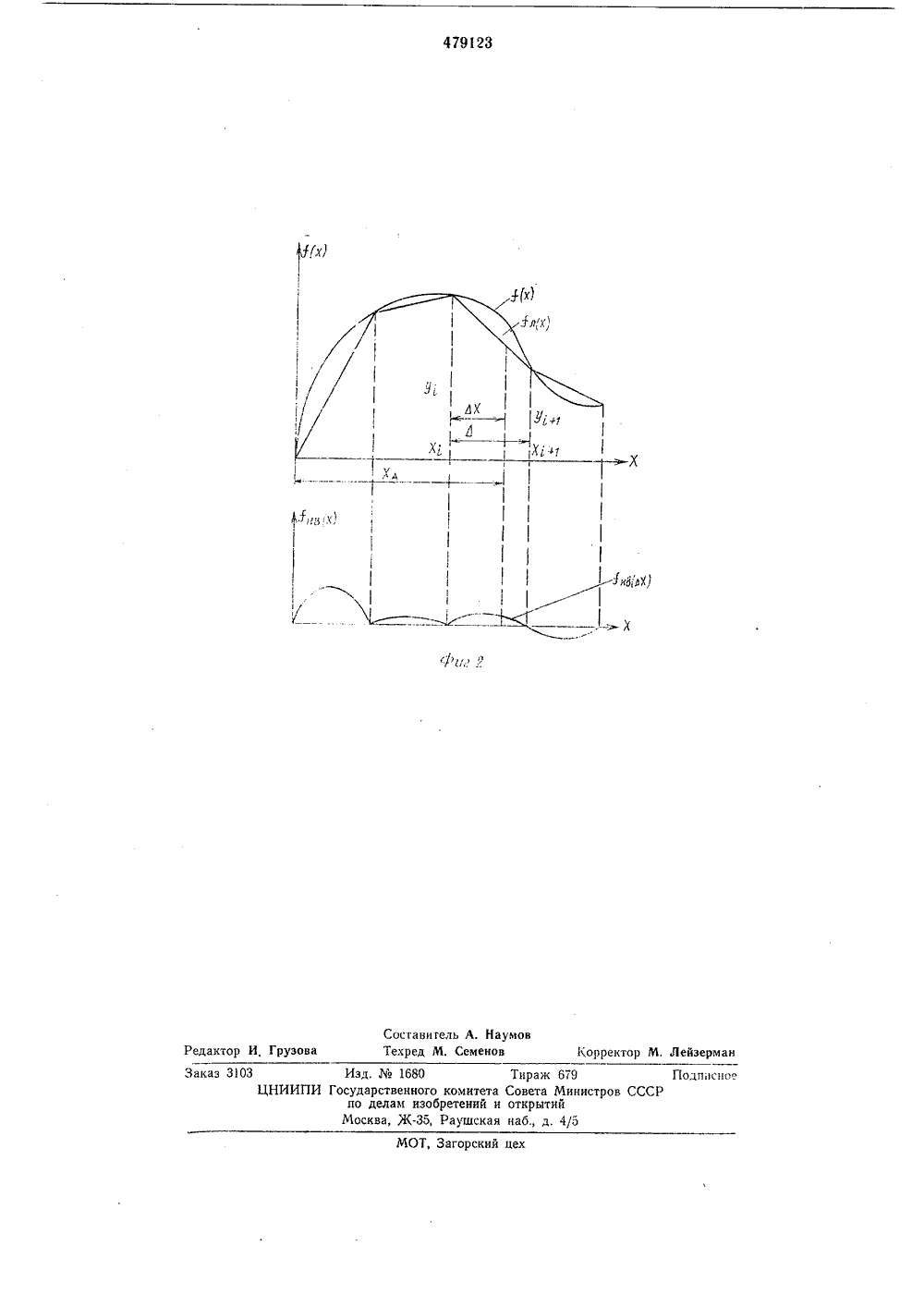

ибляот О и и с х т 1 ие ИЗОБРЕТЕН ИЯ Союз оеетских Социалистицеских Республик(23) Приоритет -Опубликовано 30.07.75. Бюллетень28Дата опубликования описания 16.09.76 51) М. Кл С 06 д 7/30 Государстаенныи комит Совета Мннистроа ССС оо делам иаооретенийн открытий УДК 681 335(08) Автор изобретения М, Шадский кой С Институт ядерной энергетики АН Бе(71) Заявитель 4) ИНТЕРПОЛЯТО Ивойникиной операционного усилителя. Выход первого операционного усилителя через резистор связан с входом второго, операционного усилителя, вход третьего цифрового управляемого резистора - с источником эталонного напряжения. Входы второго и четвертого цифровых управляемых резисторов и первый и второй входы квадратора соединены с клеммами входных аналоговых сигналов.На фиг, 1 показана схема устройства; на фиг. 2 - аппроксимация функции.Схема устройства содержит регистры 1, 2, 3, цифровые управляемые резисторы 4 - 7, причем на резистор 6 подается постоянное напряжение - Е, операционные усилители 8, 9, 10, резисторы 11 - 15 аналоговый квадратор 16, триггер 17 и ключ 18. Все перечисленные элементы известны и находят широкое применение в аналоговой и аналого-цифровой вычислительной технике. Схема вычисляет значение непрерывной функции /(х) на интервале интерполяции в соответствии с формулой(х) =у, + (у:+1 - у, ) Ах+а, (.Хх - Лх)(1) где Лх=Лпостоянныйфициент;величина и я -го участка коэф ервала интерпол зобретение относится к области аналогот аналого-цифровой вычислительной техн может быть использовано как основблок функционального преобразователя сквадратичной интерполяцией функции.Известны устройства для воспроизведениянепрерывной функции одной переменной, вкоторых применена аналого-цифровая схемадля выполнения операции интерполированиямежду каждыми двумя соседними заданными 1значениями функции. Они содержат операционные усилители, цифровые управляемые резисторы, квадратор, регистры, триггер знака,ключи, Сложность таких устройств обусловлена, в частности, тем, что для учета изменения 1знака квадратичного члена в формуле интерполяции используется операционный усилитель в режиме инвертора,Без ухудшения основных характеристик поточности и быстродействию предлагается более экономичная схема интерполятора, содержащая меньшее количество операционныхусилителей и ключевых схем.Положительный эффект достигается тем,что выход аналогового квадратора соединен с 2третьим операционным усилителем, выход которого через последовательно соединенные резистор и ключ подключен к входу первогооперационного усилителя и через первый цифровой управляемый резистор к входу второго 3) 479235 10 15 ог 30 35 20 40 45 50 55 60 65 3Квадратор 16 совместно с усилителем 1 О ьоспроизводит величину - (Лх - Лх) . Схемы цифровых управляемых резисторов проводят умножение поданных на их входы аналоговых величин на цифровые коды, записанные в соединенных с ними регистрах. Результат получается в аналоговой форме. Операционные усилители 8 и 9 обеспечивают развязку цепей, подсоединенных к их входам, и суммирование частных результатов.Схема работает следующим образом. На входы цифровых управляемых резисторов 4 и 5 подаются аналоговые переменные - Лх и + Лх, а на входы регистров 1, 2, 3 - цифровые коды величин у;, г, у;, а;, причем а; - в прямом коде, если величина а,) 6, и в обратном коде, если а; (О.Рассмотрим первый случай.а, )О (ключ 18 закрыт). Тогда после записи у , уг+г и а, в регистры и подачи, +Лх и - Лх на входы элементов 4, 5, 16 и завершения переходных процессов (длительность которых может быть доведена до одной микросекунды), получим на выходе усилителя 10 в виде напряжения величину, - (Лх - Лх 2). Знак минус перед (Лх - Лх) всегда может быть обеспечен, так как на входы квадратора 16 подаются +Лх и - Лх. Схемы цифровых управляемых резисторов 4 и 5 совместно с усилителем 8 обеспечивают получение произведений +уг+гЛх и - у;Лх и одновременное их суммирование. Таким образом, на выходе усилителя 8 получаем - (уг+1 -- у; ) Лх, так как усилитель изменяет также знак суммы входных величин на противоположный.Схема цифрового управляемого резистора 6, на вход которого подается напряжение - Е, а управление осуществляется от регистра 2, обеспечивает преобразование кода у; в аналоговую форму (т, е, получение первого члена в формуле 1), а схема цифрового управляемого резистора 7 - получение произведения. - (Лх - Лх) а, . Усилитель 9 суммирует члены - у - (Уг+г - У; )Лх и - а; (Лх - Лх 2). С учетом общего изменения знака на противоположный на выходе усилителя 9 имеем +(уг + (уг+1 - У; )Лх+а; (Лх - Лх). Конечный результат получается в аналоговой форме.Рассмотрим второй случай.а; (О и ключ 18 открыт, Линейная составляющая формулы (1), т, е. у, +(уг- у; )Лх, образуется совершенно аналогично как и в случае, когда аг О, а квадратичный член должен быть получен со знаком минус в окончательном результате, т. е, необходимо получить на выходе усилителя 9 выражение +1 У г + (уг+г - у, ) Лх - и, (Лх - Лх)1. Покажем, что предлагаемая схема обеспечивает это. Поскольку ключ 18 теперь открыт, то напряжение - (Лх - Лх) с выхода усилителя 10 посту 4пает пе только на схему цифрового управляемого резистора 7, связанного с усилителем 9, но и на вход резистора 14, также соединенного с усилителем 9 (через ключ 18 и усилитель 8). Схема цифрового управляемого резистора 7 осуществляет умножение величины напряжения - (Лх - Лхк), поданной на его вход, на код числа, записанного в регистре 3 с получением результата в аналоговой форме. Поэтому, если в регистре 3 записан прямой код величины а то получим - (Лх -- Лх)а если обратный код величины а тО - (ЛХ - ЛХ)а;,бр ГДЕ а г обр ВЕЛИЧИНа, пропорциональная обратному коду числа, а; (без учета знака а, ) и, наконец, когда в регистре записан код максимальной величины а;, то - (Лх - Лх) а г кОчевидно соотношениеа.(Лх - Лх)+а обр (Лх - Лх) == а; м, (Лх - Лх) (2)Выберем величину резистора 11 таким образом, чтобы отношение сопротивлений резисторов 13 и 11 равнялось бы аг макс Тогда, через резистор 11, ключ 18 и усилитель 8 на вход резистора 14, связанного с усилителем 9, поступает напряжение а;мс (Л - Лх 2),Поскольку в регистре 3 записан обратный код величины а,. (аг (О), то цифровой управляемый резистор 7 обеспечивает получение произведения - амакс(Лх - Лх). Усилитель 9 суммирует а г макс. (Лх Лх) и - агобр,(Лх - Лх), Сумма получается на его выходе с обратным знаком, т. е.+ (аг обр, аг макс. )(ЛХ - ЛХ )Учитывая соотношение (2) получим (аг обр. - а г макс)(ЛХ - ЛХ) = - а; (ЛХ - ЛХ), а с учетом линейной составляющейу;+ (уг+г - у,) Лхна выходе схемы (на выходе усилителя 9) образуетсяУг+ (у г. г - у;)Лх - а, (Лх - Лх).Предмет изобретения Интерполятор, содержащий цифровые уп. равляемые резисторы, управляемые входы ко. торых соединены с соответствующими регистрами, аналоговый квадратор, операционные усилители, входы первого и второго из кото. рых соединены с выходами цифровых управ. ляемых резисторов, ключ и триггер знака, от,гачающийся тем, что, с целью упрощения схемы, в ней выход аналогового квадратора соединен с входом третьего операционного усилителя, выход которого через последовательно соединенные резистор и ключ, управляющий вход которого соединен с триггером знака, соединен с входом первого операционного усилителя, выход первого операционного усили479123 1 Ь) фу 5теля соединен через резистор с входом второго операционного усилителя, выход третьего операционного усилителя соединен с входом первого цифрового управляемого резистора, выход первого регистра соединен с управляющим входом второго цифрового управляемого резистора, вход третьего цифрового управляемого резистора соединен с источником эталонного напряжения, входы первого и третьего регистров соединены с клеммами цифровых кодов величин ординат, вход второго регистра соединен с клеммой цифрового кода величины максимум квадрагичной составляющей на отрезке интерполяции, входы второго и четвер того цифровых управляемых резисторов и первый и второй входы аналового квадратора соединены с клеммами входных аналоговых сигналов устройства, выход второго операционного усилителя соединен с клеммой выхода ин- О терполятора;/),Л оставигель А. Наумоехред М. Семенов Корректор М, Лейзерма Редактор рузов Тираж 679Совета Министроткрытийнаб д. 4/5 ОТ, Загорский цех каз 3103ЦНИИП Изд.1680осударственного комитет по делам изобретенийМосква, Ж, Раушска Поди основССР

СмотретьЗаявка

1943023, 16.07.1973

ИНСТИТУТ ЯДЕРНОЙ ЭНЕРГЕТИКИ АН БЕЛ. ССР

ШАДСКИЙ ВЛАДИМИР МИХАЙЛОВИЧ

МПК / Метки

МПК: G06G 7/30

Метки: интерполятор

Опубликовано: 30.07.1975

Код ссылки

<a href="https://patents.su/4-479123-interpolyator.html" target="_blank" rel="follow" title="База патентов СССР">Интерполятор</a>

Предыдущий патент: Дифференцирующее устройство

Следующий патент: Устройство для решения систем нелинейных алгебраических уравнений

Случайный патент: 156847