Устройство для обнаружения и исправления ошибок в системе остаточных классов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

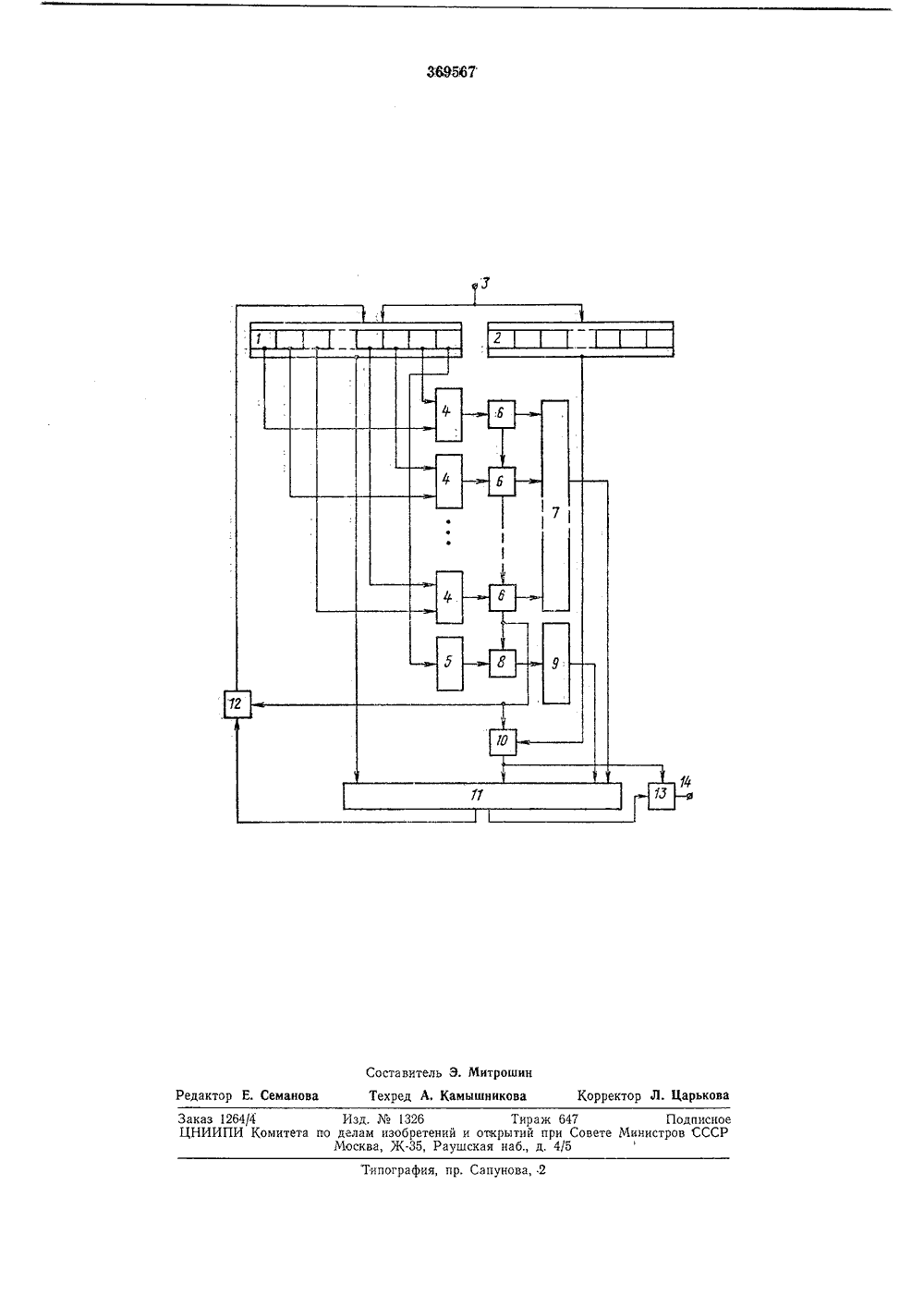

О П И С А Н И Е 36956 УИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Сана Советских Ссциалистическил РеспубликЗависимое от авт. свидетельстваЗаявлено ИЛЧ.1971 ( 1644357/18-24) 11/04 исоединением заявки Комитет по гтелаан изобретений к открытий ори Совете Министровиорит 6.77(088 ДК 681,3 Опубликовано 08 Л,193. Бюллетень10Дата опубликования описания 14 Л.1973 тсъъе 1 С Авто,рыизобретени ф. Нестерук и В. отапов Омский политехнический инстит аявител УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И ИСПРАВЛЕНИЯ ОШИ В СИСТЕМЕ ОСТАТОЧНЪХ КЛАССОВ Устройство относится к области автоматики и вычислительной техники.Известны устройства для обнаружения и исправления ошибок в системе остаточных классов, содержащее подключенные ко входным шинам операционный и запоминающий регистры с и выходами, дешифраторы, блоки памяти констант нулевизации и ошибок, сумматор, переключатели, вентили и ключи.Общим недостатком известных устройств является высокая структурная сложность и относительно низкое быстродействие. Предложенное устройство отличается тем, что в нем г-ый и (и - г+1) -ый выходы операционного регистра попарно подключены ко входам соответствующих дешифраторов, выходы которых через последовательно включенные переключатели соединены со входными шинами блоки памяти констант нулевизации, а выходы операционного регистра через дешифратор и подключенные к последнему переключателю вентили подсоединены к блоку памяти констант ошибок, Выходы операционного регистра и блока памяти констант нулевизации и констант ошибок непосредственно, а выходы запоминающего регистра через присоединенные к последнему переключателю входные вентили подключены ко входам сумматора, выходы которого через вентили запрета соединены со входами операционного регистра и через выходные ключи подключены к выходным шинам устройства.Это позволило упростить схему и повыситьбыстродействие устройства.5 На чертеже приведена схема устройства.Устройство состоит из операционного регистра 1, содержащего ячейки для хранения остатков по рабочим и контрольному основанию и предназначенного для запоминания 10 контролируемого числа и результатов промежуточных вычислений запоминающего регистра 2, содержащего ячейки для запоминания остатков контролируемого числа по рабочим и контрольному основаниям и хранения нх в 15 течение времени обнаружения ошибки. Входы операционного и запоминающего регистров подключены ко входным шинам 3 устройства обнаружения и исправления ошибки, а выходы г-ой и (гг - г+1)-ой ячеек операци онного регистра соединены попарно со входами дешифраторов 4. Если количество ячеек нечетное, то ко входам последнего из дешифраторов 4 подключены выходы одной, средней из гг ячеек для остатков по рабочим осно ваниям, Выходы (гг+1)-ой ячейки операционного регистра 1, в которую заносится остаток числа по контрольному основанию, подключены ко входам дешифратора 5.Выходы дешифраторов 4 через взаимосвя занные последовательно управляющие одиндругим переключатели б соединены со входами блока памяти 7 констант нулевизации. Эти константы предназначены для нулевизации контролируемого числа. Выходы дешифратора 5 через управляемые последним из переключателей б вентили 8 подключены ко входам блока памяти 9 констант ошибок, вычитание которых из контролируемого числа устраняет ошибку в контролируемом числе. Кроме этого, выходы ячеек операционного регистра 1 и выходы блоков памяти 7 и 9 непосредственно, а выходы ячеек запоминающего регистра 2 через управляемые последним из переключателей б входные вентили 10, соединены со входами сумматора П, в котором осуществляется нулевизация контролируемого числа. В этом же сумматоре П осуществляется исправление ошибки путем вычитания из контролируемого числа констант ошибок. Выходы сумматора П через управляемые последним из переключателей б вентели запрета 12 соединены со входами операционного регистра 1 для занесения в пего промежуточных результатов при нулевизации контролируемого числа. Кроме того, выходы сумматора 11 через управляемые входными вентилями 10 выходные ключи 13 подключены к выходным шинам 14 устройства оонаружения и исправления ошибок для выдачи исправленного числа.Работа предлагаемого устройства обнаружения и исправления ошибок осуществляется следующим образом. На входные шины 8 устройства обнаружения и исправления ошибок подается контролируемое число, которое одновременно записывается в операционный 1 и запоминающий 2 регистры. В начальном состоянии последовательно управляющие один другим переключатели б, за исключением первого, находятся в запертом состоянии, В запертом состоянии находятся также вентили 8, входные вентили 10 и выходные ключи 18 сумматора 11, По первому рабочему такту сигналы с выходов всех ячеек операционного регистра 1 подаются на соответствующие входы дешифраторов 4 и 5, Одновременно контролируемое число с выходов операционного регистра 1 заносится в сумматор 11, затем производится одновременный опрос дешифраторов 4, начиная с первого. (Первым из дешифраторов 4 будем называть дешифратор 4, входы которого соединены с выходами 1-ой и и-ой рабочих ячеек операционного регистра 1, вторым - дешифратор, входы которого соединены с выходами 2-ой и (п - 1)-ой рабочих ячеек операционного регистра 1 и т, д, Последний из дешифраторов 4 при четном числе рабочих ячеек регистра 1 соединен по входам с выход . идами - -ой и 1 +1)-ой рабочих ячеек реги 2 2стра 1, а при нечетном числе рабочих ячеек операционного регистра 1 соединен по вхо 5 10 15 20 25 30 35 40 45 50 55 60 65 й - 1дам с вь 1 ходами 1 +1)-ой рабочей ячей- г кп регистра 1).Если в 1-ой и ц-ой рабочих ячейках регистра 1 записаны ненулевые остатки, то при анализе выходного сигнала первого из дешифраторов 4 этот сигнал через связанный с первым дешифратором 4 открытый первый из переключателей б поступит на вход блока памяти 7 констант нулевизации и выоерет оттуда соответствующую константу нулевизации. Эта константа поступает в сумматор 11, где вычитается из занесенного туда ранее контролируемого числа. Константа подобрана таким образом, что при ее вычитании из контролируемого числа в остатках по 1-му и а-му рабочим основаниям образуются нули. Полученное после первого цикла пулевизации число с выхода сумматора П через открытые вентили запрета 12 заносится в предварительно очищенный операционный регистр 1, с выходов которогов следующем такте частично нулевизированное число снова поступает на входы дешифраторов 4, 5 и в сумматор 11, После этого опять производится опрос дешифраторов 4 и последовательный анализ выходных сигналов дешифраторов 4. В связи с тем, что после первого цикла нулевизации в 1-ой и и-ой рабочих ячейках регистра 1 записаны нули, на выходе первого из дешифраторов 4 присутствует нулевой сигнал, который не проходит на вход блока памяти 7, а через управляющий выход первого из переключателей б открывает второй из переключателей б. Если во 2-ой и (г - 1)-ой рабочих ячейках регистра 1 запи- саны ненулевые остатки по 2-му и (п - 1)-му рабочим основаниям, то ненулевой сигнал с соответствующего выхода второго из дешифраторов 4 и связанный с ним открытый переключатель б поступает в блок памяти 7 констант нулевизацни, откуда выбирает соответствующую константу нулевизации. Выбранная константа поступает в сумматор 11 и вычитается из занесенного туда ранее числа полученного после первого цикла нулевизации. Константа подобрана таким образом, что при ее вычитании из частично нулевизированного ,в первом цикле нулевизации контролируемого числа в остатках по ,2-му и (п - 1)-му рабочим основаниям образуются нули, а также сохраняются нули в остатках по 1-му и ю-му рабочим основаниям.Полученное после второго цикла нулевизации число с выхода сумматора 11 через открытые вентили запрета 12 заносятся в предварительно очищенный операционный регистр 1, с выходов которого в очередном такте дважды частично нулевизированное число снова поступает на входы дешифраторов 4 и 5 и в сумматор 11. Процесс нулевизации по-, вторяется аналогичным образом до тех пор пока во всех остатках по рабочим основаниям не окажутся нули. При этом все пере-, ключатели б окажутся открытыми, и сигналс управляющего выхода последнего из переключателей б открывает вентили 8, входные вентили 10 сумматора 11 И запирает вентили запрета 12.В следующем за этим цикле работы устройства выявляется правильность числа или наличие в нем ошибки, т. е. необходимость коррекции. Первая операция этого цикла заключается в занесении в сумматор 11 через открытые входные вентили 10 контролируемого числа из запоминающего регистра 2. Одновременно сигналом с выхода входных вентилей 10 открываются выходные ключи 13.Следующая операция заключается в анализе содержимого ячейки остатков по контрольному основанию регистра 1. Для этого подаются импульсы опроса на дешифраторы. При этом, если на выходе дешифратора б сигнал появляется на нулевой шине, что имеет место при наличии нуля в ячейке по контрольному основанию регистра 1, то это является признаком отсутствия ошибок в контролируемом числе. Если же на выходе дешифратора б появится ненулевой сигнал, что свидетельствует о наличии ошибки в контролируемом числе, то этот сигнал через открытые вентили 8 поступает на вход блока памяти 9 констант ошибок, где по этому сигналу выбирается соответствующая константа. Эта константа подается в сумматор 11 и вычитается из занесенного туда ранее нз регистра 2 контролируемого числа, Константа подобрана таким образом, что при ее вычитании из контролируемого числа имевшая место ошибка в числе устраняется. Исправленное число через открытые выходные ключи 13 поступает на выходные шины 14 устройства обнаружения и исправления ошибок. Если ц коонтролируемом числе ошибки отсутствовали, то никакая константа из блока памяти 9 не выбирается и не вычитается из контролируемого числа. Контролируемое число, не со держащее ошибок, с выхода сумматора 11 через выходные ключи 13 поступает на выходные шины 14 устройства обнаружения и исправления ошибок,10 Предмет изобретенияУстройство для обнаружения и исправленИя ошибок в системе остаточных классов, содержащее подключенные ко входным ши нам операционный и запоминающий регистры с и выходами, дешифраторы, блоки памяти констант нулевизации и ошибок, сумматор, переключатели, вентили и ключи, отличаюиееся тем, что, с целью повышения бы стродействия и упрощения устройства, в нем-ый и (и - 1+1) -ый выходы операционного регистра подключены ко входам соответствующих дешифраторов, выходы которых через последовательно включенные переключа тели соединены со входными шинами блокапамяти констант нулевизацпи, а выходы операционного регистра через дешифратор и подключенные к последнему переключателю вентили подсоединены к блоку памяти кон стант ошибок; выходы операционного ретистра и блока памяти констант нулевизации и констант ошибок непосредственно, а выходы запоминающего регистра через присоединенные к последнему переключателю входные 35 вентили подключены ко входам сумматора,выходы которого через вентили запрета соеди нены со входами операционного регистра и через выходные ключи подключены к выходным шинам успройства.Заказ 1264/4 Изд.1326 Тираж 647 ПодписноеЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССРМосква, Ж, Раушская наб., д. 4/5Типография, пр, Сапунова, 2

СмотретьЗаявка

1644357

Авторы изобретени

В. Ф. Нестерук, В. И. Потапов Омский политехнический институт

МПК / Метки

МПК: G06F 11/10

Метки: исправления, классов, обнаружения, остаточных, ошибок, системе

Опубликовано: 01.01.1973

Код ссылки

<a href="https://patents.su/4-369567-ustrojjstvo-dlya-obnaruzheniya-i-ispravleniya-oshibok-v-sisteme-ostatochnykh-klassov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения и исправления ошибок в системе остаточных классов</a>

Предыдущий патент: Устройство для выделения крайней единицы

Следующий патент: Способ табулирования функции многих

Случайный патент: Устройство для изготовления горловин баллонов