Устройство для параллельного суммированиядвух чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

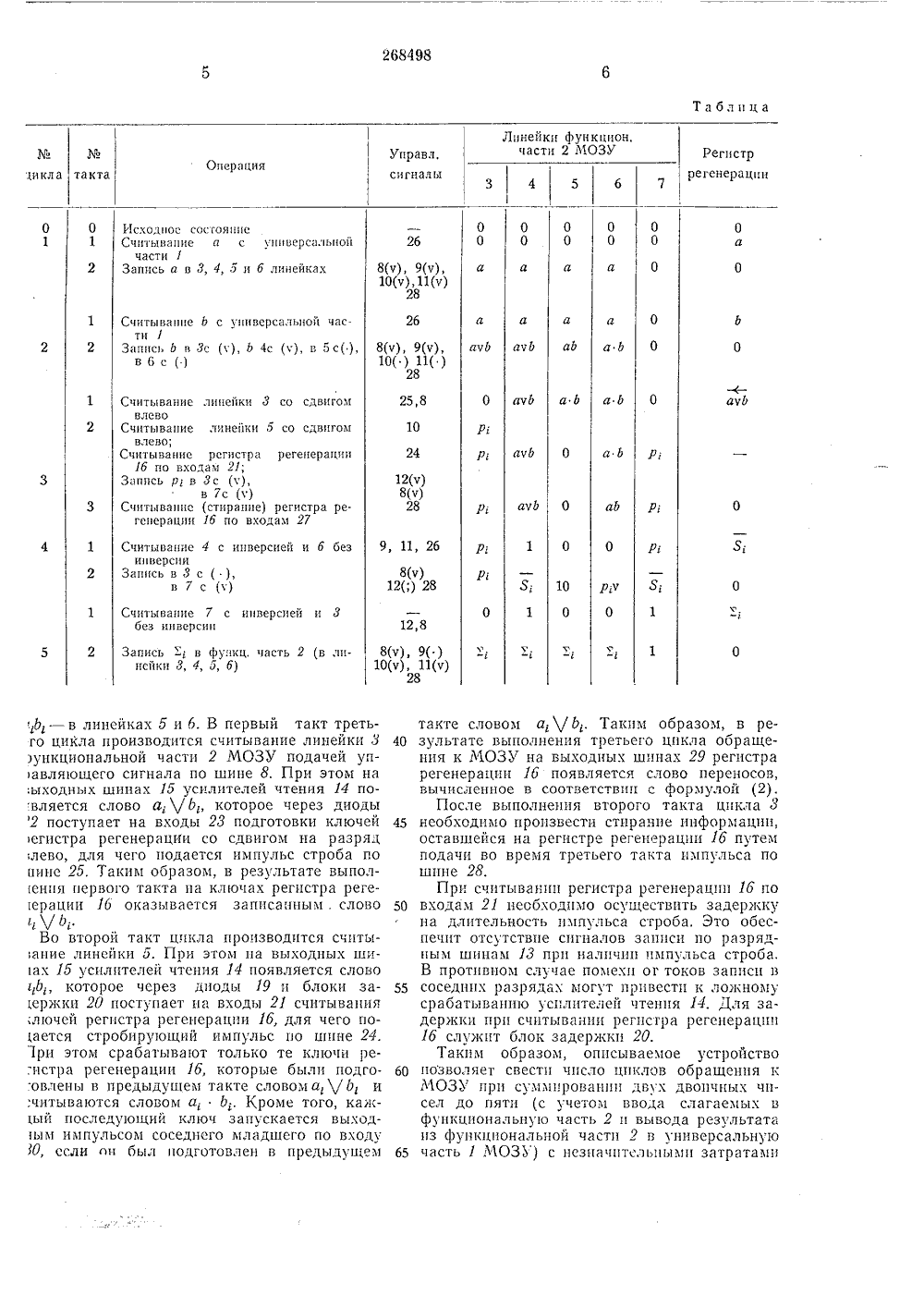

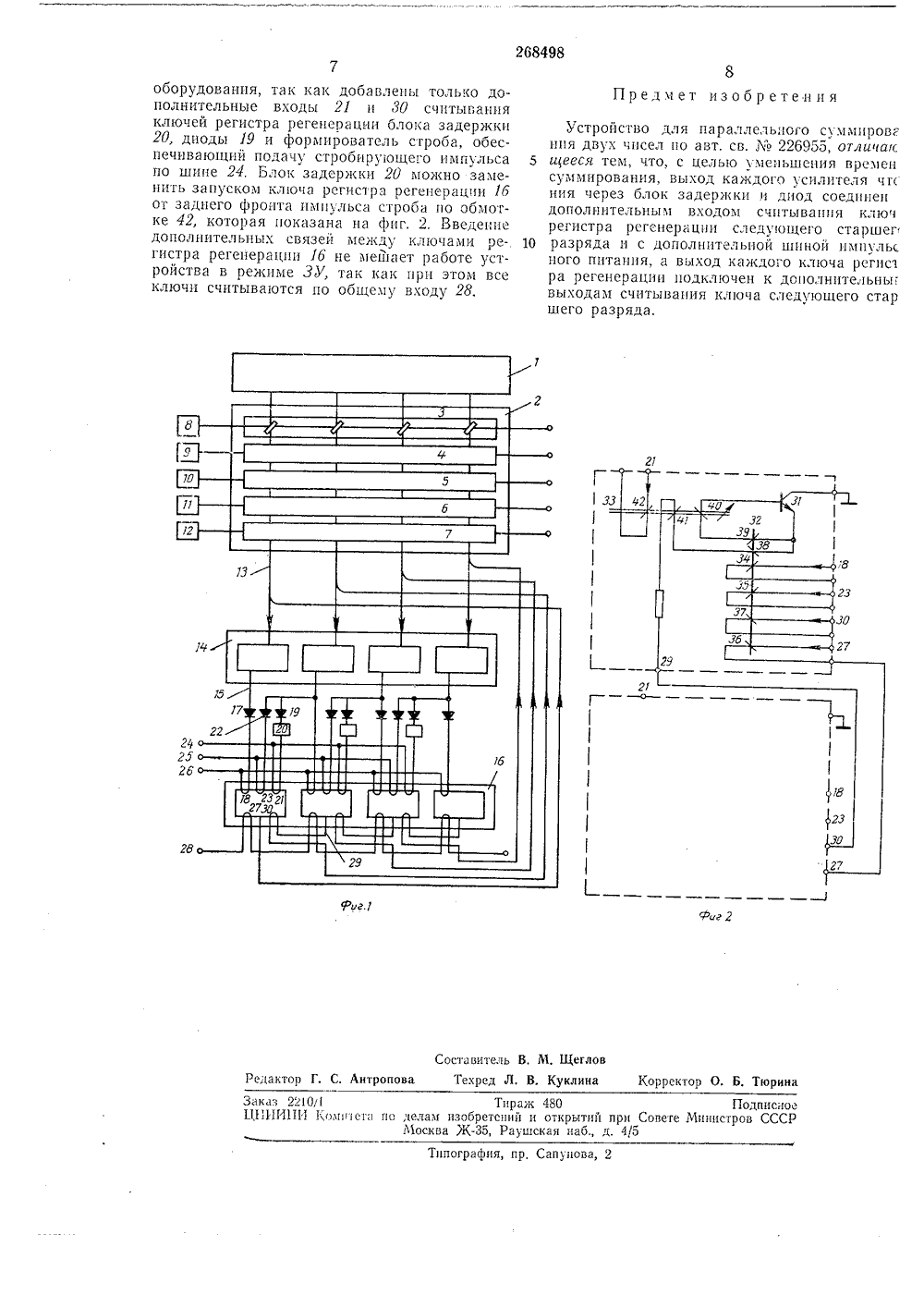

О П И С А Н И Е 268498ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ. Союз Советских Социалистических Респуоликвисимое от авт. свидетельства Ге 226955 Заявлено 15, 1).1968 ( 1241441/18с присоединением заявкил. 21 ат, 3 омитет по делам МПК 6 11 сУДК 681,327.02(0 Приоритет Опубликовано Дата опублик изобретений и открыти при Совете Министров СССР)ЧИРОВАНИЯ ПАРАЛЛЕЛЬНОГДВУХ ЧИСЕЛ УСТРОЙСТВ кении двух )7. разр 5 диьчогической формуле:Р. а;) у (р , - переиос изряд, по следующей х чисе вычпслительнои зовапо в универх цифровых сисперативное запо( т 1) -й разо з 5 с- Я гИзобретение относится ктехнике и может быть испольсальных и специализированнытемах, имеющих магнитное оминающее устройство (МОЗГ).Известно устройство параллельного суммирования двоичных чисел с последовательной реализацией переносов на магнитном оперативном запоминающем устройстве с линейной выборкой, в котором в качестве логического устройства используются специально выделенные линейки МОЗУ (см. авт, св.226955).Однако в таком устройстве для суммирования двух т-разрядных двоичных чисел требуется от пяти до 2 - 3 т циклов обращен я к МОЗУ.Цель изобретения заключаегся в сокращении числа циклов обращения к МОЗУ, требующихся для сложения двоичных чисел. Это достигается тем, что в устройстве вь)ход каждого усилителя чтения через блок задержки и диод соединен с дополительным входом считывания кл)оч регистра регенерации следующего старшего разряда и с дополнительной шиной импульсного питания, а выход каждого ключа регистра регенерации подключен к дополнительным выходам счит )павия ключа следующего старшего разряда.Цель изобретения достигается путем вычисления слова переносов, возника)ощих прп слорг - перенос и ( - 1) -и, азряд;а) и ); - сла)аемые )-го разряда;Действительно, перенос пз )-го в (г+ 1)-й разряд может возникнуть в двух слцаях: при наличии едишп ь обоих слагаемых )-го разряда; при пали шп едишщы ь одном из слагаемых -го разряда и переносе в -и разряд из ( - 1) -го разряда.Формул (1 можно привести к вид.:г. -= ; ,) 0(гг,), ,/ д). (2) Для вычисления слова переносов по формуле (2) выходы усилителей чтения матрицы МОЗУ через лиоды и устройства задержки соединяются со специальными входами считызания кл)очей р гистра регенерации; кроме того, выход ключа -го разряда регистра регенерации по специальному входу поступает и считывание ключа (+ 1)-го разряда. Окончателыця сумма двух двоичных чисел г-го разряда выражается следующей гоги 1 ской формулой:г = ОХ рМК 50 60 Где .г - г-и разряд суммы слагаемых и и Ь;р, - перенос в г-и разряд;Зг - предварительцая сумма (без учетапереносов) г-го разряда.Логическую формулу (3) можно привести квиду: Из формулы (4) видно, что для вычпсленця Ег достаточно иметь инвертированное значение предварительной суммы 5,. и прямое значение переноса в г-й разряд р;.Инвертированное значение 5 г может быть вычислено5 г - : аг гг Ьг / агЬг, (5) Тогда слойение двух двоичных чцсел может быть выполнено по следующему алгоритму: ввод числа а в специально выделенные для выполнения логических операций линейки МОЗУ; ввод числа Ь е специальное выделенные для выполнения логических операций линейки МОЗУ с образованием выражений а,./ Ь, и а,.Ь,; образование слова переносов по формуле (2); образование инвертированного значения предварительной суммы 5, по формуле (ос); образование окончательной суммы слагаемых а и Ь по формуле (4) и запись ее в МОЗУ.Из изложенного видно, что алгоритм сложения двух двоичных чисел при помощи предлагаемого устройства состоит из пяти циклов обращения к МОЗУ. Цикл 3 выполняется при помощи дополнительных связей в предлагаемом устройстве. Дополнительные связи, введенные в предлагаемое устройство, существенно уменьшают время сложения двоичных чисел и не мешают использованию предлагаемого устройства в качестве обычного МОЗУ,На фиг. 1 изображена схема описываемого устройства сложения двоичных чисел со сквозным переносом; на фиг. 2 - два ключа регистра регенерации.Устройство состоит из универсальной части 1 и функциональной части 2.Функциональная часть 2 состоит из пяти числовых линеек 3 - 7. Каждая линейка функциональной части имеет одну адресную шину 8 - 12. Выходы (разрядные шины) 13 матрицы МОЗУ соединены с усилителями чтения 14. Выходы 15 усилителей чтения подключены к регистру регенерации 16, прчем выход г-го усилителя чтения подключен через диод 17 ко входу 18 подготовки ключа г-го разряда регистра регенерации 16, через диод 19 и блок задержки 20 ко входу 21 с штыванпя ключа (г + 1)-го разряда регистра регенерации 16, а через диод 22 - ко входу 23 подготовки ключа (г + 1)-го разряда регистра регенерацииИмпульсное пигание оконечных каскадов усилителей чтения 14 может подаваться либо по дополнительной шине 24 импульсного питания, либо по шине 25, либо по шине 26. Специальные входы 27 считывания ключей ре 10 15 20 25 30 35 40 45 гистра регенерации 16 соединены друг с другом ц имеют общий вход 28. Выход 29 ключа г-го разряда регистра регенерации 16 подключен ко входу 30 считывания ключа (г+ 1)-го разряда и к уазрядным шинам 13 матрицы МОЗУ.Ключ г-го разряда рсгцстра регенерации 16 состоит цз транзистора 31 а - р - гг, магнитного сердсчнгна 32 с ПП 1, регулируемого магнитного сердечника 33. Магнитный сердечник 32 имеет обмотки подготовки 34 ц 35, обмотки считывания 36 и 37, обмотку положглтельной обратной связи 38 и базовую обмотку 39. Магнитный сердечник 33 имеет базовую обмотку 40, обмотку положительной обратной связи 41 и обмотку 42 запуска транзистора 31 от заднего фронта импульса, поступающего на вход 21. Лдресные шины 8 - 12 функциональной части 2 подключены к выходам формирующих реверсивных ключей; каждая адресная шина соединена со своим ключом. С помощью этих ключей в адресные шины могут подаваться в такт записи или в такт считывания импульсы полоо тока или цгпульсы полутока,Рассмотрим работу предлагаемого устроиства при образовании слова переносов по формуле (2), пользуясь чертежом и таблицей, в которой показана последовательность выпол. пения операций, сочетания управляющих сигналов, необходимые для выполнения каждой операции, а также содержимое линеек фуглкциональной части матрицы МОЗУ и регистра регенерации 16 после выполнения каждой операции, Таблица составлена по описанному ранее алгоритму, в котором слово переносов образуется в результате выполнения третьего цикла обращения к МОЗУ.Каждый цикл обращения к МОЗУ состоит из выполнения считывания матрицы МОЗУ с записью считанного кода на регистр регенерации и передачи кода с регистра регенерации обратно в матрицу МОЗУ, причем как во время считывания, так и во время записи могут производиться логические операции с кодами. Операция поразрядной дизъгонкцци выполняется так же, как и запись по принципу совпадения полутоков, подаваемьгх по разрядным и по адресным шинам, но без предварительного стирания содержимого линейки. Операция проразрядной конъюнкции вылолняется подачей полного тока в сторону О по адресноц шине одновременно с кодом, поступающим по разрядным шинам. Операция инвертирования кода выполняется при считывании линейки имггульсом олиного тока в сторону 1, подаваемым по адресной шипе. Кроме того, при одновременном считывании нескольких линеек функциональной части 2 на выходных шинах 15 усилителей чтения 14 появляется код, являющийся диз ьюцкцией кодов, считываемых с линеек функциональной части 2.Перед началом третьего цикла обращения к МОЗУ слово а;/Ьг записано в линейках 3 и 4 функциональной части 2 МОЗУ, а словоРегистр7регенерации Управл, сигналы Операция такта цикла 3 4 5 6 0 а 26 8(ч), 9(ч),10(ч),11(ч)28 26 ичЬ ачЬ аЬ а Ь 8(ч), 9(ч),10( ) 11( )28-С - ачЬ линейки 3 со сдвигом линейки 6 со сдвпгоги 0 ачЬ а Ь а Ь 25,8 Считывание влево Считывание влево; Считывание 16 по вхо Запись р; вИсходпос состо 5 исСчитывание а с уиивсрссыойчасти 1Запись а в 3, 4, б и б линейках Считывание Ь с универсальной чвс.ти 1Запись Ь в 3 с (ч), Ь 4 с (ч), в 5 с( ),в 6 сСчитывание 4 с инверсией и б бсвинверсииЗаписьв 3 с( ),в 7 с (ч) Считывание 1 с инверсией и 3 без инверсии Запись Хс в фуикц. часть 2 (в лпнсики 3, 4, 6, 6) А - в линейках 5 и 6. В первый такт третьго цикла производится считывание линейки 8 )уцкциональной части 2 МОЗУ подачей упавляющего сигнала по шине 8. При этом на ;ыходных шипах 15 усилителей чтения 14 повляется слово а;/6 которое через диоды 2 поступает на входы 28 подготовки ключей егистра регенерации со сдвигом на разряд ;лево, для чего подается импульс строба по пине 25. Таким образом, в результате выполенця первого такта па ключах регистра регеерациц 16 оказывается записанным . слово ;ЧЬВо второй такт ццкла производится счцты:ание линейки 5. При этом ца выходных шиах 15 усилителей чтения 14 появляется слово ,Ь которое через диоды 19 ц блоки задержки 20 поступает на входы 21 считывания ;лючсй регистра регенерации 16, для чего поается стробирующий импульс по шине 24. три этом срабатывают только те ключи ре.истра регенерации 16, которые были подгоовлены в предыдущем такте словома,х/д, и ;читываются словом а, 6,. Кроме того, кажтый последующий ключ запускается выходым импульсом соседнего младшего по входу 10, если ги был подготовлен в предыдущем такте словом а,./6;. Таким образом, в ре зультате выполнения третьего цикла обращения к МОЗУ на выходных шинах 29 регистра регенерации 16 появляется слово переносов, вычислеппое в соответствип с формулой (2).После выполнения второго такта цикла 8 45 необходимо произвести стирачце информации,оставшейся на регистре регенерации 16 путем подачи во время третьего такта импульса по шине 28.При считывании регистра регенерации 16 по 50 входам 21 необходимо осуществить задержкуна длительность импульса строба. Это обеспечит отсутствие сигналов записи по разрядным шинам 13 прц налп шп импульса строба.В противном случае помехи ог токов записи в 55 соседних разрядах могут привести к ложномусрабатыванию усилителей чтения 14. Для задержки прц считывании регистра регенерации 16 служит блок задержки 20.Таким образом, описываемое устройство 60 позволяет свести число циклов обращения кМОЗУ прц суммировании двух двоичных чисел до пяти (с учетом ввода слагаемых в функциональную часть 2 и вывода результата цз функциональной части 2 в универсальную 65 часть 1 МОЗУ) с незначительными затратами268498 Устройство для параллельного суммнрове ння двух чисел по авт, св. Ъо 22 б 955, отличат 5 и 1 ееся тем, что, с целью уменьшения времен суммирования, выход каждого усилителя чгс ния через блок задержки и диод соединен дополнительным входом считывания ключ регистра регенерации следующего старшег 10 разряда и с дополнительной шиной импульс ного питания, а выход каждого ключа регист ра регенерации подключен к донолннтельны: выходам считывания ключа следующего стар шего разряда, Составитель В, М, Щегловнтропова Текред Л. В. Куклина Корректор О, Б. Тюрина Редактор Подписноее Министров СССР Тираж 480 и 1 ста по делаы изобретений и открыт Москва Ж, Раушская набЗак 1, 9 оО 1.111 ИИ 11 И 1при Сод. 1(5 пография, пр, Сапунова, 2 оборудования, так как добавлены только дополнительные входы 21 н 30 считывания ключей регистра регенерации блока задержки 20, диоды 19 и формирователь строба, обеспечивающий подачу стробирующего импульса по шине 24. Блок задержки 20 можно заменить запуском ключа регис 1 ра регенерации 1 б от заднего фронта импульса строба по обмотке 42, которая показана на фнг. 2, Введение дополнительных связей между ключами регистра регенерации 1 б не мешает работе устройства в режиме ЗУ, так как при этом все ключи считываются по общему входу 28,Предмет изобретения

СмотретьЗаявка

1241441

В. Г. Колосов, А. Г. Леонтьев, В. Ф. Мелехин, Б. А. илови, Н. И. Радомысльска, В. Н. Тисенко ГПд Ленинградский политехнический институт М. И

МПК / Метки

МПК: G11C 11/02

Метки: параллельного, суммированиядвух, чисел

Опубликовано: 01.01.1970

Код ссылки

<a href="https://patents.su/4-268498-ustrojjstvo-dlya-parallelnogo-summirovaniyadvukh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для параллельного суммированиядвух чисел</a>

Предыдущий патент: Устройство для воспроизведения сигналов,

Следующий патент: Способ изготовления блока магнитньгх головок

Случайный патент: Самосвальное транспортное средство