Многофункциональная логическая схема в интегральном исполнении

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 236530

Авторы: Бабичева, Евреинов, Прангишвили, Ускач

Текст

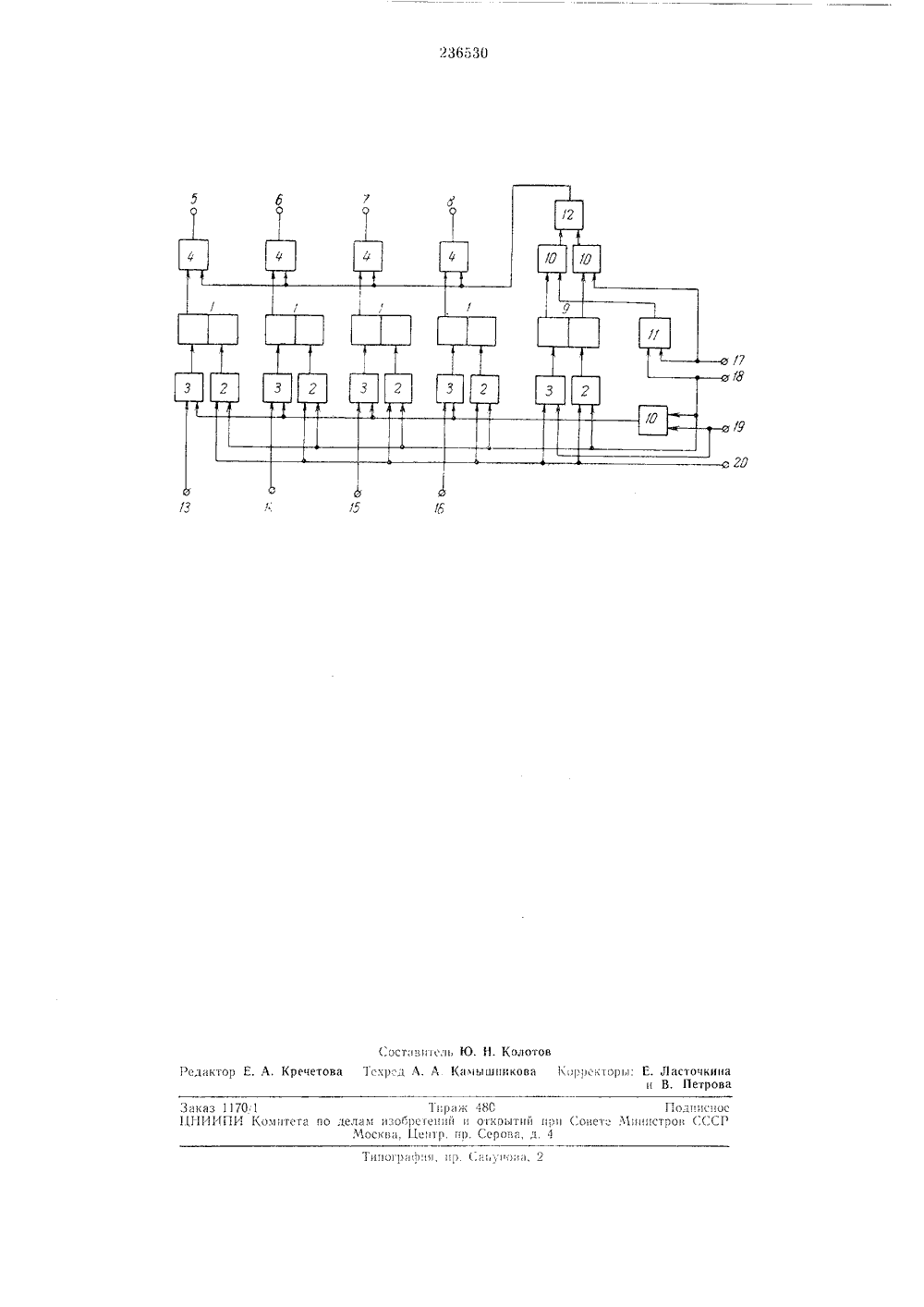

гО П И С А Н Й е 236530ИЗОБРЕТЕНИЯ Союз Советских Социзлистических РеспубликК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 3 ависи мое от авт, свидетельства ЛЪ.ПК Н 03 Комитет по делам зобретений и открытийДК 681.325.65(088.8) ри Совете Министров СССРАвторыизобреген И. В. Прангишвили, Е. В, Бабичева, М. А. Ускач, Э. В. Евреинов, А, И, Мишин, М. А, Королев, В. М, Гусаков и Е, С. Сельков Институт автоматики и телемеханики (технической кибернетики) аявитель ОГОФУНКЦИОНАЛЪНАЯ ЛОГИЧЕСКАЯ СХЕ В ИНТЕГРАЛЬНОМ ИСПОЛНЕНИИая логи- вычислиользована и, регист- вычисли- томатики ая многофункциональ тносится к элементах ки и может быть исп мента памяти, задержк гического элемента в нах и устройствах а ых схемах. Предложенн ческая схема о тельнсй техни в качестве эле ра сдвига, ло тельных маши на пчтегральн едложенная многофункционал я схема в интегральном испол ащая триггеры, входные схемы овки в нуль и единицу,И - НЕ, управляющий равляющие схемы И, - НЕ, отличается тем, ч чные входы тритгеров выходами входных схем И -ьная логинении, со- И - НЕвыходныетритгерИ - НЕ,ск схемь у ИЛИ едини ны св неи соедине- Е устаИзвестные логические интегральные схемы являются большей частью однофункциональными, как например, схема сдвигового регистра, ячейки оперативной памяти, логические схемы типа ИЛИ - НЕ и т. д., либо представляют собой простое объединение в одном корпусе не связанных друг с другом логических схем типа И, ИЛИ, задержка с большим числом индивидуальных входов и выходов, что приводит к снижению надежности устройства, так как надежность внугренних компочентов интегральных схем значительно выше надежности внешних выводов и паек. новки в единицу, одни входы которых соответственно подключены к единичным входам схемы, а вторые входы соединены с выходом управляющей схемы И, один вход которой 5 подключен ко входу управляющей схемыИ - НЕ, устанавливающей управляющий триггер в единицу, и к первому управляющему входу, а другои вход - со вторым управляющим входом схемы, Единичные выходы О триггеров через выходные схемы И - НЕподключены к выходам схемы, вторые входы выходных схем 11 - НЕ соединены с выходом управляющей схемы ИЛИ - НЕ, соединенной через вторую и третью управляющие 5 схемы И с выходами управляющего триггера, а вторые входы управляющих схем И подключены и третьему управляющему входу, один непосредственно, а другой - через управляющую схему 11 - НЕ, другой вход ко- О торой подсоединен ко второму управляющемувходу и ко входам схем И - НЕ установки триггеров в нуль, другие входы которых подключены к четвертому управляющему входу и ко входу схемы И - 1-1 Е установки управ ляющего триггера в едпницу.Такое выполнение позволяет расширитьфункциональные возможности и сократить число типов интегральных схем.Описываемая многофункциональная логи ческая схема в интегральном псполненип приведена на чертеже.(Гсм сотстетуощег.) еолцровдця )холс.Гс(л 1:1 с 1 х ИРЯЗлпоц(чх вхо Ях 7 2( елиииИях Входах 18 16 предлагаемую схс(10 жио 1 дсрдивя 1 ь ня Вьполненис Оц(ОЙ 13 сллуСщих основных функшй:г);:спец олцоролцой структуры;О ) О И С ) Д 1 Ц Б Ц О й Ц Д М 51 Т И В Ы И 1 С, И Т СГ 1 Ы 0 Й М с- цииы смеостю 4 бит с коорлицатной здписоСч;ПБДЦ;СМ;Б) гстцрЕХраэряЛИОГО ПдрдЛЛСЛЬНОГО ЗЯПОи 1(дю;цсго регистра;г) чстырсхразрядцого ЧстЫрЕХта ЕПОГО -5 (лв:(говоо рсцст)д (половина),;1) БОСЬ:(1:(рс(3)ядцого сЕТЫр(.:;ТЯЕПС(0 рде - ц)с,(сл итс 1;1 иГ 13 л(,(ОВ (половина);ЛБ",ХТДЕ 1 ПОГО Э,1 СМСИГД ЗДДСРЖКИ;)(.ЛС Бс.,ци (цолвина); 30Яс) Л ЦО ГО:3 ХОЛОБ 010 .1 ОИ ЧССЕОГО ЭЛСХ СЦ,1:)П 1(310(3 ХОЛО 3 ОГО ОИЧССЕО 0 ЭЛСХС(. Гс 1 с 11.11 Сре(:.СЛ ПЫС функцц реаШЗуатгя ( Л.- 35 л(, нп 1.11(м Обрдзом.у ц е и ц 5( я и с й к ц о л ц о р о л 1 о й с т р х и т у р ы. Совоеуп;ость мцогофуцкццо- ИДЛПЬ:Х ЛОГПЧССЕИХ СХСМ, СОЕДЦЦСЦЦЫХ ХСЕДУ собоц ь Бил решетки, образует олиоролп, ю 40 СТРУКТУРУ, ПРИ 1 ЕМ ЕЯЖЛЯ 51 ЛОГИЧССЕЯ 51 С)с 51 ВГ 151 стс 5 51 сиеОЙ сГруктрь. СПГнс 1.ы О (.О.сслцихчсек (например, от четырех) иолдюгся цд упрявл 5(.оцдц вход 17. Сигналы с выколов 6 - -8 поступают, В свою очередь, цд уп равляющце 1(холы 17 окруждощцх сосслцих ячеек. .,г(разляющцс входы 18- -20 исцог(.БуОТС 51 ЛГ 15(: СТ)01 Еи 51 СЙКИ СТР) Е ( РЫ С ПОМО- цПо хира;л 510 цсго триср 1 9 ид Бь(посшс (с одцои з Г 1 огпссеих ф(неций 11 -П., 50 либо 14 цдл сигналахи, подаццы)ш на уц) а БГ 15(10 Ц(й 13 ХОЛ 17 (Гр И Гср 9 (.ОО ГБСТС 1 БСНИ 0 Б ЦМГС 3Х Г 1 ИОО Б СЛПНИЧНОМ СОСТОЯ.ИИ) .С помощью елшичцых Вколов 18 - -16 соотьетствуощце триггеры 1 устацавлцьаются В сдци шое состояние, при этом разрывается информационна 1 сВ 513 ь )1 ежлдянцОЙ 51 СЙкОЙ ц соответствующей соседней. 1 аличию связи псжлу ячейками соотвстствуот пулевые состояния тригг роз 1. 60Оперативная память вы 1(слительной машины емкостьо 4 б Г с коорлицдтной записью и с:иты- В я и е мэяпись инфо,):(яици В триГГер 1имеющейся нд слццичцых Бхолдх 18 - 16, про.)анись информации извне в сдвиговыи ре.пстр 1:роцзвоцится по елиничцым входам 8 - . 1;33 олигс 51 цуге.( олцовр монной цолачц (лц. цчиых сиГ 311013 цд , прсц;1 яющие В.;Оды 18 и 19. С:пг;ывднцс здццсдИой шформации ос;- и(ссг 3 л 5 ется при полачс единичных сигналов цд мирЯБля 0 цис Входы 1/ и 18, при этО) с выколов схемы 6 - 8 снимается прямой кол. Стирание информации производится путем полачи слицичых сигналов олновременно нд управлюшс входы 18 и 20. Для увеличения еолпчсстпд рязр 51 лов 13 слОВс цсобхолпО Оо 1- С;ццц;1 цс(КОЛЬКО СХС 3 СОО) БСТСТВЕИП цо17 18 19Р 9а( (.Ы р С Х р Я 3 р 51,1 П Ы И П Я р д 1.С Г Ь;(ы й 3 до м:ц а ю щ и й р ет;с т р. Запись, считывание и стирацис информации Б отл Гчие от функщи оперативной цамяп( Осуществляется по одной коордвате при подаче СЛшичиого счгнала ца управляющие вхолы 19, 17, 20. 11 а уцравляк)щий Вход 18 постояц - О ЦОЛаетСЯ НаПРЯжЕЦИЕ ПцтаНИЯ.с Е т Ы р Е Х р я 3 р 53 Л ц Ы Й Ч С т Ы р Е Х Г а К тцый слвцговый регистр, распределите ь и (пульсов и лвухта к гцый элемент задержкиреле времени. Дл 1 построения слвигового регистра, распрелелцтсля ихпхльсов и элемента задержки -- рсле времен:1 необходимо соединить чегное 1 ю)1 Исст 130 (мин(мум две) хПОГОф 1 кцио. Ца.1 ЬЦХ .101 И 1 ЕСКЦХ СХЕХ. ПРИ 31 ИГ ЛЕИСГВИЯ этих строОтв основан на том, по информация поочередно персписывдстс 1 из цсчетцых (хсм в чеп(ые и обратно. С виг шформации осуцс(твлястся Вследствие того, что Выход еяжОго из четырех разрядов цсчстой мнОГО- фУЦЕ(с О: ДЛЬЦОй СХСМЫ СОЕДИНЯЕТСЯ С ЕЛ Ш:Ч- (:ым Входом сделкоюцего разряда четной мноофуцеццональцой схемы, а выход каждого из четырех разрядов четной схемы - = единичным входом соответствующего разряла нечетной схемы. При этом в сдвиговом регистре и рдспрсделителе импульсов после каждой переписи информации происходит очистка имяти триггеров 1 соответствующей логической схемы. Для реализации этих операций ца управляющие )холы многофункциональных схем подается четырехтактная серия импульсов.При работе элемента залержк; о(шстка памяти тригеров 1 не производится, поэтому Б этом случае достаточно двухтактцой серии цм- ПУЛЬСОВ. г,.(51 ВЫИОЛНЕЦИЯ УКаэаННЫХ фУНКЦИй необходимо:опарно соединить единичные входы и выходы нечетной и четной многофункциоцальшгх логических схем, обозначенных соответственно с индексамии 2, в соответствци с таблицей 1.1 б нечетной логической схемы. На единичный вход 18 четной логической схемы подается, в зависимости от назначения, напряжение питания (сдвиговый регистр), импульсный сигнал (распределитель импульсов) либо единичный скачок (элемент задержки). На управляющие входы 17 - 20 подаются тактовые импульсы Т,; Т,; Т,; Т, и напряжение питания в соответствии в табл. 2. ТЗОлпца 2 Управляющие входы 1 О лОо Д РЕ гб17;19,20.,19,19,20.,17,;19., 20,19.,19.,20,17,; 17 18,; 18.,18,;, 17,; 17.,Напряжение питания 18., 18; 18.,Многовходовые логические элем е н т ы И - НЕ, И. Выходы 5 - 8 нескольких элементов объединяются на управляющем входе 17. Если управляющий триггер 9 многофункциональной логической схемы находится в нулевом состоянии (на управляющие входы 18, 20 подано напряжение питания), то на любом из выходов 5 - 8 реализуе 1- ся функция И - НЕ от переменных, поданных на управляющий вход 17. Если управляощий триггер 9 находится в единичном состоянии (на управляющие входы 19, 20 подано напряжение питания), то реализуется функция И от тех же переменных. В последнем случае требуется предварительный сброс триьеров 1 путем подачи однократного единичногосигнала на управляющий вход И. Предмет изобретенияМногофункциональная логическая схема винтегральном исполнении, содержащая триггеры, входные схемы И - НЕ установки в нуль и единицу, выходные схемы И - НЕ, управляющий триггер и управляющие схемы 11, И - НЕ, ИЛИ - НЕ, отличающаяся тем, что, с целью расширения функциональных возможностей и сокращения числа типов 15 интегральных схем, в ней единичные входытриггеров соединены с выходами входных схем И - НЕ установки в единицу, одни входы которых соответственно подключены к единичным входам схемы, а вторые входы 20 соединены с выходом управляющей схемыИ, один вход которои подключен ко входу управляющеи схемы И -НЕ, устанавливающей управляющий триггер в единицу, и к первому управляющему входу, а другой 25 вход - со вторым управлгпощим входом схемы; единичные выходы трип еров через выходные схемы И - НЕ подключены и выходам схемы, вторые входы выходных схем И - НЕ соединены с выходом управляющей схемы 30 ИЛИ - 1-1 Е, соединенной через вторую итретью управляющие схемы И с выходами управляющего триггера, а вторые входы управляющих схем И подключены к третьему управляющему входу, один непосредственно, 35 а другой - через управляющую схему И 11 Е, другой вход которой подсоединен ко второму управляющему входу и ко входам схем И - 1-1 Е установки триггеров в нуль, другис входы которых подключены и чствсрто му управляющему входу и ко входу схемыИ - НЕ установки управляющего триггера в единицу.77ЭСостдвггсли Ю. Н. Колотов Редактор Е. А, Кречетова Тскрсп А. А Камышиикова Корректоры: Е. Ласточкинаи В. Петрова Заказ 11701 Тираж 48 В Попиисиос 1 НИИПИ Комитета по делам изобретений и открытий ири Совет. Аииистроп СССР Москва, Цсит 1 к пр. Серопд, д. 4 Типогрдф ю, и и Сдиуиодд, 2

СмотретьЗаявка

1220180

Институт автоматики, телемеханики технической кибернетики

И. В. Прангишвили, Е. В. Бабичева, А. Ускач, Э. В. Евреинов

МПК / Метки

МПК: H03K 19/20

Метки: интегральном, исполнении, логическая, многофункциональная, схема

Опубликовано: 01.01.1969

Код ссылки

<a href="https://patents.su/4-236530-mnogofunkcionalnaya-logicheskaya-skhema-v-integralnom-ispolnenii.html" target="_blank" rel="follow" title="База патентов СССР">Многофункциональная логическая схема в интегральном исполнении</a>

Предыдущий патент: Одноканальный временной дискриминатор

Следующий патент: Бистабильная схема

Случайный патент: Устройство для наложения проволоки по спирали на заготовку рукава