Устройство для выбора заданного числа повторений двоичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1829029

Авторы: Вдовиченко, Кишенский, Надобных, Христенко

Текст

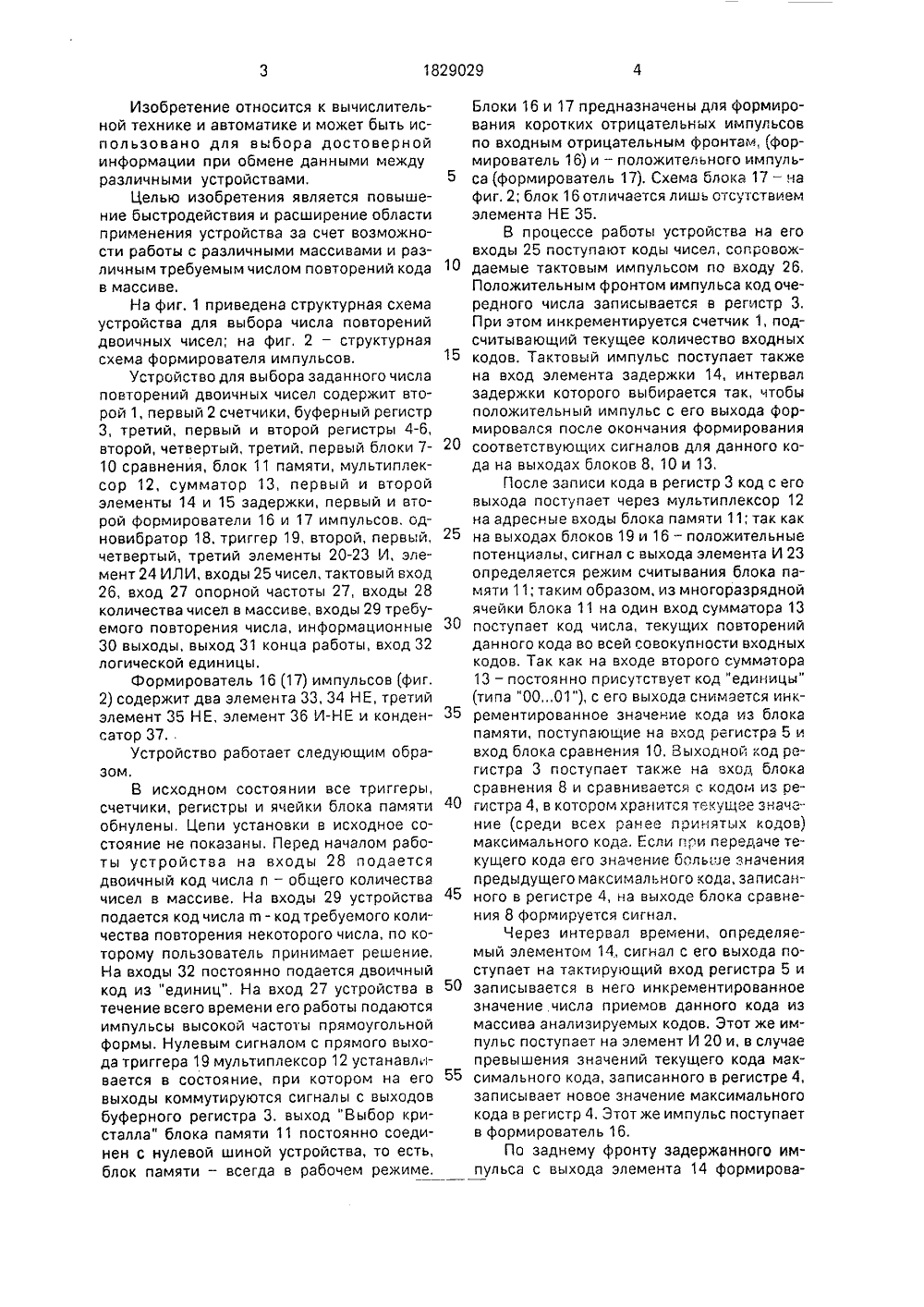

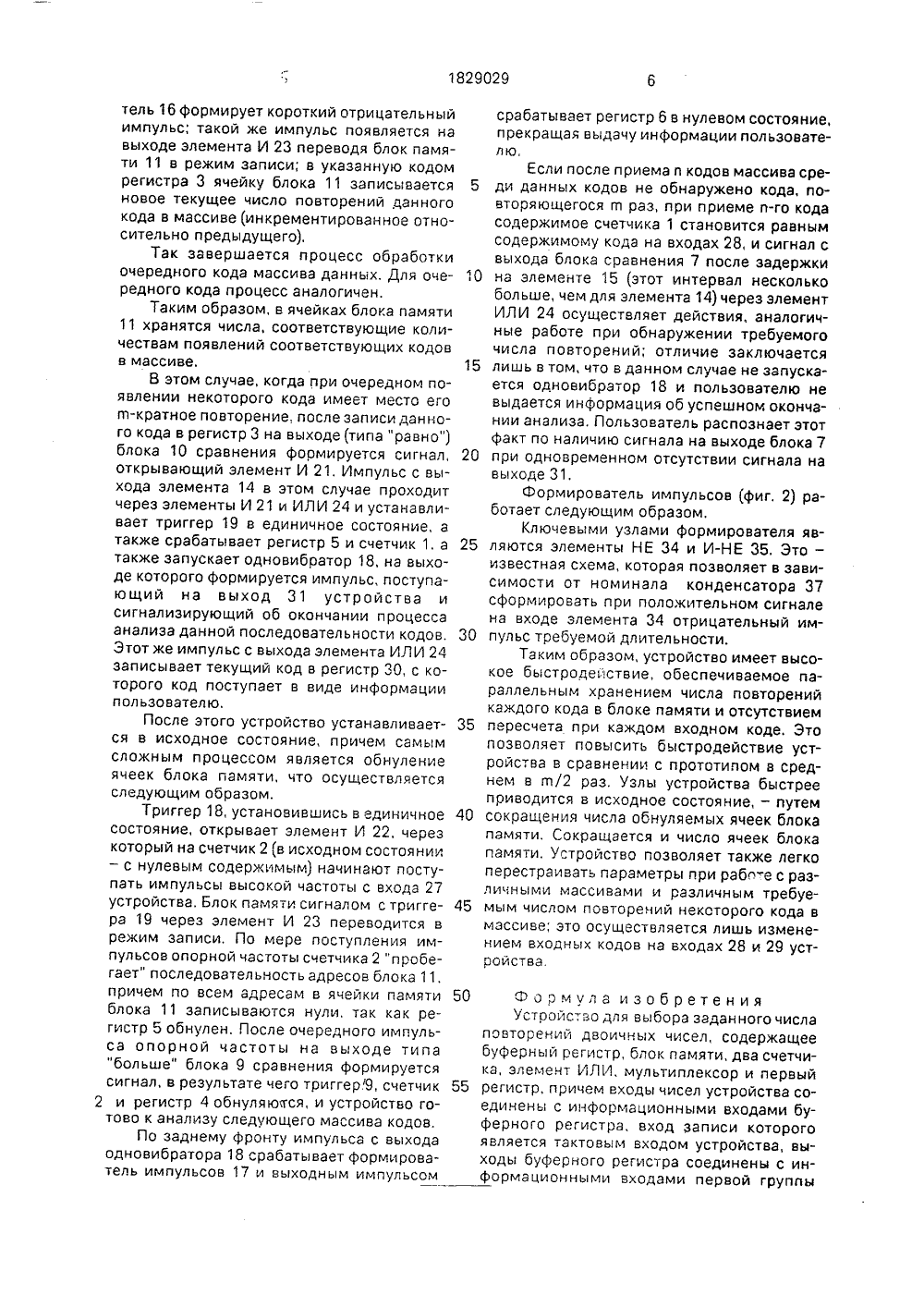

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 19) 151)5 6 00 ГОСУДАРСТВЕННОЕ ПАТЕНТНОВЕДОМСТВО СССР(ГОСПАТЕНТ СССР) Е ИЗОБРЕТЕНИ ВТОРСКОМУ СВИДЕТЕЛЬСТВ 5/2403, Бюл, %27вский институт инженеров гриацииКишенский, Н,С.Вдовиченных и О,Ю,Христенкокое свидетельство СССРкл, 0 06 Р 7.02, 1971.кое свидетельство СССР(54) УСТРОИСТВО ДЛЯ ВЫБОРА ЗАДАН- КОГО ЧИСЛА ПОВТОРЕНИЙ ДВОИЧНЫХ ЧИСЕЛ(57) Изобретение относитной технике и автоматикепользовано ддя выбоинформации при обменеразличными устройствамтения является повышени ся к вычислитель- и может быть исра достовернойданными между и. Целью изобрее быстродействия(21) 48850 (22) 22.11, (46) 23.07. (71) Моско данской а (72) С,)К Е.Н, Надоб (56) Автор К. 378842Автор М. 1267402 и расширение области применения устроиства за счет возможности работы с размещенными массивами и различным требуемым числом повторений кода в массиве. Устройство содержит буферный регистр 3, блок памяти 11, два счетчика 1, 2, элемент ИЛИ 24, мультиплексор 12, первый регистр 4, 5, 6 блоки сравнения 7- 10, триггер 19 формирователи импульсов 16, 17, одновибратор 18, сумматора 13, элементы И, элементы задержки. Более высоксе быстродействие по сравнению с пратогипом обеспечивается параллельным хранением числа повторений каждого кода в блоке памяти.Устройство позводяет легко перестраивать параметры при работе с различными массива- ф ми и различным требуемым числом повторений некоторого кода в массиве изменением кодов общего количества чисел в массиве и требуемого повторения некоторого числа массива. 2 ид.Изобретение относится к вычислительной технике и автоматике и может быть использовано для выбора достоверной информации при обмене данными между различными устройствами.Целью изобретения является повышение быстродействия и расширение области применения устройства за счет возможности работы с различными массивами и различным требуемым числом повторений кода в массиве.На фиг. 1 приведена структурная схема устройства для выбора числа повторений двоичных чисел; на фиг. 2 - структурная схема формирователя импульсов.Устройство для выбора заданного числа повторений двоичных чисел содержит второй 1, первый 2 счетчики, буферный регистр 3, третий, первый и второй регистры 4-6, второй, четвертый, третий, первый блоки 7- 10 сравнения, блок 11 памяти, мультиплексор 12, сумматор 13, первый и второй элементы 14 и 15 задержки, первый и второй формирователи 16 и 17 импульсов, одновибратор 18. триггер 19, второй, первый, четвертый, третий элементы 20-23 И, элемент 24 ИЛИ, входы 25 чисел, тактовый вход 26, вход 27 опорной частоты 27, входы 28 количества чисел в массиве, входы 29 требуемого повторения числа, информационные 30 выходы, выход 31 конца работы, вход 32 логической единицы,Формирователь 16 (17) импульсов (фиг.2) содержит два элемента 33, 34 НЕ, третий элемент 35 НЕ, элемент 36 И-НЕ и конденсатор 37.Устройство работает следующим образом.В исходном состоянии все триггеры, счетчики, регистры и ячейки блока памяти обнулены, Цепи установки в исходное состояние не показаны, Перед началом работы устройства на входы 28 подается двоичный код числа и - общего количества чисел в массиве, На входы 29 устройства подается код числа а - код требуемого количества повторения некоторого числа, по которому пользователь принимает решение, На входы 32 постоянно подается двоичный код из "единиц". На вход 27 устройства в течение всего времени его работы подаются импульсы высокой частоты прямоугольной формы. Нулевым сигналом с прямого выхода триггера 19 мультиплексор 12 устанавл - вается в состояние, при котором на его выходы коммутируются сигналы с выходов буферного регистра 3. выход "Выбор кристалла" блока памяти 11 постоянно соединен с нулевой шиной устройства, то есть, блок памяти - всегда в рабочем режиме. 5 10 15 20 25 30 35 40 45 50 55 Блоки 16 и 17 предназначены для формирования коротких отрицательных импульсов по входным отрицательным фронтам, (формирователь 16) и - положитегьного импульса (формирователь 17). Схема блошка 17 - на фиг. 2; блок 16 отличается лишь отсутствием элемента НЕ 35.В процессе работы устройства на его входы 25 поступают коды чисел, сопровождаемые тактовым импульсом по входу 26, Положительным фронтом импульса код очередного числа записывается в регистр 3, При этом инкрементируется счетчик 1, подсчитывающий текущее количество входных кодов. Тактовый импульс поступает также на вход элемента задержки 14, интервал задержки которого выбирается так, чтобы положительный импульс с его выхода формировался после окончания формирования соответствующих сигналов для данного кода на выходах блоков 8, 10 и 13,После записи кода в регистр 3 код с его выхода поступает через мультиплексор 12 на адресные входы блока памяти 11; так как на выходах блоков 19 и 16 - положительные потенциалы, сигнал с выхода элемента И 23 определяется режим считывания блока памяти 11; таким образом, из многоразрядной ячейки блока 11 на один вход сумматора 13 поступает код числа, текущих повторений данного кода во всей совокупности входных кодов, Так как на входе второо сумматора 13 - постоянно присутствует код "единицы" (типа "00,01"), с его выхода снимается инкрементированное значение кода из блока памяти, поступающие на вход регистра 5 и вход блока сравнения 10, Выходной код регистра 3 поступает также на вход блока сравнения 8 и сравнивается с кодом из регистра 4, в котором хранится текущее значение (среди всех ранее принятых кодов) максимального кода. Если при передаче текущего кода его значение больше значения предыдущего максимального кода, записанного в регистре 4, на выходе блока сравнения 8 формируется сигнал,Через интервал времени, определяемый элементом 14 сигнал с его выхода поступает на тактирующий вход регистра 5 и записывается в него инкрементированное значение числа приемов данного кода из массива анализируемых кодов. Этот же импульс поступает на элемент И 20 и, в случае превышения значений текущего кода максимального кода, записанного в регистре 4, записывает новое значение максимального кода в регистр 4. Этот же импульс поступает в формирователь 16.По заднему фронту задержанного импульса с выхода элемента 14 формирова 18290295 10 15 20 25 30 35 40 45 50 55 тель 16 формирует короткий отрицательныйимпульс; такой же импульс появляется навыходе элемента И 23 переводя блок памяти 11 в режим записи; в указанную кодомрегистра 3 ячейку блока 11 записываетсяновое текущее число повторений данногокода в массиве (инкрементированное относительно предыдущего),Так завершается процесс обработкиочередного кода массива данных. Для очередного кода процесс аналогичен.Таким образом, в ячейках блока памяти11 хранятся числа, соответствующие количествам появлений соответствующих кодовв массиве.В этом случае, когда при очередном появлении некоторого кода имеет место егоп-кратное повторение, после записи данного кода в регистр 3 на выходе(типа "равно")блока 10 сравнения фоомируется сигнал,открывающий элемент И 21, Импульс с выхода элемента 14 в этом случае проходитчерез элементы И 21 и ИЛИ 24 и устанавливает триггер 19 в единичное состояние, атакже срабатывает регистр 5 и счетчик 1, атакже запускает одновибоатор 18, на выходе которого формируется импульс, поступающий на выход 31 устройства исигнализирующий об окончании процессаанализа данной последовательности кодов.Этот же импульс с выхода элемента ИЛИ 24записывает текущий код в регистр 30, с которого код поступает в виде информациипол ьзователю.После этого устройство устанавливается в исходное состояние, причем самымсложным процессом является обнулениеячеек блока памяти, что осуществляетсяследующим образом.Триггер 18, установившись в единичноесостояние, открывает элемент И 22, черезкоторый на счетчик 2 (в исходном состоянии- с нулевым содержимым) начинают поступать импульсы высокой частоты с входа 27устройства, Блок памяти сигналом с триггера 19 через элемент И 23 переводится врежим записи, По мере поступления импульсов опорной частоты счетчика 2 "пробегает" последовательность адресов блока 11,причем по всем адресам в ячейки памятиблока 11 записываются нули, так как регистр 5 обнулен. После очередного импульса опорной частоты на выходе типа"больше" блока 9 сравнения формируетсясигнал, в результате чего триггер 9, счетчик2 и регистр 4 обнуляюгся, и устройство готово к анализу следующего массива кодов.По заднему фронту импульса с выходаодновибратора 18 срабатывает формирователь импульсов 17 и выходным импульсом срабатывает регистр б в нулевом состояние,прекращая выдачу информации пользователю,Если после приема п кодов массива среди данных кодов не обнаружено кода, повторяющегося гп раз, при приеме п-го кодасодержимое счетчика 1 становится равнымсодержимому кода на входах 28, и сигнал свыхода блока сравнения 7 после задержкина элементе 15 (этот интервал несколькобольше, чем для элемента 14) через элементИЛИ 24 осуществляет действия, аналогичные работе при обнаружении требуемогочисла повторений; отличие заключаетсялишь в том, что в данном случае не запускается одновибратор 18 и пользователю невыдается информация об успешном окончании анализа, Пользователь распознает этотфакт по наличию сигнала на выходе блока 7при одновременном отсутствии сигнала навыходе 31.Формирователь импульсов (фиг. 2) работает следующим образом.Ключевыми узлами формирователя являются элементы НЕ 34 и И-НЕ 35. Это -известная схема, которая позволяет в зависимости от номинала конденсатора 37сформировать при положительном сигналена входе элемента 34 отрицательный импульс требуемой длительности.Таким образом, устройство имеет высокое быстродействие, обеспечиваемое параллельным хранением числа повторенийкаждого кода в блоке памяти и отсутствиемпересчета при каждом входном коде. Этопозволяет повысить быстродействие устройства в сравнении с прототипом в среднем в п/2 раз, Узлы устройства быстрееприводится в исходное состояние, - путемсокращения числа обнуляемых ячеек блокапамяти. Сокращается и число ячеек блокапамяти, Устройство позволяет также легкоперестраивать параметры при рабе-е с различными массивами и различным требуемым числом повторений некоторого кода вмассиве; это осуществляется лишь изменением входных кодов на входах 28 и 29 устройства.Формула изобретения Устройство для выбора заданного числаповторений двоичных чисел, содержащее буферный регистр, блок памяти, два счетчика, элемент ИЛИ, мультиплексор и первый регистр, причем входы чисел устройства соединены с информационными входами буферного регистра, вход записи которого является тактовым входом устройства, выходы буферного регистра соединены с информационными входами первой группы1829029 Составитель С,КишенскийТехред М1 оргентал Корректор С.ЮСКО Редактор Т.Иванова Заказ 2475 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР13035, Москва, Ж, Раушская наб 4/5 Производственно-издательский комбинат "Патент", г, Ужгород, ул,Гагарина, 101 мультиплексора, информационные входы второй группы которого соединены с выходами первого счетчика, выходы мультиплексора подключены к адресным входам блока памяти, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия и расширения области применения путем обеспечения возможности работы с различными массивами и различным требусмым числом повторений кода в массиве, в него введены второй и третий регистры, четыре элемента И, четыре блока сравнения, сумматор, два формирователя импульсов, два элемента задержки и одновибратор. причем тактовый Вход устролства соединен со счетным входом БТОООГО счетчика и ч 8 р 83 первый элемент заде.жки с первыми Входами первого и второго элементов И, входом перВого формирователя и входом записи первого регистра, информационные входы которого включены к входам первой группы первого блока сравнения и к выходам сум. матора, входы первой групгы которого подключ 8 ны к Входам логическолг единицы устройства, а входы второй группы соединены с ВыхоДами блока памяти, информационны 8 ВхОды которого соединены с Выходами первого регистра, вход Выбор крисалла" подключен к входу логического нуля устройства, а вход записи "Считывание" соединен с выходом третьего элемента И, первый вход которого подключен к выходу первого формирователя импульсов, а второй - к лнверсному выходу триггера, прямой выход которого подключен к первому выходу четвертого элемента И и к управляюцему входу мультиплексора, выходы второго счетчика соединены с входами первой группы второго блока сравнения, входы второй группы которого являются входами количества чисел в массиве устройства, а выход через второй элемент задержки подключен к первому входу элемента ИЛИ, второй вход 5 которого соединен с входом установки в "0"первого регистра, выходом первого элемента и Входом одновибратора и входом записи второго регистра, а выход подключен к входам установки соответственно в нулевое со стояние второго счетчика и в единичноесостояние триггера, вход установки в нулевое состояние которого соединен с выходом третьего блока сравнения и входами установки в нулевое состояние первого счетчика 15 и третьего регистра, выходы которого соединены с выходами первых групп третьего и четвертого блоков сравнения, входы второй группы третьего блока сравнения подключены к выходам первого счетчика, вход 20 опорной частоты устройства соединен с вторым входом четвертого элемента И, выход которого подключен к счетному входу первого счетчика. выходы буферного регистра соединены с информационными входами 25 второго и третьего регистров и входами второй группы четвертого блока сравнения, выход которого соединен с вторым входом Второго элемента И, выход которого подключен к входу записи третьего регистра, 30 входы второй группы первого блока сравнения являются входами кода требуемого повторения числа устройства, а выход соединен с вторым входом гервого элемента И, выход одновибратора является выхо дом конца работы устройсва и через второйформирователь импульсов подключен к входу установки В нулевое состояние второго регистра, выходы которого являются информационными выходами устройства,

СмотретьЗаявка

4885005, 22.11.1990

МОСКОВСКИЙ ИНСТИТУТ ИНЖЕНЕРОВ ГРАЖДАНСКОЙ АВИАЦИИ

КИШЕНСКИЙ СЕРГЕЙ ЖАНОВИЧ, ВДОВИЧЕНКО НИКОЛАЙ СТЕПАНОВИЧ, НАДОБНЫХ ЕВГЕНИЙ НИКОЛАЕВИЧ, ХРИСТЕНКО ОЛЬГА ЮРЬЕВНА

МПК / Метки

МПК: G06F 7/02

Метки: выбора, двоичных, заданного, повторений, чисел, числа

Опубликовано: 23.07.1993

Код ссылки

<a href="https://patents.su/4-1829029-ustrojjstvo-dlya-vybora-zadannogo-chisla-povtorenijj-dvoichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для выбора заданного числа повторений двоичных чисел</a>

Предыдущий патент: Генератор ортогональных сигналов

Следующий патент: Устройство для накопления чисел с плавающей запятой

Случайный патент: Способ моделирования реиннервации гетеротонически пересаженной почки