Процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1826787

Авторы: Дмитриев, Кляшторный, Макушкин, Миль

Текст

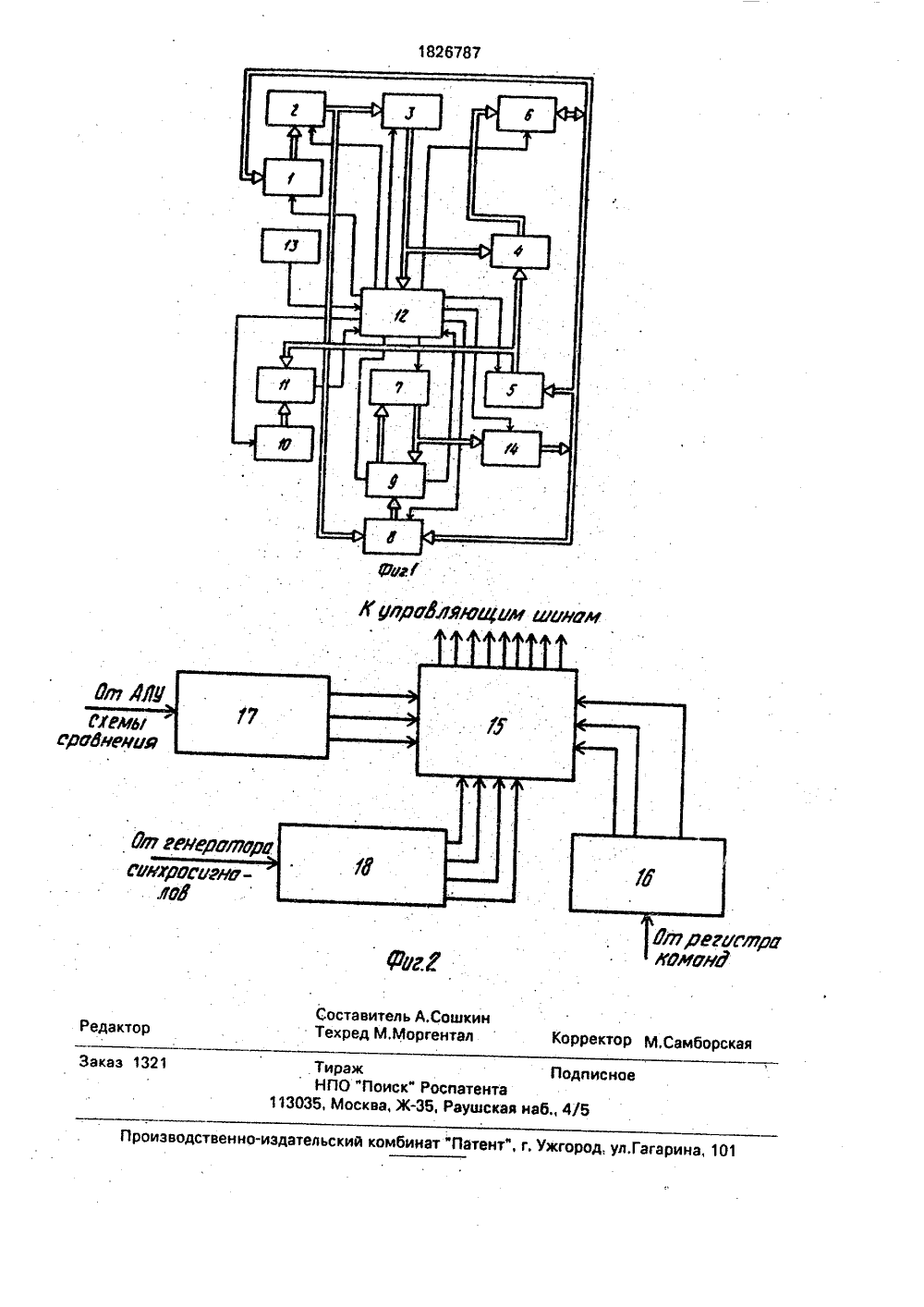

(13) А 1.1 г ЕТЕНИЯ ЕТЕЛЬСТВ ТОРСКОМ е объединени ный М,Ю: ейство ЭВМа, 1988, сруемый/Рук6 РЭ. лектро 44-60.одство к вычислительнои теховано в автоматизироки данных Цель изобСОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХ РЕСПУБЛИКГОСУДАРСТВЕННОЕ ПАТЕНТНОЕВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) 1 ОПИСАН(72) Миль ААМакушкин САДмитриев ВН(56) МикроЭВМ. Кн. 1. Семника; - М.: Высшая школВычислитель программипо эксплуатации 6 Л 3.031.0(57) Изобретение относитсянике и может быть использванном комплексе обработ Я п) 182 б 76 6 Р 1 76 ретения - повышение достоверности работы и повышение производительности Изобретение позволяет непосредственно контролировать хранение программ в памяти, обеспечивает быструю реакцию на возникшую ошибку, что позволяет сократить время на проверку работоспособности машины и локализовать, в случае необходимости, место ее неисправности, Предлагаемый процессор содержит блок памяти программ, блок памяти операндов, регистр команд, регистр операндов, счетчик команд сумматор адреса, индексный регистр, арифметикологическое устройство, формирователь микроопераций, генератор синхроимпульсов, шинный формирователь, счетчик циклов, схему сравнения и шинный коммутатор, 2 ил.Изобретение относится к вычислительной технике и может быть использовано вавтоматизированном комплексе обработкиданных.Целью изобретения является повышение достоверности работы и повышениепроизводительности.На фиг.1 приведена структурная схемапредлагаемого процессора; на фиг.2 - пример реализации формирователя микроопераций.Предлагаемый процессор содержитсчетчик команд 1, соединенный с адреснымвходом блока памяти программ 2, выход которого соединен со входом регистра команд3, сумматор адреса 4, входы которого соединеныы с выходами регистра команд 3 и индексного регистра 5, а выход его соединен садресным входом блока памяти операндов6, регистр операндов 7, шинный коммутатор8, арифметико-логическое устройство 9,счетчик циклов 10, схему сравнения 11 иформирователь микроопераций 12, генератор синхроимпульсов 13 и шинный формирователь 14.Формирователь микроопераций 12 осуществляет управление всеми операциямипроцессора, Специфическое для каждойоперации распределение импульсов поуправляющим шинам осуществляетсяспециальной схемой распределения управляющих импульсов 15, связанной с дешифратором кода операции 16, регистромсостояний 17, служащим для хранения признаковрезультата выполненной операции,регистром сдвига 18, предназначенным длявыработки серии импульсов, распределенных во времени и в пространстве и связанным с генератором 13 синхроимпульсов.Выход каждого его разряда представляетсобой определенный такт работы процессора.Арифметико-логическое устройство 9(АЛУ) имеет параллельные цепи для выполнения всех заложенных в него арифметических и логических операций. Кроме того,устройством формируются признаки результата выполненной операции, например, боЛьше "О", меньше "О", равно "0",признак наличия переполнения оаэряднойсетки,АЛУ 9 может быть реализовано последовательным соединением интегральных микросхем, например 533 ИПЗ.Схема распределения управляющих импульсов 15 представляет собой микропрограммный автомат,.синтезированный на основе системы команд процессора, и может быть реализован на логических ячейках И и ИЛИ, либо на программируемой логической матрице, либо с помощью ПЗУ,Предлагаемый процессор работает следующим образом.5 По включейию питания счетчик команд1 устанавливается в нулевое состояние, запускается генератор синхроимпульсов 13, по сигналам которого формирователь микроопераций 12 содержащий схему распре деления управляющих импульсов 15,дешифратор кода операций 16, регистр состояний 17 и регистр сдвига 18) выдает сигналы синхронизации и управления на все узлы процессора, Выбранная из блока па мяти программ 2 команда считывается в регистр команд 3, а к счетчику .команд 1 добавляется единица, чем подготавливается выборка следующей команды. Старшие разряды регистра команд 3, представляющие собой код команды, поступают на вход формирователя микропередачи 12, а младшие разряды, представляющие собой адресную часть команды, поступают на сумматор адреса 4, где формируется испол нительный адрес для блока памяти операндов 6. Операнд из блока памяти операндов 6 поступает через шинный коммутатор 8 на АЛУ 9, где с ним производится арифметическое или логическое действие, результат 30 которого записывается в регистр операндов 7.В командах условных и безусловных переходов из блока памяти операндов 6 считывается в счетчик команд 1 адрес перехода 35 по программе.Рассмотрим работу процессора приконтролировании правильности хранения программ. В список команд процессора вводится команда "Циклическое сложение" 40 ЦСЛ). Команда выполняется следующимобразом; предварительно (в предыдущей команде) в индексный регистр 5 заносится число, равное длине массива команд, который подлежит контролю. Последней коман дой этого массива является псевдокоманда,дополняющая сумму всех предшествующих ей команд, начиная с команды, следующей за командой ЦСЛ, до нуля.В первом машинном также происходит 50 считывание команды из блока памяти программ 2 в регистр команд 3. Одновременно производится добавление "1" к счетчику команд 1, содержимое которого является адресом блока памяти программ 2. Таким 55 образом подготавливается выборка иэ памяти следующей команды. Во втором такте происходит обнуление регистра операндов 7 и счетчика циклов 10. В третьем такте, являющемся основным тактом команды, происходит сложение в АЛУ 9, содержимогоПРОЦЕССОР, содержащий блок памяти программ, блок памяти операндов, регистр команд, регистр операндов, счетчик команд, сумматор адреса, индексный регистр, арифметика-логическое 2 устройство, формирователь микроопераций, генератор синхроимпульсов, шинный формирователь, причем выходы формирователя микроопераций соедине- З ны с управляющими входами блоков памяти программ и операндов, счетчика команд, арифметика-логического устройства, шинного формирователя, с входами синхронизации регистра команд, ин-З дексн ого регистра, регистра операндов, счетчика команд, выход которого соединен с адресным входом блока памяти программ, выход которого соединен с информационным входом регистра ко манд, выход которого соединен с входом задания команды формирователя микроопераций и первым входом сумматора адреса, вход синхронизации формирователя микроопераций соединен 4 с выходом генератора синхроимпульсов, выход индексного регистра соединен с вторым входом сумматора адреса, выход которого соединен с адресным входом блока памяти операндов, инфор 5 мационный вход-выход которого соединен с входом индексного регистра, входом счетчика команд, выходом шиннОГО формирователя, инфар 5 регистра операндов 7 с прошедшей через шинный коммутатор 8, выбранной из блока памяти программ 2 очередной командой. Результат сложения записывается в регистр операндов 7, В этом же такте происходит добавление "1" к счетчику циклов 10, содержимого которого на схеме сравнения 11 сравнивается с содержанием индексного регистра 5. При отрицательном результате сравнения в следующем такте происходит добавление "1" к счетчику команд 1, т.е, готовится выборка из памяти следующей команды. После этого осуществляется переход к третьему, основному такту команды. Выход из этого цикла происходит по положительному результату сравнения счетчика циклов 10 и индексного регистра 5. В этом случае не происходит добавление "1" к счет- Формула изобретения чику команд 1, а осуществляется переход к выполнению следуьащей команды.Рассмотрим в качестве примера выполнения команды "сложение с запоминанием" 5 с модификацией адреса при помощи индекснога регистра,Первый такт выполняется идентично вовсех командах. Во втором такте происходит формирование исполнительного адреса для 10 блока памяти, операндов б путем сложенияна сумматоое адреса 4 младших разрядов регистра команд Э и содержимого индексного регистра 5. Выбранный по этому адресу операнд в третьем такте складывается с со держимым регистра операндов 7. Полученная сумма в четвертом такте записывается через шинный формирователь 14 в блок памяти операндов 6. мационный выход арифметика-логического устройства соединен с информационным входом регистра операндов, выход которого соединен с первым информационным входом арифметика-логи ческаго устройства и информационнымвходом шинного формирователя, выход признаков результата арифметика-логического устройства соединен с первым входом логических условий формиро вателя микроопераций, отличающийсятем, что, с целью повышения достоверности работы процессора и повышения производительности, в него введены 5счетчик циклов, схема сравнения и шинный коммутатор, первый информационный вход которого соединен с выходом блока памяти операндов, а второй информационный вход соединен 0 с выходом блока памяти программ, управляющий вход шинного коммутатора соединен с выходом формирователя микроопераций, выход шинного коммутатора соединен с вторым инфор мационным входом арифметика-логическаа устройства, счетный вход счетчика циклов соединен с выходом формирователя микроопераций, а выход - с первым входом схемы сравнения, вто рой вход которой соединен с выходаминдексного регистра, выход схемы сравнения соединен с вторым входом логических условий формирователя мироопераций.1826787 ФигЛирсАжющам шинам Составитель А,СошкиТехред М.Моргентал орректор М,Самборска ктор Заказ 13 одпис Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 1 р НПО "Поиск" Р13035, Москва, ЖПпатентаРауаскав наб.,

СмотретьЗаявка

4852497/24, 18.07.1990

Научно-производственное объединение "Сфера"

Миль А. А, Макушкин С. А, Кляшторный М. Ю, Дмитриев В. Н

МПК / Метки

МПК: G06F 15/76

Метки: процессор

Опубликовано: 20.12.1995

Код ссылки

<a href="https://patents.su/4-1826787-processor.html" target="_blank" rel="follow" title="База патентов СССР">Процессор</a>