Кодер знаковой дельта-модуляции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

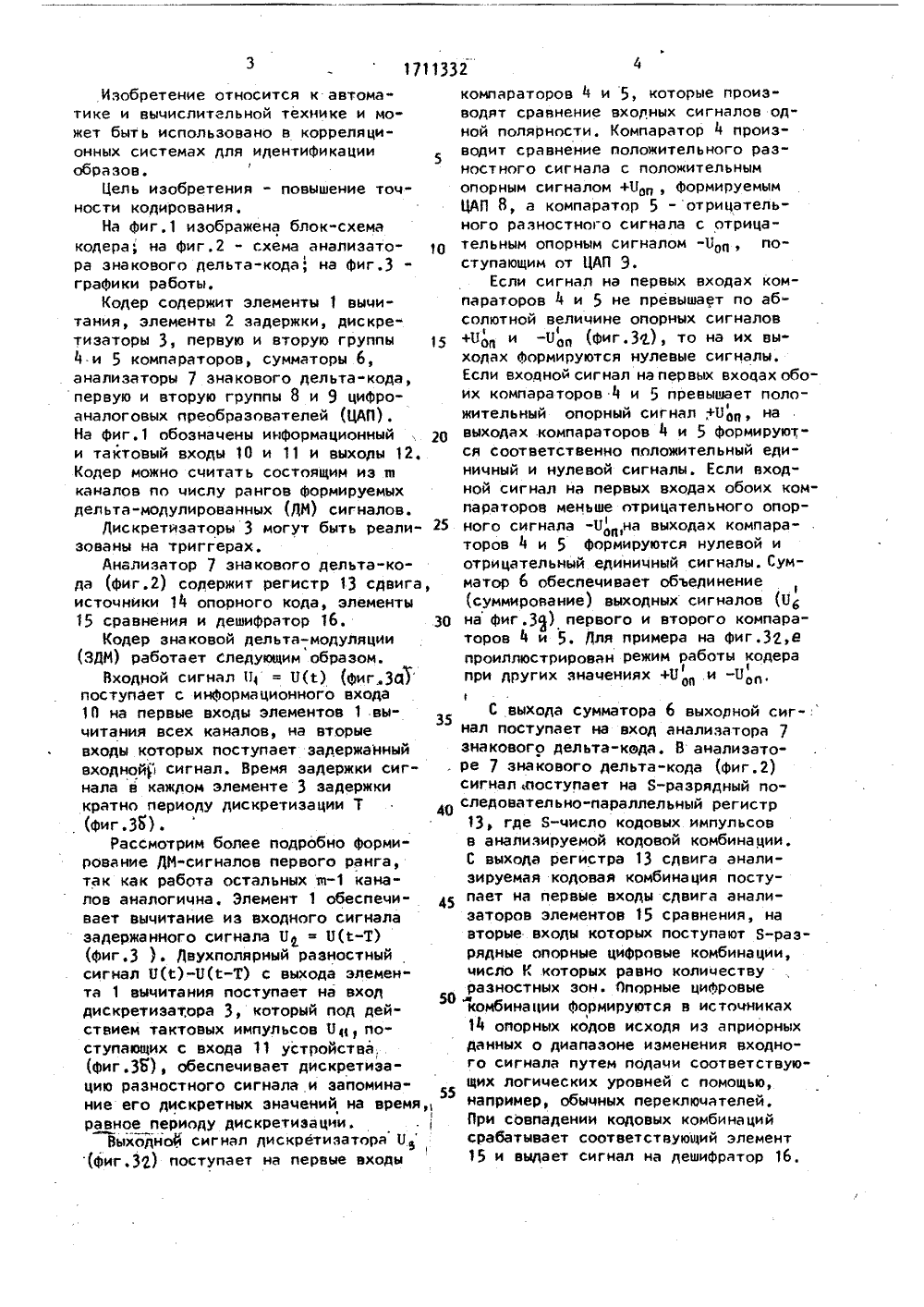

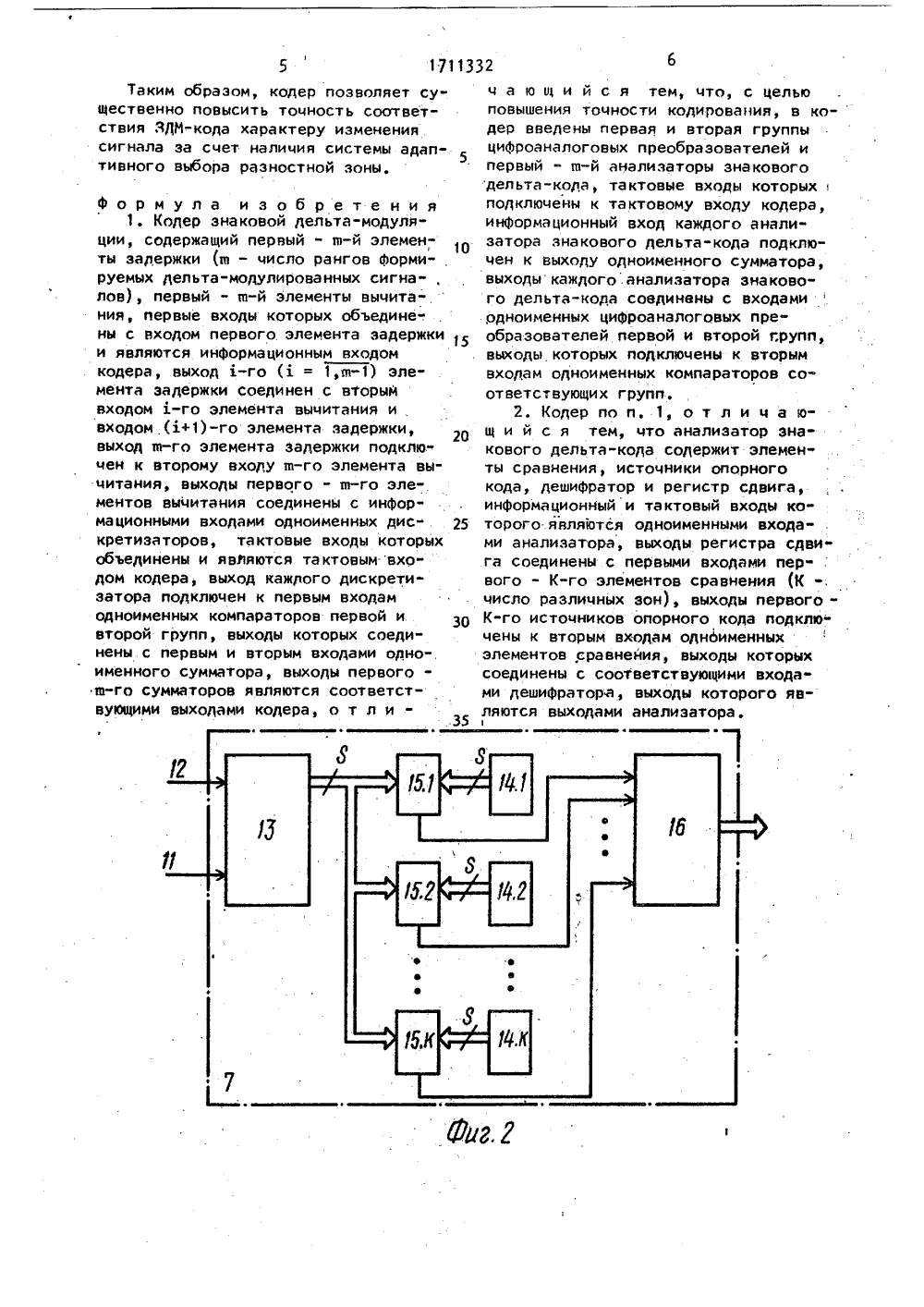

СОЮЗ СОВЕТСКИХшилапмпеРЕСПУЬЛИН 03 .М 3)00 3/ ОБРЕТИ Фиг. Р ОСУДАРСТВЕНКЫЙ КОМИТЕТГЮ ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯПРИ ПАКТ СССР ПИСАНИЕ ИЗ ВТОУСНОМУ СВИДИВЪСТ.Его использование в корреляционныхсистемах для идентификации образовпозволяет повысить точность кодирования. Кодер содержит элементывычитания, элементы 2 задержки, дискретизаторы 3, группы 4, 5 компараторов и сумматоры 6, Благодарявведению анализаторов 7 знаковогодельта-кода и групп 8; 9 цифроаналоговых преобразователей в кодереобеспечивается адаптивное изменениепорогов срабатывания компараторов4, 5. 1 з.п.ф-лы, 3 ил.171133 35 50 Изобретение относится к автоматике и вычислительной технике и может быть использовано в корреляционных системах для идентификацииобразов.Цель изобретения - повышение точности кодирования.На фиг.1 изображена блок-схемакодера; на Фиг,2 - схема анализатора знакового дельта-кода, на фиг.3 графики работы,Кодер содержит элементы 1 вычитания, элементы 2 задержки, дискре"тизаторы 3, первую и вторую группы 154 и 5 компараторов, сумматоры 6,анализаторы 7 знакового дельта-кода,первую и вторую группы 8 и 9 цифроаналоговых преобразователей (ЦАП).На фиг.1 обозначены информационный , 20и тактовый входы 10 и 11 и выхоры 12,Кодер можно считать состоящим иэ аканалов по числу рангов Формируемыхдельта-модулированных (ЬИ) сигналов.Ьискретизаторы 3 могут быть реализованы на триггерах.Анализатор 7 знакового дельта-кода (фиг.2) сорержит регистр 13 сдвига,источники 14 опорного кода, элементы15 сравнения и дешиФратор 16, 30Кодер знаковой дельта-модуляции(ЗДИ) работает следующим образом.Входной сигнал П = Б (Фиг,3 СУпоступает с информационного входа10 на первые входы элементов 1 вычитания всех каналов, на вторыевходы которых поступает зарержанныйвходной сигнал. Время задержки сигнала в каиром элементе 3 задержкикратно периоду дискретизации Т 40, (ф .За) .Рассмотрим более подробно формирование ЬИ-сигналов первого ранга,так как работа остальных яканалов аналогична. Элемент 1 обеспечивает вычитание из входного сигналазадержанного сигнала Б = 0(й-Т)(Фиг,3 ). Ьвухполярный разностныйсигнал 0(й)-0(й-Т) с выхода элемента 1 вычитания поступает на входдискретизатора 3, который под действием тактовых импульсов Бц, поступающих с входа 11 устройства,(Фиг.38), обеспечивает дискретизацию разностного сигнала и запоминание его дискретных значений на времяравное периоду дискретизации.Выходной сигнал дискретизатора 0(Фиг.32) поступает на первые входы 2компараторов 4 и 5, которые производят сравнение входных сигналов одной полярности. Компаратор 4 производит сравнение положительного разностного сигнала с положительнымопорным сигналом +УрФормируемымЦАП 8, а компаратор 5 - отрицательного разностного сигнала с отрицательным опорным сигналом -Боя, поступающим от ЦАП Э,Если сигнал на первых входах компараторов 4 и 5 не превышает по абсолютной величине опорных сигналов+ПО и -Од (фиг.3), то на их выходах Формируются нулевые сигналы,Если входной сигнал на первых вхоцах обоих компараторов 4 и 5 превышает положительный опорный сигнал +Бвв, навыходах компараторов 4 и 5 формируют,ся соответственно положительный единичный и нулевой сигналы, Если входной сигнал на первых входах обоих компараторов меньше отрицательного опорного сигнала -0,на выходах компараторов 4 и 5 формируются нулевой иотрицательный единичный сигналы. Сумматор 6 обеспечивает обьединение(суммирование) выходных сигналов (0на Фиг.3) первого и второго компараторов 4 и 5. Ьля римера на фиг.32,епроиллюстрирован режим работы кодера1при других значениях +Ц.и -Б и,С выхода сумматора 6 выхорной сиг-нал поступает на вход анализатора 7знакового дельта-кеда. В анализаторе 7 знакового дельта-кода (Фиг.2)сигнал, поступает на Я-разрядный по"следовательно-параллельный регистр13, где 8-число кодовых импульсовв анализируемой кодовой комбинации,С выхода регистра 13 сдвига анализируемая кодовая комбинация поступает на первые входы сдвига анализаторов элементов 15 сравнения, навторые входы которых поступают я-разрядные опорные цифровые комбинации,число К которых равно количествураэностных зон. Опорные цифровыекомбинации Формируются в источниках14 опорных кодов исходя из априорныхданных о диапазоне изменения входного сигнала путем подачи соответствующих логических уровней с помощью,например, обычных переключателеи,При совпадении кодовых комбинацийсрабатывает соответствующий элемент15 и выдает сигнал на дешифратор 16,Таким Образом, кодер позволяет существенно повысить точность соответствия ЯДМ-кода характеру изменения сигнала за счет наличия системы адаптивного выбора разностной зоны. формула изобретения1. Кодер знаковой дельта-модуляции, содержащий первый - щ-й элементы задержки (щ - число рангов Формируемых дельта-модулированных сигна-, лов), первый - щ-й элементы вычитания, первые входы которых объединены с входом первого элемента задержки и являются информационным входом кодЕра, выход -го (х = 1,щ) элемента задержки соединен с вторым входом -го элемента вычитания и входом (д+1)-го элемента задержки, выход щ-го элемента задержки подключен к второму входу щ-го элемента вычитания, выходы первого - щ-го элементов вычитания соединены с информационными входами одноименных дискретизаторов, тактовые входы которых объединены и являются тактовым-входом кодера, выход кажрого дискретизатора подключен к первым входам одноименных компараторов первой и второй групп, выходы которых соединены с первым и вторым входами одноименного сумматора, выходы первогощ-го сумматоров являются соответствующими выходами кодера, о т л ич а ю щ и й с я тем, что, с цельюповышения точности кодирования, в кодер введены первая и вторая группыцифроаналоговых преобразователей и5агпервыи - щ-и анализаторы знаковогодельта-кора, тактовые входы которых .подключены к тактовому Входу кодера,информационный вход каждого анализатора знакового дельта-кода подклю"чен к выходу одноименного сумматора,выходы каждого анализатора знаково"го дельта-кода соединвны с входамиодноименных цифроаналоговых преобразователей первой и второй групп,выходы которых подключены к вторымвходам одноименных компараторов соответствующих групп.2. Кодер по и. 1, о т л и ч а ющ и й с я тем, что анализатор знакового дельта-кода содержит элементы сравнения, источники опорногокода, дешифратор и регистр сдвига,информационный и тактовый входы ко 25 торого являются одноименными входа"ми анализатора, выходы регистра сдвига соединены с первыми входами пер- .вого - К-го элементов сравнения (К -,число различных зон), выходы первого 3 О К ГО источникОв Опорного кода подклюцены к вторым входам однЬименныхэлементов сравнения, выходы которыхсоединены с соответствующими входами дешифратор, выходы которого являются выходами анализатора,1Тиражкомитета по изобрет ог фл 5 д, К, Раушс Подписноениян и открытиям при КТ СССРая наб., и. 4/5

СмотретьЗаявка

4714774, 04.07.1989

ЛЬВОВСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. ЛЕНИНСКОГО КОМСОМОЛА

ПОГРИБНОЙ ВЛАДИМИР АЛЕКСАНДРОВИЧ, РОЖАНКОВСКИЙ ИГОРЬ ВЛАДИМИРОВИЧ, САВЧИН ОСТАП МИРОНОВИЧ, АТАМАНЧУК АЛЕКСАНДР НИКОЛАЕВИЧ, ПАНЧУК АЛЕКСАНДР СЕРГЕЕВИЧ, КУЛИНИЧ ТАТЬЯНА ВАСИЛЬЕВНА

МПК / Метки

Метки: дельта-модуляции, знаковой, кодер

Опубликовано: 07.02.1992

Код ссылки

<a href="https://patents.su/4-1711332-koder-znakovojj-delta-modulyacii.html" target="_blank" rel="follow" title="База патентов СССР">Кодер знаковой дельта-модуляции</a>

Предыдущий патент: Устройство кодирования и декодирования сигналов звукового вещания

Следующий патент: Устройство для формирования многофазных сигналов

Случайный патент: 158582