Устройство сопряжения интерфейсов разной разрядности

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

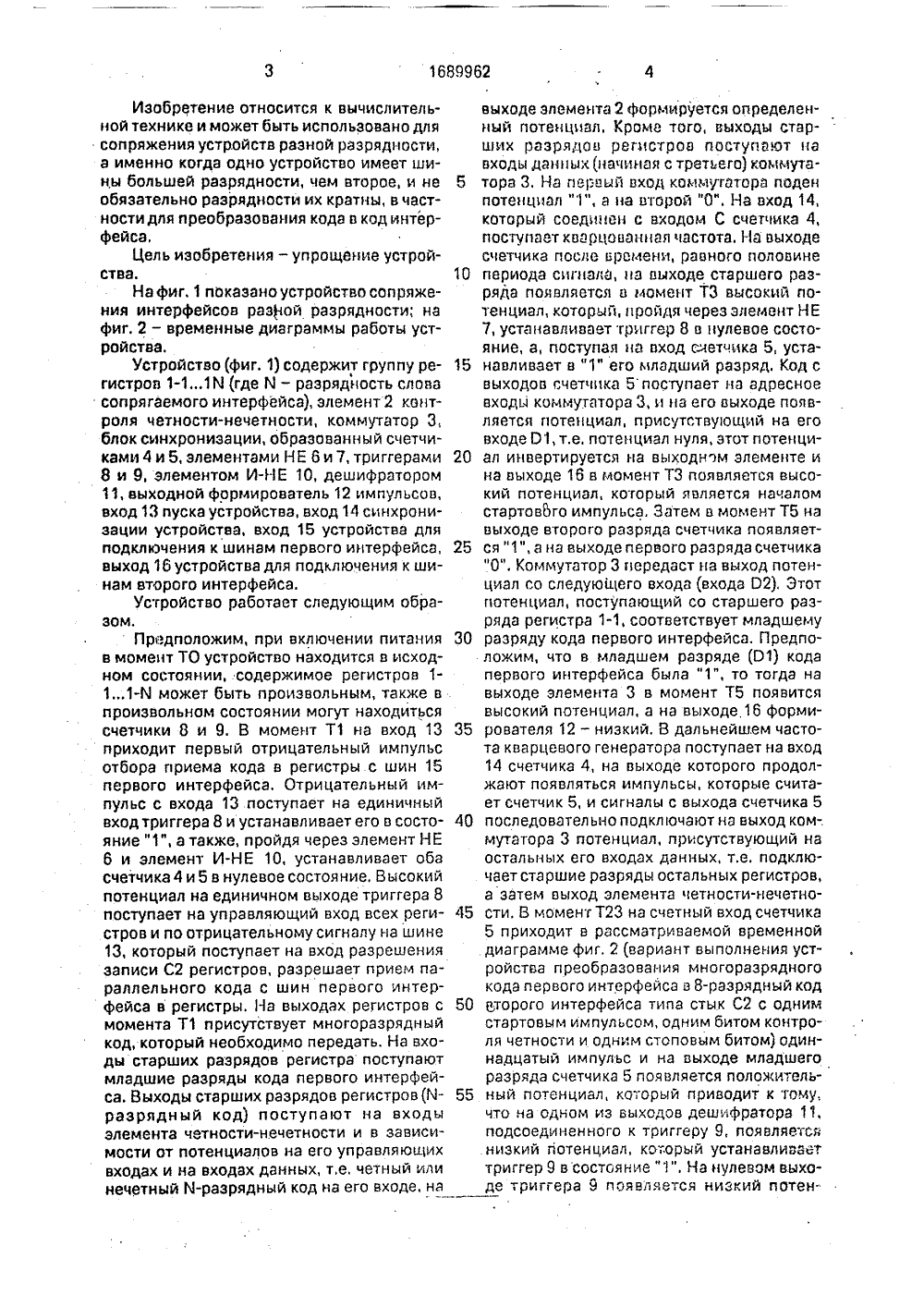

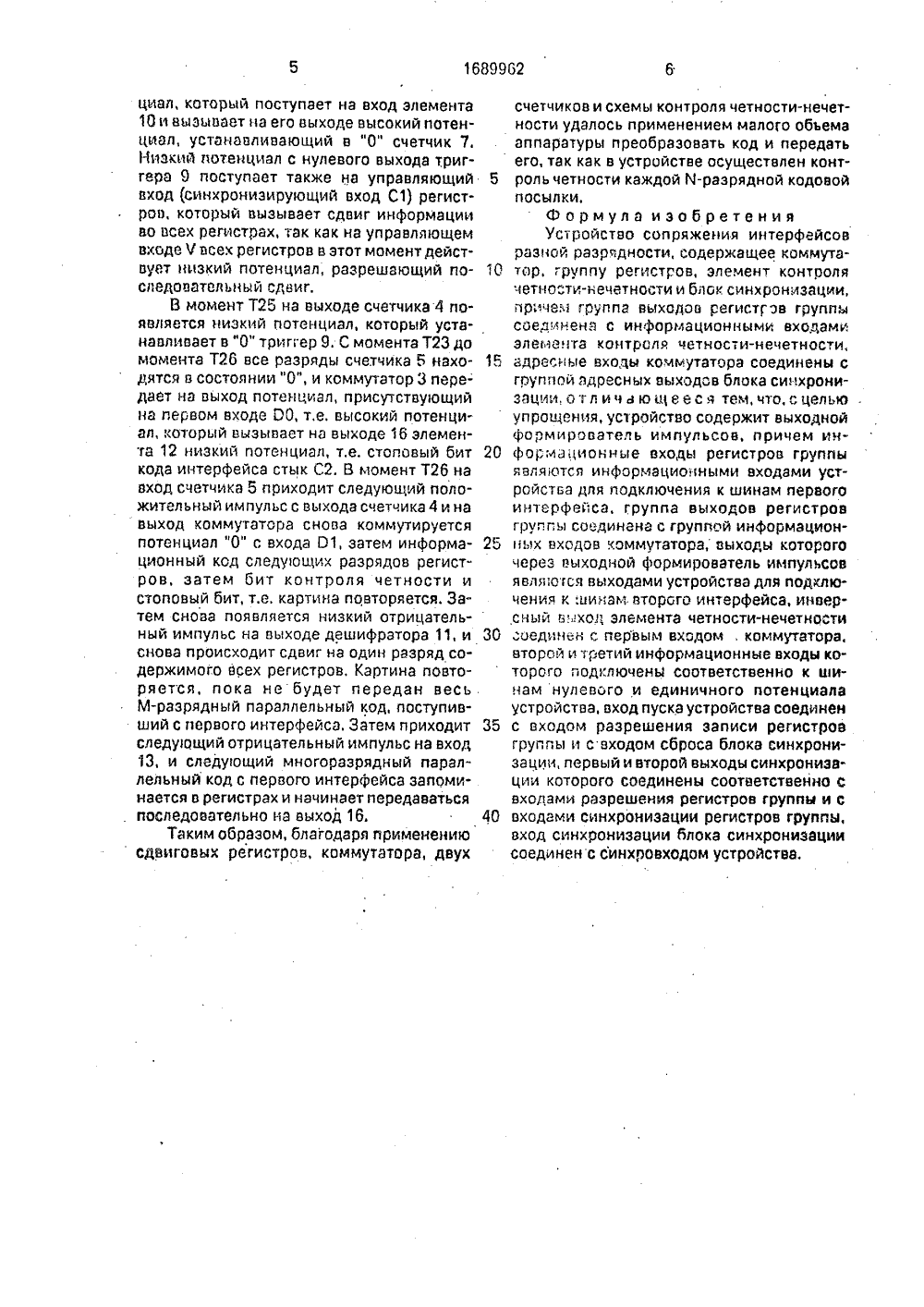

(5) ГОСУДАРСТВЕНЫИ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ОПИСАНИЕ ИЗОБРЕТЕНИК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Кра тельовано зряд- име(21) 4778399/24(56) Авторское свидетельство СССРВ 1462329, кл. 6 06 Е 13/00, 1987,Авторское свидетельство СССРЛЬ 1365088, кл. 6 06 Г 13/00, 1986.(54) УСТРОЙСТ 80 СОПРЯЖЕНИЯ ИНТЕФЕЙСОВ РАЗНОЙ РАЗРЯДНОСТИ(57) Изобретение относится к вычислиной технике и может быть использдля сопряжения устройств разной раности, а именно, когда одно устройствок ет шины большей разрядности, чем другое, и не обязательно разрядность их кратна между собой, в частности для преобразования кода в код интерфейса, Цель изобретения - упрощение устройства. Устройство содержит группу регистров 1-11 й ч - разрядность слова сопрягаемого интерфейса), элемент 2 четности/нечетности, коммутатор 3, блок синхронизации, образованный счетчиками 4, 5, элементами Н Е 6, 7, триггерами 8, 9, элементом И-НЕ 10, дешифратором 11, выходной формирователь 12 импульсов, вход 13 пуска устройства, вход 14 синхронизации устройства, вход 15 устройства для подключения к шинам первого интерфейса, выход 16 устройства для подключения к шинам второго интерфейса, 2 ил,5 10 20 25 30 40 50 Изобретение относится к вычислительной технике и может быть использовано длясопряжения устройств разной разрядности,а именно когда одно устройство имеет шины большей разрядности, чем второе, и необязательно разрядности их кратны, в частности для преобразования кода в код интерфейса,Цель изобретения - упрощение устройства.На фиг. 1 показано устройство сопряжения интерфейсов разой разрядности; нафиг. 2 - временные диаграммы работы устройства.Устройство (фиг. 1) содержит группу регистров 1-11 М (где И - разрядность словасопрягаемого интерфейса), элемент 2 контроля четности-нечетности, коммутатор 3,блок синхронизации, образованный счетчиками 4 и 5, элементами Н Е 6 и 7, триггерами8 и 9, элементом И-НЕ 10, дешифратором11, выходной формирователь 12 импульсов,вход 13 пуска устройства, вход 14 синхронизации устройства, вход 15 устройства дляподключения к шинам первого интерфейса,выход 16 устройства для подключения к шинам второго интерфейса.Устройство работает следующим образом.Предположим, при включении питанияв момент ТО устройство находится в исходном состоянии, содержимое регистров 111-й может быть произвольным, также в произвольном состоянии могут находиться счетчики и и 9. В момент Т 1 на вход 13 приходит первый отрицательный импульс отбора приема кода в регистры с шин 15 первого интерфейса, Отрицательный импульс с входа 13 поступает на единичный вход триггера 8 и устанавливает его в состояние "1", а также, пройдя через элемент НЕ 6 и элемент И-НЕ 10, устанавливает оба счетчика 4 и 5 в нулевое состояние, Высокий потенциал на единичном выходе триггера 8 поступает на управляющий вход всех регистров и по отрицательному сигналу на шине 13, который поступает на вход разрешения записи С 2 регистров, разрешает прием параллельного кода с шин первого интерфейса в регистры. На выходах регистров с момента Т 1 присутствует многоразрядный код, который необходимо передать. На входы старших разрядов регистра поступают младшие разряды кода первого интерфейса. Выходы старших разрядов регистров(К- разрядный код) поступают на входы элемента четности-нечетности и в зависимости от потенциалов на его управляющих входах и на входах данных, т.е. четный или нечетный Й-разрядный код на его входе, на выходе элемента 2 Форл 1 ируется определенный потенциал, Кроме того, выходы старших разрядов регистров поступают на входы данных начиная с третьего) коммутатора 3. На первый вход коммутатора поден потенциал "1"а на второй "0", На вход 14, который соединен с входом С счетчика 4, поступает кварцованная частота. На выходе счетчика после ьремени, равноо половине периода синана, на выходе старшего разряда появляется а момент ТЗ высокий потенциал, который, пройдя через элемент НЕ 7, устанавливает триггер 8 в нулевое состояние, а, поступал на вход счетчика 5, устанавливает в "1" его младший разряд. Код с выходов счетчика 5 поступает на адресное входы коммутатора 3, и на его выходе появляется потенциал, присутствующий на его входе 01, т.е, потенциал нуля, этот потенциал инвертируется на выходнм элементе и на выходе 16 в момент ТЗ появляется высокий потенциал, который является началом стартового импульса. Затеи в момент Т 5 на выходе второго разряда счетчика появляется "1", а на выходе первого разряда счетчика "0", Коммутатор 3 передаст на выход потенциал со следующего входа (входа 02), Этот потенциал, поступающий со старшего разряда регистра 1-1, соответствует младшему разряду кода первого интерфейса. Предположим, что в младшем разряде (01) кода первого интерфейса была "1", то тогда на выходе элемента 3 в момент Т 5 появится высокий потенциал, а на выходе 16 формирователя 12 - низкий. В дальнейшем частота кварцевого генератора поступает на вход 14 счетчика 4, на выходе которого продолжают появляться импульсы, которые считает счетчик 5, и сигналы с выхода счетчика 5 последовательно подключают на выход ком-. мутатора 3 потенциал, присутствующий на остальных его входах данных, т.е. подключает старшие разряды остальных регистров, а затем выход элемента четности-нечетности. В момент Т 23 на счетный вход счетчика 5 приходит в рассматриваемой временной диаграмме фиг. 2 (вариант выполнения устройства преобразования многоразрядного кода первого интерфейса в 8-разрядный код Рторого интерфейса типа стык С 2 с одним стартовым импульсом, одним битом контроля четности и одним стоповым битом) одиннадцатый импульс и на выходе младшего разряда счетчика Б появляется положительный потенциал, который приводит к тому., что на одном из выходов дешифратора 11, подсоединенного к триггеру 9, появляегся низкий потенциал, который устанавливает триггер 9 в состояние "1", На нулевом выходе триггера 9 появляется низкий потен 1689962циал, который поступает на вход элемента 10 и вызывает на его выходе высокий потенциал, устанавливающий в "0" счетчик 7. Низкий потенциал с нулевого выхода триггера 9 поступает также на управляющий 5 вход (синхрониэирующий вход С 1) регистров, который вызывает сдвиг информации во Всех регистрах, так как на управляющем входе Ч Всех регистров в этот момент действует низкий потенциал, разрешающий по следовательный сдвиг.В момент Т 25 на выходе счетчика 4 появляется низкий потенциал, который устанавливает в "0" триггер 9. С момента Т 23 до момента Т 26 все разряды счетчика 5 нахо дятся в состоянии "О", и коммутатор 3 передает на выход потенциал, присутствующий на первом входе 00, т.е. высокий потенциал, который вызывает на выходе 16 элемента 12 низкий потенциал, т.е. стоповый бит 20 кода интерфейса стык С 2. В момент Т 26 на вход счетчика 5 приходит следующий положительный импульс с выхода счетчика 4 и на ВыхОд коммутатора снова коммутируется потенциал "О" с входа О 1, затем информа ционный код следующих разрядов регистров, затем бит контроля четности и стоповый бит, т.е. картина повторяется. Затем снова появляется низкий отрицательный импульс на выходе дешифратора 11, и 30 снова происходит сдвиг на один разряд содержимого всех регистров, Картина повторяется, пока не будет передан весь М-разрядный параллельный код, поступивший с первого интерфейса, Затем приходит 35 следующий отрицательный импульс на вход 13, и следующий многоразрядный параллельный код с первого интерфейса запоминается в регистрах и начинает передаваться последовательно на выход 16. 40Таким образом, благодаря применению сдвиговых регистров, коммутатора, двух счетчиков и схемы контроля четности-нечет- ности удалось применением малого объема аппаратуры преобразовать код и передать его, так как в устройстве осуществлен контроль четности каждой Гч-разрядной кодовой посылки,Ф о рмул а и зоб рете ни я Устройство сопряжения интерфейсов разной разрядности, содержащее коммутатор, группу регистров, элемент контроля четности-нечетности и блок синхронизации, причем группа выходов регистгэв группы соединена с информационными входами элема,та контроля четности-нечетности,. адресные входы коммутатора соединены с гоуппой адресных выходов блока синхронизации,отличающееся тем,что,сцелью уп рощения, ус 1 ройство содержит выходной формирователь импульсов, причем информаионные входы регистров группы являются информационными входами устройства для подключения к шинам первого интерфейса, группа выходов регистров группы соединена с группой информационных входов коммутатора, выходы которого через выходной формирователь импульсов явля Отея выходами устройства для подключения к шинам второго интерфейса, инверсный выход элемента четности-нечеткости "оединвн с первым входом . коммутатора, второй и третий информационные входы которого подключены соответственно к шинам нулевого и единичного потенциала устройства, вход пуска устройства соединен с входом разрешения записи регистров группы и с входом сброса блока синхронизации, первый и второй выходы синхронизации которого соединены соответственно с входами разрешения регистров группы и с входами синхронизации регистров группы, вход снронизации блока сронизации соединен с синхровходом устройства.1689962Составитель А.Сиротская Редактор С.Патрушева Техред М,Моргентал Корректор С.Ч каз 3815 Тираж Подписное. ВНИИПИ Государственного комитета по изобретениям и открцтиям при ГКНТ СС113035, Москва, Ж, Раушская наб., 4/5роизводственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарин

СмотретьЗаявка

4778399, 17.10.1989

НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ "КВАНТ"

ФОЙДА АЛЬБЕРТ НИКИТОВИЧ, РАДЧЕНКО ОКТЯБРИНА АНТОНОВНА, КРАВЧЕНКО ЛЮДМИЛА ИВАНОВНА

МПК / Метки

МПК: G06F 13/00, G06F 5/00

Метки: интерфейсов, разной, разрядности, сопряжения

Опубликовано: 07.11.1991

Код ссылки

<a href="https://patents.su/4-1689962-ustrojjstvo-sopryazheniya-interfejjsov-raznojj-razryadnosti.html" target="_blank" rel="follow" title="База патентов СССР">Устройство сопряжения интерфейсов разной разрядности</a>

Предыдущий патент: Устройство для обмена информацией между цвм и внешними устройствами

Следующий патент: Устройство связи кольцевой оптоволоконной сети

Случайный патент: Дроссельная литниковая система