Преобразователь последовательного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

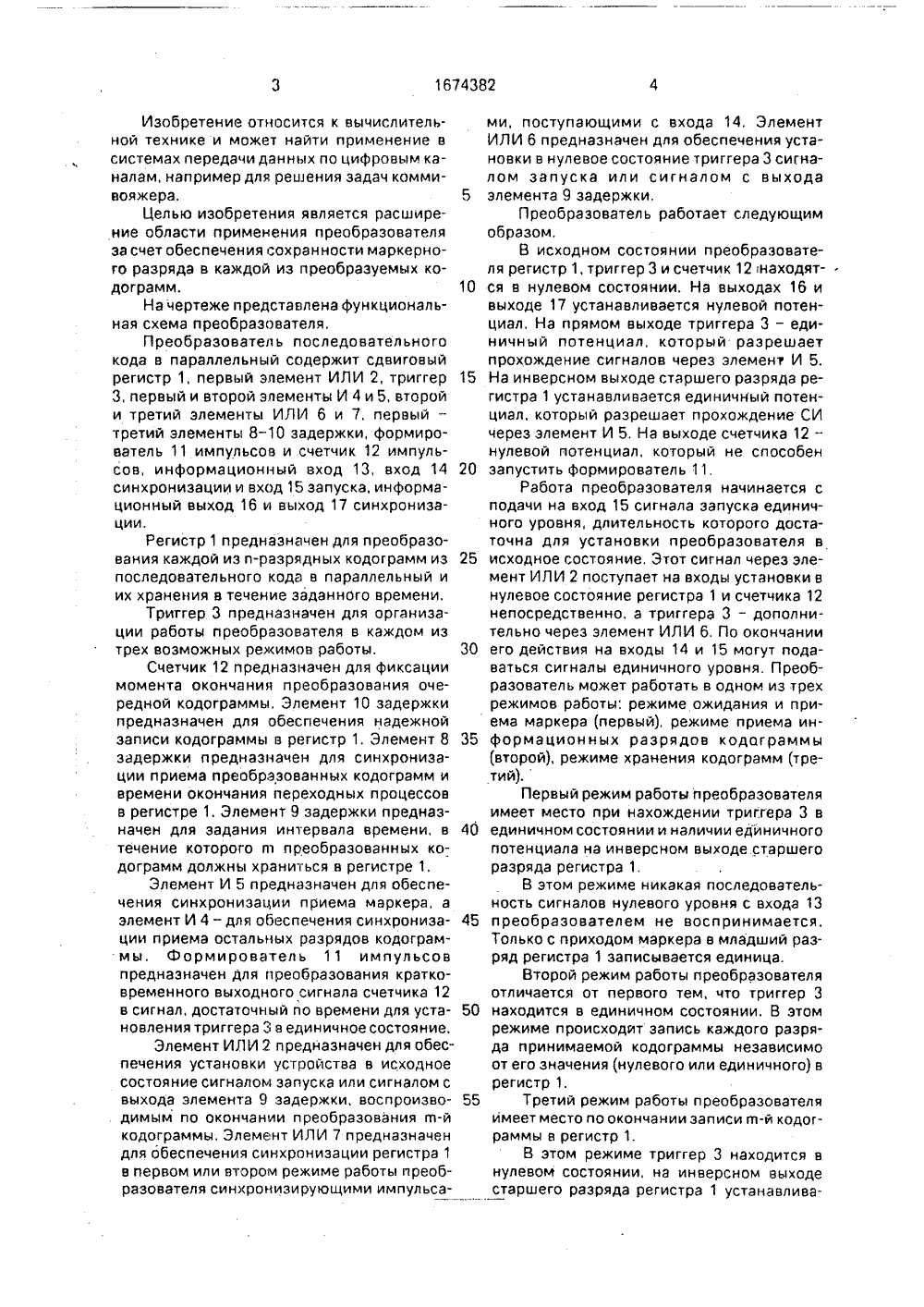

)5 АНИЕ ИЗОБРЕТЕНИ 17 ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(56) Авторское свидетельство СССР 1 Ф 1081639, кл. Н 03 М 9/00, 1984.Авторское свидетельство СССР М 851396, кл, Н 03 М 9/00, 1981. (54) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ (57) Изобретение относится к вычислительной технике и может найти применение в редачи данных по цифровым каимер для решения задач коммиобретение позволяет сохранять кодограммы, в том числе и маряд, за счет чего обеспечивается области применения преобраеобразователь последователь- в параллельный содержит егистр 1, элементы ИЛИ 2, б и 7, ементы И 4 и 5, элементы 8 - 10 ормирователь 11 импульсов и мпульсов, 1 ил. системах пе налам,напр вояжера. Из все разряды керный разр расширение зователя. Пр ного кода сдвиговый р триггер 3, эл задержки, ф счетчик 12 иИзобретение относится к вычислительной технике и может найти применение всистемах передачи данных по цифровым, каналам, например для решения задач коммивояжера. 5Целью изобретения является расширение области применения преобразователяза счет обеспечения сохранности маркерного разряда в каждой из преобразуемых кодограмм, 10На чертеже представлена функциональная схема преобразователя,Преобразователь последовательногокода в параллельный содержит сдвиговыйрегистр 1, первый элемент ИЛИ 2, триггер 153, первый и второй элементы И 4 и 5, второйи третий элементы ИЛИ 6 и 7, первый -третий элементы 8-10 задержки, формирователь 11 импульсов и счетчик 12 импульсов, информационный вход 13, вход 14 20синхронизации и вход 15 запуска, информационный выход 16 и выход 17 синхронизации,Регистр 1 предназначен для преобразования каждой из и-разрядных кодограмм из 25последовательного кода в параллельный иих хранения в течение заданного времени,Триггер 3 предназначен для организации работы преобразователя в каждом изтрех возможных режимов работы. 30Счетчик 12 предназначен для фиксациимомента окончания преобразования очередной кодограммы. Элемент 10 задержкипредназначен для обеспечения надежнойзаписи кодограммы в регистр 1. Элемент 8 35задержки предназначен для синхронизации приема преобразованных кодограмм ивремени окончания переходных процессовв регистре 1. Элемент 9 задержки предназначен для задания интервала времени, в 40течение которого гп преобразованных кодограмм должны храниться в регистре 1,Элемент И 5 предназначен для обеспечения синхронизации приема маркера, аэлемент И 4 - для обеспечения синхронизации приема остальных разрядов кодограммы, Формирователь 11 импульсовпредназначен для преобразования кратковременного выходного сигнала счетчика 12в сигнал, достаточный по времени для установления триггера 3 в единичное состояние.Элемент ИЛИ 2 предназначен для обеспечения установки устройства в исходноесостояние сигналом запуска или сигналом свыхода элемента 9 задержки, воспроизводимым по окончании преобразования а-йкодограммы. Элемент ИЛИ 7 предназначендля обеспечения синхронизации регистра 1в первом или втором режиме работы преобразователя синхронизи рующими импул ьсами, поступающими с входа 14, ЭлементИЛИ 6 предназначен для обеспечения установки в нулевое состояние триггера 3 сигналом запуска или сигналом с выходаэлемента 9 задержки,Преобразователь работает следующимобразом,В исходном состоянии преобразователя регистр 1, триггер 3 и счетчик 12 находятся в нулевом состоянии. На выходах 16 ивыходе 17 устанавливается нулевой потенциал, На прямом выходе триггера 3 - единичный потенциал, который разрешаетпрохождение сигналов через элемент И 5,На инверсном выходе старшего разряда регистра 1 устанавливается единичный потенциал, который разрешает прохождение СИчерез элемент И 5, На выходе счетчика 12 -нулевой потенциал. который не способензапустить формирователь 11.Работа преобразователя начинается сподачи на вход 15 сигнала запуска единичного уровня, длительность которого достаточна для установки преобразователя висходное состояние, Этот сигнал через элемент ИЛИ 2 поступает на входы установки внулевое состояние регистра 1 и счетчика 12непосредственно, а триггера 3 - дополнительно через элемент ИЛИ 6. По окончанииего действия на входы 14 и 15 могут подаваться сигналы единичного уровня. Преобразователь может работать в одном из трехрежимов работы: режиме ожидания и приема маркера (первый), режиме приема информационных разрядов кодаграммы(второй), режиме хранения кодограмм (третий),Первый режим работы преобразователяимеет место при нахождении триггера 3 вединичном состоянии и наличии единичногопотенциала на инверсном выходе старшегоразряда регистра 1,В этом режиме никакая последовательность сигналов нулевого уровня с входа 13преобразователем не воспринимается.Только с приходом маркера в младший разряд регистра 1 записывается единица.Второй режим работы преобразователяотличается от первого тем, что триггер 3находится в единичном состоянии. В этомрежиме происходит запись каждого разряда принимаемой кодограммы независимоот его значения (нулевого или единичного) врегистр 1.Третий режим работы преобразователяимеет место по окончании записи а-й кодограммы в регистр 1.В этом режиме триггер 3 находится внулевом состоянии, на инверсном выходестаршего разряда регистра 1 устанавлива 16743825 10 15 20 25 30 35 40 45 50 ется нулевой потенциал, чем запрещается прохождение СИ на вход синхронизации регистра 1. На выходе 17 нулевой потенциал изменяется на единичный, т.е. вырабатывается динамический сигнал синхронизации приема преобразованных кодограмм и выходов 16 внешней нагрузкой.До появления на входе 13 очередной (в том числе в первой) из т преобразуемых и-разрядных кодограмм, каждая из которых начинается с маркера, преобразователь находится в первом режиме работы,В этом случае с приходом маркера очередной кодограммы (в том числе и первой) сигнал единичного уровня с входа 13 через элемент И 5, подготовленный к срабатыванию единичными потенциалами, поступающими с инверсного выхода триггера 3 и инверсного выхода старшего разряда регистра 1, одновременно с приходом очередного СИ с входа 14 поступает через элемент ИЛИ 7 на вход синхронизации регистра 1, Кроме того, сигнал с входа 13 с задержкой, равной длительности срабатывания элементов И 5 и ИЛИ 7, поступает через элемент 10 задержки на информационный вход регистра 1. Происходит запись единицы в младший разряд регистра 1, т.е, прием маркерного разряда кодограммы, Кроме того, с выхода элемента И 5 сигнал единичного уровня поступает на единичный вход триггера 3, Последний переходит в единичноесостояние, а преобразователь в целом в . вовторой режим работы. Теперь уже единичный поТенциал с.прямого выхода триггера 3 разрешает прохождение СИ с входа 14 через элемент И 4, а нулевой потенциал с инверсного выхода этого триггера запрещает прохождение сигмалов с входа 13 через элемент И 5, Приход каждого СИ с входа 14 сопровождается. сдвигом влево содержимого регистра 1 на один разряд и записью в младший разряд значения очередного разряда (единичного или нулевого) принимаемой на входе 13 ко-. дограммы,Для обеспечения надежной работы устройства необходимо, чтобы передний фронт каждого СИ на входе 14 приходился на середину длительности сигналов на входе 13, воспроизводящих единичные значения разрядов кодограммы, Число сдвигов в регистре 1 подсчитывается счетчиком 12, на информационный вход которого поступают СИ с выхода элемента И 4, управляющие сдвигом И во втором режиме работы преобразователя, После поступления (2 п - 1)-го СИ на информационный вход счетчика 12 он вырабатывает сигнал единичного уровня, устанавливающий через формирователь 11 и элемент ИЛИ 6 в нулевое состояние триггер 3, Преобразователь переводится в первый режим работы, счетчик 12 устанавливается в нулевое состояние, а,в первых п разрядах регистра 1 размещается первая принятая кодограмма. Последующие кодограммы с второй по щ-ю принимаются аналогично, а прием происходит лишь по поступлении маркера, По окончании приема гп-й кодограммы на прямом выходе старшего разряда регистра 1 устанавливается потенциал единичного уровня, который через элемент 8 задержки через промежуток времени, достаточный для окончания переходных процессов в регистр 1 после проведения очередного сдвига, поступает на выход 17, чем синхронизирует момент приема п 1 преобразованных кодограмм с выходов 16, соединенных с одноименными прямыми выходами разрядов регистра 1, внешней нагрузкой.На инверсном выходе регистра 1 устанавливается нулевой потенциал, который запрещает поступление СИ через элемент И 5 в течение заданного времени хранения преобразованных кодограмм. При этом преобразователь находится в третьем режиме работы.Длительность хранения а преобразованных кодограмм в регистре 1 ограничена снизу временем, достаточным для приема внешней нагрузкой сигналов с выходов 16, а сверху временем, не превышающим минимального интервала времени между соседними кодограммами,Эта длительность задается элементом 9 задержки, выходной сигнал которого через элемент ИЛИ 2 поступает на входы установки в нулевое состояние регистра 1 и счетчика 12 непосредственно. а триггера 3 - дополнительно через элемент ИЛИ 6,Таким образом, по окончании преобразования и истечении заданного времени хранения е кодограмм устройство самостоятельно переводится в исходное состояние и оказывается готовым к осуществлению очередного цикла преобразования,Формула изобретения Преобразователь последовательного кода в параллельный, содержащий сдвиговый регистр, первый элемент ИЛИ, триггер, прямой выход которого соединен с первым входом первого элемента И, инверсный выход триггера соединен с первым входом второго элемента И, второй вход которого объединен с вторым входом первого элемента И и является входом синхронизации преобразователя, третий вход второго эле1674382 Составитель Б,ХодовТехред М,Моргентал Редактор Н,Шитев Корректор С.Черни Заказ 2935 Тираж 436 Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб 4/5 Производственно-издательский комбинат "Патент", г. Ужгород. ул Гагарина, 101 мента И является информационным входом преобразователя, прямые выходы разрядов сдвигового регистра являются информационным выходом преобразователя, о т л и ч а ющ и й с я тем, что, с целью расширения области применения преобразователя за счет обеспечения сохранности маркерного разряда в каждой из преобразуемых кодограмм, в преобразователь введены второй и третий элементы ИЛИ, элементы задержки, формирователь импульсов и счетчик импульсов, выход которого через формирователь имцульсов соединен с первым входом второго элемента ИЛИ, выход которого соединен с первым входом триггера, выход первого элемента И соединен с информационным входом счетчика импульсов и с первым входом третьего элемента ИЛИ, выход которого соединен с входом синхронизации сдвигового регистра, инверсный выход старшего разряда которого совдинен с четвертым входом второго элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ и с вторым входом триггера.5 входы первого и второго элементов задержкиобъединены и подключены к прямому выходу старшего разряда сдвигового регистра, выход первого элемента задержки является выходом синхронизации преобразователя, выход 10 второго элемента задержки соединен с первым входом первого элемента ИЛИ, выход которого соединен с установочными входами счетчика импульсов и сдвигового регистра и с вторым входом второго элемента ИЛИ, выход 15 третьего элемента задержки соединен с информационным входом сдвигового регистра, вход третьего элемента задержки объединен с третьим входом второго элемента И, второй вход первого элемента ИЛИ является вхо дом запуска преобразователя,

СмотретьЗаявка

4471234, 08.08.1988

ВОЕННЫЙ ИНЖЕНЕРНЫЙ КРАСНОЗНАМЕННЫЙ ИНСТИТУТ ИМ. А. Ф. МОЖАЙСКОГО

БЕЛИКОВ ЮРИЙ ВИКТОРОВИЧ, ЖИГОРА ПАВЕЛ ПЕТРОВИЧ

МПК / Метки

МПК: H03M 9/00

Метки: кода, параллельный, последовательного

Опубликовано: 30.08.1991

Код ссылки

<a href="https://patents.su/4-1674382-preobrazovatel-posledovatelnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода в параллельный</a>

Предыдущий патент: Преобразователь кода

Следующий патент: Устройство для преобразования напряжения в код

Случайный патент: Композиция для получения водной дисперсии бутилкаучука