Параллельно-последовательный аналого-цифровой преобразователль

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

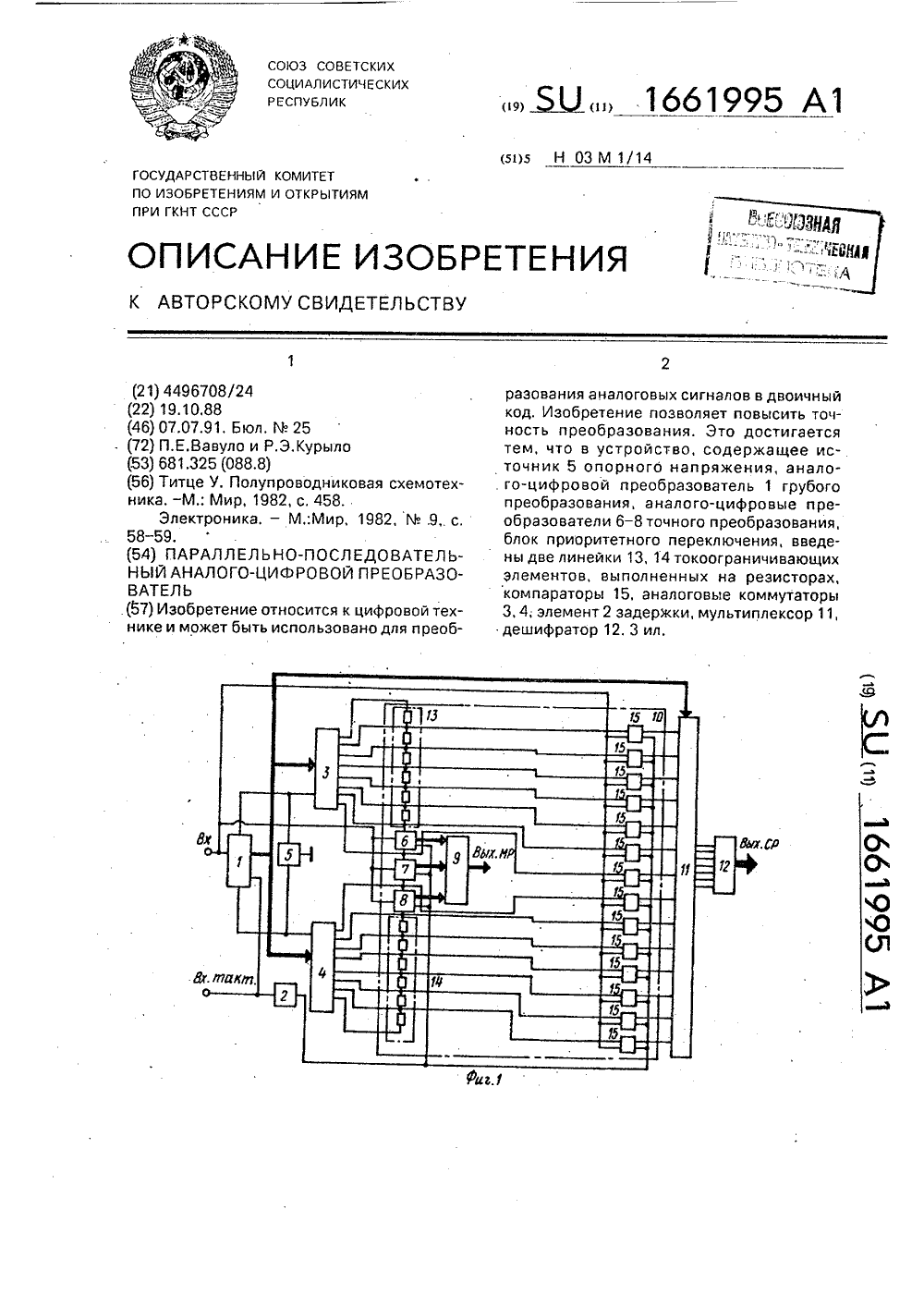

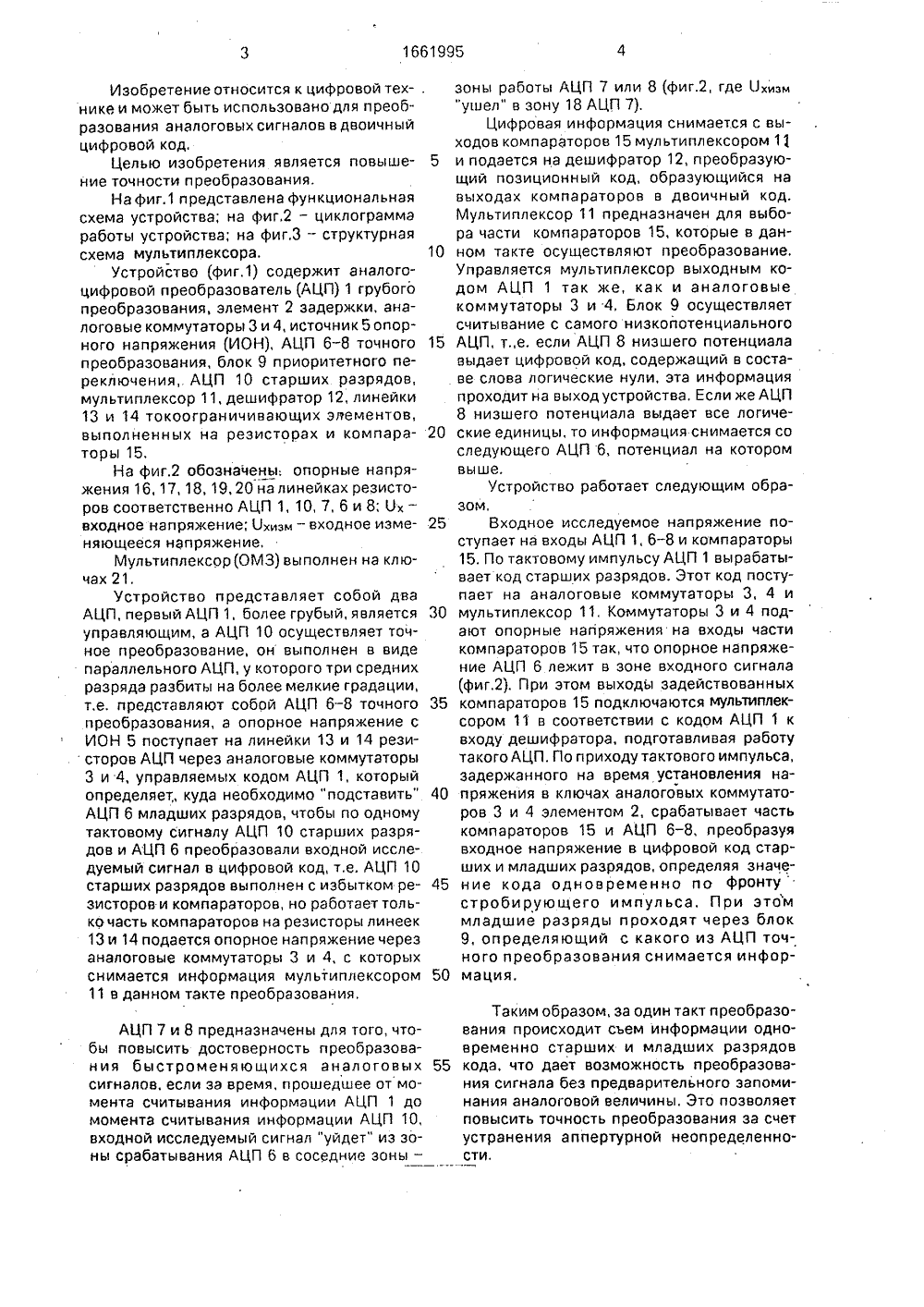

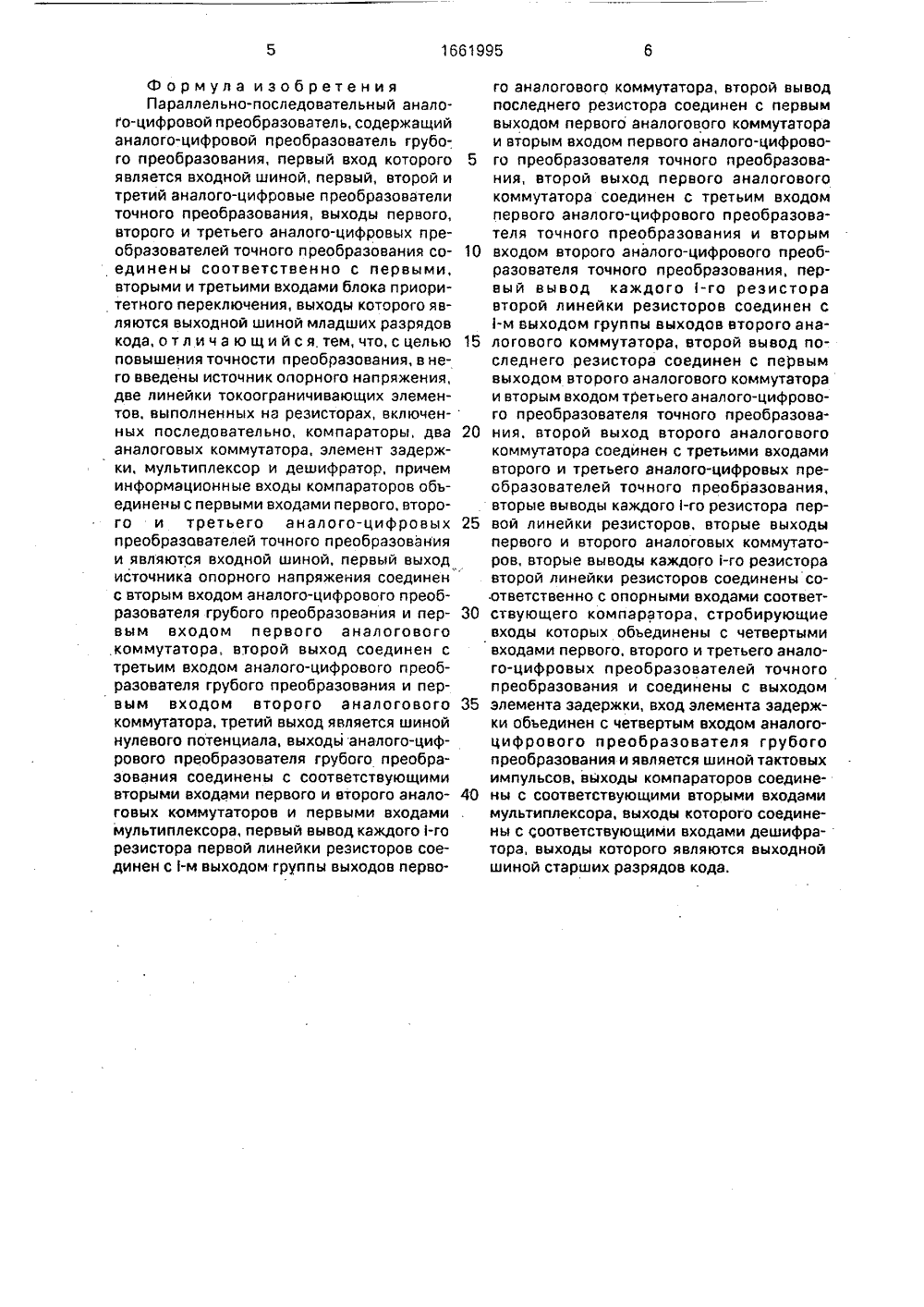

-ПОСЛЕДОВАТЕЛЬРОВОЙ ПРЕОБРАЗОосится к цифровой тех пользовано для преоб ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИПРИ ГКНТ СССР. (57) Изобретение онике и может быть роводниковая схемотех 2, с. 458.- М.:Мир, 1982, М .9 с. разования аналоговых сигналов в двоичныи код, Изобретение позволяет повысить точность преобразования. Это достигается тем, что в устройство, содержащее источник 5 опорного напряжения, аналого-цифровой преобразователь 1 грубого преобразования, аналого-цифровые преобразователи 6-8 точного преобразования, блок приоритетного переключения, введены две линейки 13, 14 токоограничивающих элементов, выполненных на резисторах, компараторы 15, аналоговые коммутаторы 3, 4, элемент 2 задержки, мультиплексор 11, дешифратор 12. 3 ил,Изобретение относится к цифровой тех- .нике и может быть использовано для преобразования аналоговых сигналов в двоичныйцифровой код,Целью изобретения является повышение точности преобразования.На фиг.1 представлена функциональнаясхема устройства; на фиг,2 - циклограммаработы устройства; на фиг.3 - структурнаясхема мультиплексора. 10Устройство (фиг,1) содержит аналогоцифровой преобразователь (АЦП) 1 грубогопреобразования, элемент 2 задержки. аналоговь 1 е коммутаторы 3 и 4, источник 5 опорного напряжения (ИОН), АЦП 6-8 точного 15преобразования, блок 9 приоритетного переключения, АЦП 10 старших разрядов,мультиплексор 11, дешифратор 12, линейки13 и 14 токоограничивающих элементов,выполненных на резисторах и компараторы 15,На фиг.2 обозначены; опорные напряжения 16, 17, 18, 19, 20 на линейках резисторов соответственно АЦП 1, 10, 7, 6 и 8; Ох -входное напряжение; Охиэм - входное изменяющееся напряжение,Мультиплексор(ОМЗ) выполнен на ключах 21.Устройство представляет собой дваАЦП, первый АЦП 1, более грубый, является 30управляющим, а АЦП 10 осуществляет точное преобразование, он выполнен в видепараллельного АЦП, у которого три среднихразряда разбиты на более мелкие градации,т.е, представляют собой АЦП 6 - 8 точного 35преобразования, а опорное напряжение сИОН 5 поступает на линейки 13 и 14 резисторов АЦП через аналоговые коммутаторы3 и 4, управляемых кодом АЦП 1, которыйопределяеткуда необходимо "подставить" 40АЦП 6 младших разрядов, чтобы по одномутактовому сигналу АЦП 10 старших разрядов и АЦП 6 преобразовали входной исследуемый сигнал в цифровой код, т,е. АЦП 10старших разрядов выполнен с избытком резисторов и компараторов, но работает только часть компараторов на резисторы линеек13 и 14 подается опорное напряжение черезаналоговые коммутаторы 3 и 4, с которыхснимается информация мультиплексором 5011 в данном такте преобразования. АЦП 7 и 8 предназначены для того, чтобы повысить достоверность преобразования быстроменяющихся аналоговых 55 сигналов, если зэ время, прошедшее от момента считывания информации АЦП 1 до момента считывания информации АЦП 10, входной исследуемый сигнал "уйдет" из зоны срабатывания АЦП 6 в соседние заныв зоны работы АЦП 7 или 8 (фиг.2, где Охизм "ушел" в зону 18 АЦП 7),Цифровая информация снимается с выходов компараторов 15 мультиплексором 13 и подается на дешифратор 12, преобразующий позиционный код, образующийся на выходах компараторов в двоичный код, Мультиплексор 11 предназначен для выбора части компараторов 15, которые в данном такте осуществляют преобразование. Управляется мультиплексор выходным кодом АЦП 1 так же, как и аналоговые коммутаторы 3 и 4, Блок 9 осуществляет считывание с самого низкопотенциального АЦП, т.,е. если АЦП 8 низшего потенциала выдает цифровой код, содержащий в составе слова логические нули, зта информация проходит на выход устройства, Если же АЦП 8 низшего потенциала выдает все логические единицы, то информация снимается со следующего АЦП 6, потенциал на котором выше,Устройство работает следующим образом,Входное исследуемое напряжение поступает на входы АЦП 1, 6 - 8 и компараторы 15, По тактовому импульсу АЦП 1 вырабатывает код старших разрядов, Этот код поступает на аналоговые коммутаторы 3, 4 и мультиплексор 11, Коммутаторы 3 и 4 подают опорные напряжения на входы части компараторов 15 так, что опорное напряжение АЦП 6 лежит в зоне входного сигнала (фиг,2). При этом выходы задействованных компараторов 15 подключаются мультиплексором 11 в соответствии с кодом АЦП 1 к входу дешифратора, подготавливая работу такого АЦП. По приходу тактового импульса, задержанного на время установления напряжения в ключах аналоговых коммутаторов 3 и 4 элементом 2, срабатывает часть компараторов 15 и АЦП 6 - 8, преобразуя входное напряжение в цифровой код старших и младших разрядов, определяя значение кода одновременно по фронту стробирующего импульса. При зтом младшие разряды проходят через блок 9, определяющий с какого из АЦП точного преобразования снимается информация. Таким образом, за один такт преобразования происходит съем информации одновременно старших и младших разрядов кода. что дает возможность преобразования сигнала без предварительного запоминания аналоговой величины, Это позволяет повысить точность преобразования за счет устранения аппертурной неопределенности, 16619955 10 15 25 30 35 40 Формула изобретения Параллельно-последовательный аналого-цифровой преобразователь, содержащий аналого-цифровой преобразователь грубого преобразования, первый вход которого является входной шиной, первый, второй и третий аналого-цифровые преобразователи точного преобразования, выходы первого, второго и третьего аналого-цифровых преобразователей точного преобразования соединены соответственно с первыми, вторыми и третьими входами блока приоритетного переключения, выходы которого являются выходной шиной младших разрядов кода, отличающийся тем,что,сцелью повышения точности преобразования, в него введены источник опорного напряжения, две линейки токоограничивающих элементов, выполненных на резисторах, включенных последовательно, компараторы, два аналоговых коммутатора, элемент задержки, мультиплексор и дешифратор, причем информационные входы компараторов объединены с первыми входами первого, второго и третьего аналого-цифровых преобразователей точного преобразования и являются входной шиной, первый выход источника опорного напряжения соединен с вторым входом аналого-цифрового преобразователя грубого преобразования и первым входом первого аналогового .коммутатора, второй выход соединен с третьим входом аналого-цифрового преобразователя грубого преобразования и первым входом второго аналогового коммутатора, третий выход является шиной нулевого потенциала, выходы аналого-цифрового преобразователя грубого преобразования соединены с соответствующими вторыми входами первого и второго аналоговых коммутаторов и первыми входами мультиплексора, первый вывод каждого 1-го резистора первой линейки резисторов соединен с 1-м выходом группы выходов первого аналогового коммутатора, второй вывод последнего резистора соединен с первым выходом первого аналогового коммутатора и вторым входом первого аналого-цифрового преобразователя точного преобразования, второй выход первого аналогового коммутатора соединен с третьим входом первого аналого-цифрового преобразователя точного преобразования и вторым входом второго аналого-цифрового преобразователя точного преобразования, первый вывод каждого 1-го резистора второй линейки резисторов соединен с 1-м выходом группы выходов второго аналогового коммутатора, второй вывод последнего резистора соединен с первым выходом второго аналогового коммутатора и вторым входом третьего аналого-цифрового преобразователя точного преобразования, второй выход второго аналогового коммутатора соединен с третьими входами второго и третьего аналого-цифровых преобразователей точного преобразования, вторые выводы каждого 1-го резистора первой линейки резисторов, вторые выходы первого и второго аналоговых коммутаторов, вторые выводы каждого 1-го резистора второй линейки резисторов соединены со.ответственно с опорными входами соответствующего компаратора, стробирующие входы которых объединены с четвертыми входами первого, второго и третьего аналого-цифровых преобразователей точного преобразования и соединены с выходом элемента задержки, вход элемента задержки обаединен с четвертым входом аналогоцифрового преобразователя грубого преобразования и является шиной тактовых импульсов, выходы компараторов соединены с соответствующими вторыми входами мультиплексора, выходы которого соединены с Чоответствующими входами дешифратора, выходы которого являются выходной шиной старших разрядов кода.1661995 Фиг едактор Н.Рогулич Коррек Лончакова оизводственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 1 акаэ 2136 ВНИИПИ Г оставитель А,Тито ехред М,МоргентаЖТираж ф Подписноевенного комитета по изобретениям и открытиям при ГКНТ СС113035, Москва, Ж, Раушская наб 4/5

СмотретьЗаявка

4496708, 19.10.1988

ПРЕДПРИЯТИЕ ПЯ В-2634

ВАВУЛОВ ПЕТР ЕВГЕНЬЕВИЧ, КУРЫЛО РИШАРД ЭДУАРДОВИЧ

МПК / Метки

МПК: H03M 1/14

Метки: аналого-цифровой, параллельно-последовательный, преобразователль

Опубликовано: 07.07.1991

Код ссылки

<a href="https://patents.su/4-1661995-parallelno-posledovatelnyjj-analogo-cifrovojj-preobrazovatell.html" target="_blank" rel="follow" title="База патентов СССР">Параллельно-последовательный аналого-цифровой преобразователль</a>

Предыдущий патент: Синхронный десятичный счетчик

Следующий патент: Фотоэлектрический преобразователь перемещения в код

Случайный патент: Устройство для дозированной подачи паров