Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1580361

Автор: Криворучко

Текст

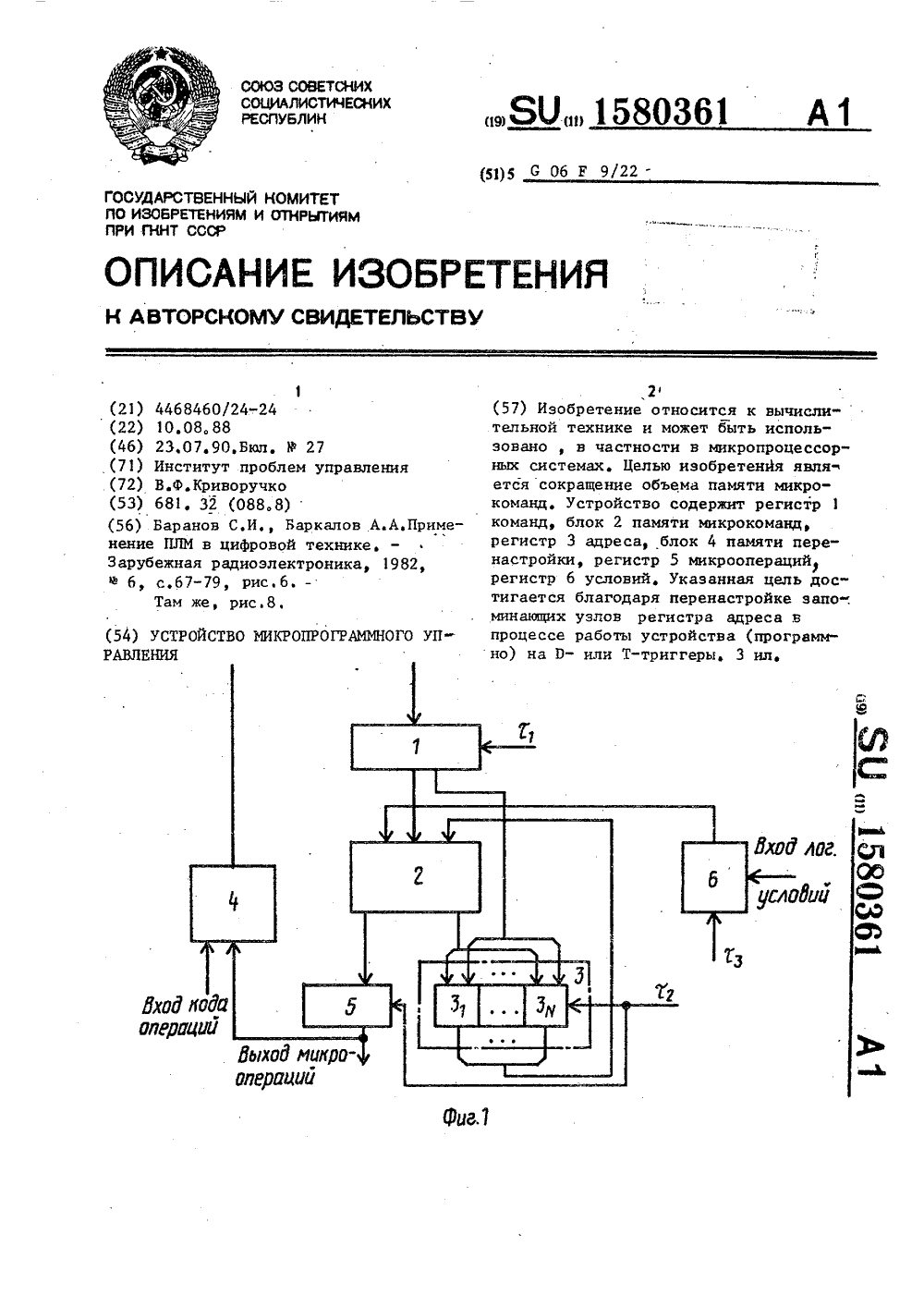

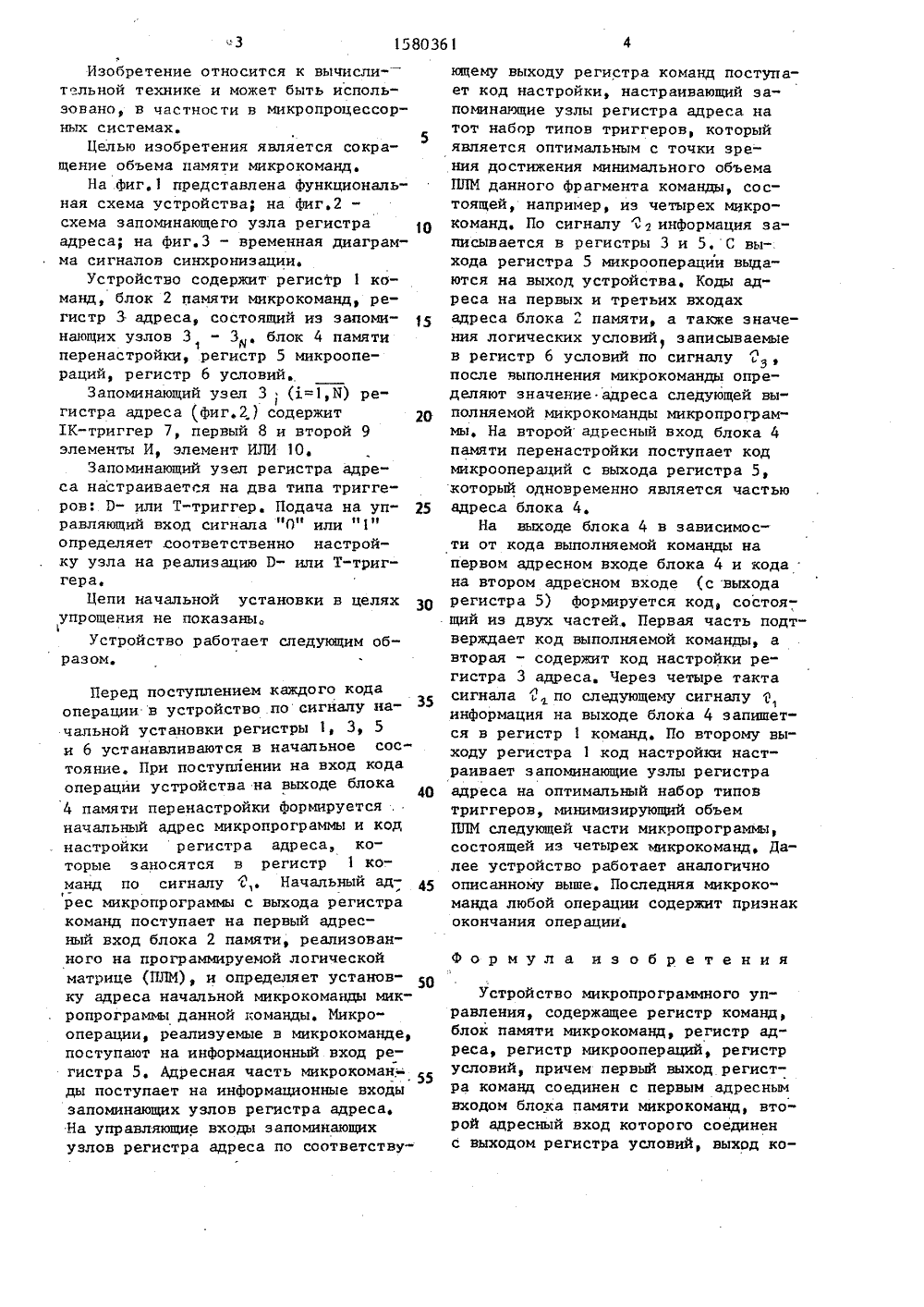

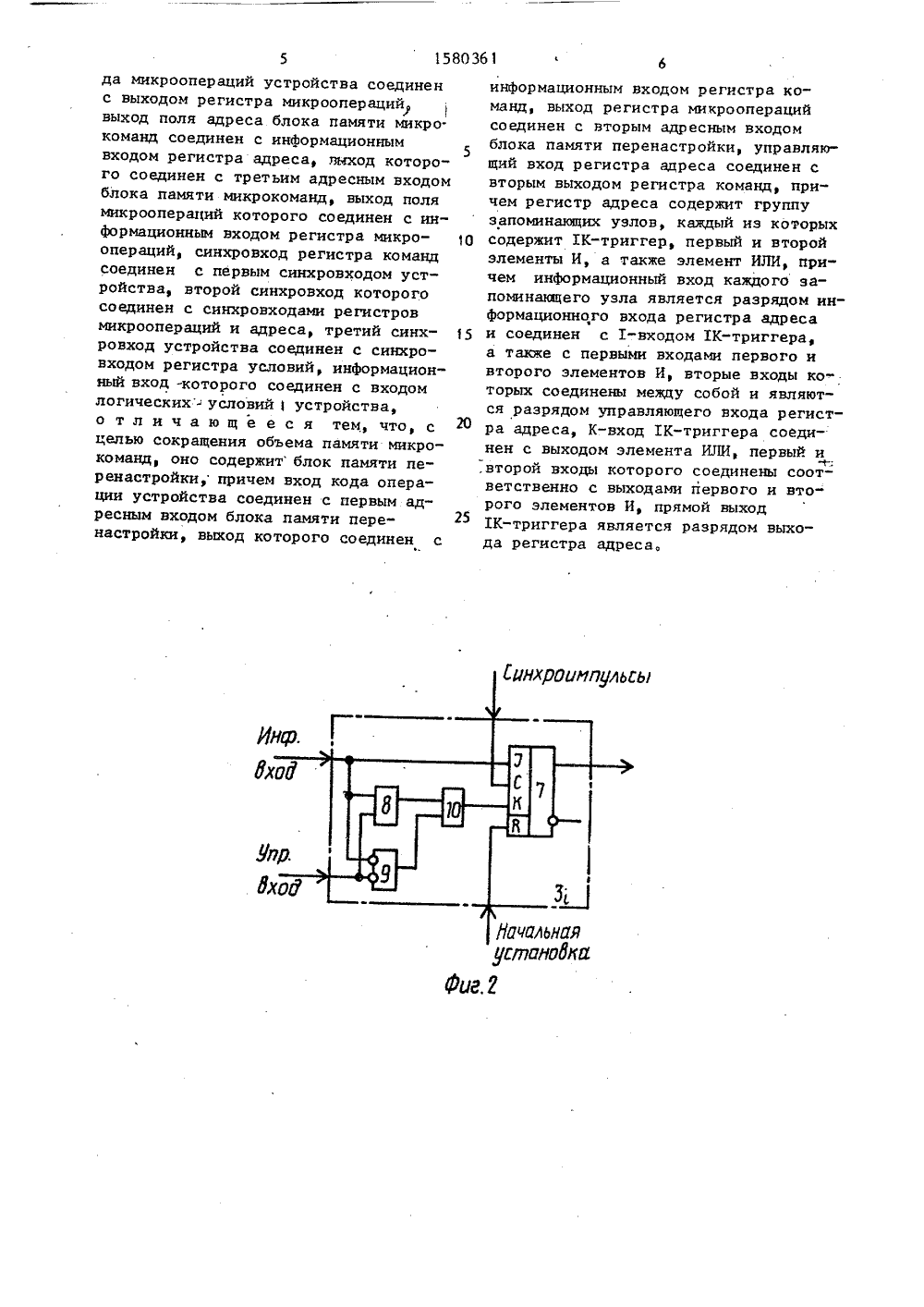

(ц)5 С 06 Р 9 ГОСУДАРСТВЕННЫПО ИЗОБРЕТЕНИЯМПРИ П(НТ СССР КОМИТЕТОТНРЫТИЯМ ПИСА ЗОБРЕТЕНИЯ К АВТОВСКОМУ ЕЛЬСТВ(5 7) Из о бр етение о тно сится ктельной технике и может бытьзовано , в частности в микроных системах. Целью изобретенется сокращение объема памятикоманд, Устройство содержиткоманд, блок 2 памяти микрокорегистр 3 адреса, блок 4 памянастройки, регистр 5 микроопрегистр 6 условий, Указаннаятигается благодаря перенастроминающих узлов регистра адрепроцессе работы устройства (но) на П- или Т-триггеры, 3 ил(71) Институт проблем управления(54) УСТРОЙСТВО МИКРОПРОГРРАВЛЕНИЯ микроегистр 1 манд,ти пере- рацийцель дос" йке запоса впр о граммИзобретение относится к вычислительной технике и может быть использовано, в частности в микропроцессорных системах,Целью изобретения является сокращение объема памяти микрокоманд,На фиг,1 представлена функциональная схема устройства; на фиг,2 схема запоминающего узла регистраадреса; на фиг.3 - временная диаграмма сигналов синхронизации.Устройство содержит регистр 1 команд, блок 2 памяти микрокоманд, регистр 3 адреса, состоящий из запоминающих узлов 3 - 3, блок 4 памятиперенастройки, регистр 5 микроопераций, регистр 6 условий,Запоминающий узел 3, (1=1,И) регистра адреса (фиг,2содержит 2 О1 К-триггер 7, первый 8 и второй 9элементы И, элемент ИЛИ 10.Запоминающий узел регистра адреса настраивается на два типа триггеров: Э- или Т-триггер. Подача на уп" 25равляющий вход сигнала "0" или "1"определяет соответственно настройку узла на реализацию 0- или Т-триггера,Цепи начальной установки в целях 30упрощения не показаны.Устройство работает следующим образом. Перед поступлением каждого кода операции в устройство по сигналу на 35 чальной установки регистры 1, 3, 5 и 6 устанавливаются в начальное сос тояние. При поступлении на вход кода операции устройства на выходе блока 4 памяти перенастройки формируется, начальный адрес микропрограммы и код настройки регистра адреса, которые заносятся в регистр 1 команд по сигналу ,. Начальный ад рес микропрограммы с выхода регистра команд поступает на первый адресный вход блока 2 памяти, реализованного на программируемой логической матрице (ПЛМ), и определяет установ ку адреса начальной микрокоманды микропрограммы данной команды, Микро- операции, реализуемые в микрокоманде, поступают на информационный вход регистра 5, Адресная часть микрокоман.- ды поступает на информационные входы запоминающих узлов регистра адреса, На управляющие входы запоминающих узлов регистра адреса по соответству из обретения Формул а Устройство микропрограммного управления, содержащее регистр команд, блок памяти микрокоманд, регистр адреса, регистр микроопераций, регистр условий, причем первый выход регистра команд соединен с первым адресным входом блока памяти микрокоманд, второй адресный вход которого соединен с выходом регистра условий, выхрд коющему выходу регистра команд поступает код настройки, настраивающий запоминающие узлы регистра адреса натот набор типов триггеров, которыйявляется оптимальным с точки зрения достижения минимального объемаПЛМ данного фрагмента команды, состоящей, например, иэ четырех микрокоманд, По сигналу г информация записывается в регистры 3 и 5. С выхода регистра 5 микрооперации выдаются на выход устройства. Коды адреса на первых и третьих входахадреса блока 2 памяти, а также значения логических условий записываемыев регистр 6 условий по сигналу 2,после выполнения микрокоманды определяют значение адреса следующей выполняемой микрокоманды микропрограммы, На второй адресный вход блока 4памяти перенастройки поступает кодмикроопераций с выхода регистра 5,который одновременно является частьюадреса блока 4.На выходе блока 4 в зависимости от кода выполняемой команды напервом адресном входе блока 4 и кода .на втором адресном входе с выходарегистра 5) формируется код, состоящий из двух частей., Первая часть подтверждает код выполняемой команды, авторая - содержит код настройки регистра 3 адреса, Через четыре тактасигналапо следующему сигналу Гинформация на выходе блока 4 запишется в регистр 1 команд, По второму выходу регистра 1 код настройки настраивает запоминающие узлы регистраадреса на оптимальный набор типовтриггеров, минимизирующий объемПЛМ следующей части микропрограммы,состоящей из четырех микрокоманд, далее устройство работает аналогичноописанному выше. Последняя микрокоманда любой операции содержит признакокончания операции,1580361 установи да микроопераций устройства соединенс выходом регистра микрооперацийвыход поля адреса блока памяти микро.команд соединен с информационнымвходом регистра адреса, выход которого соединен с третьим адресным входомблока памяти микрокоманд, выход полямикроопераций которого соединен с информационным входом регистра микроопераций, синхровход регистра командсоединен с первым синхровходом устройства, второй синхровход которогосоединен с синхровходами регистровмикроопераций и адреса, третий синхровход устройства соединен с синхровходом регистра условий, информационный вход -которого соединен с входомлогических условийустройства,о т л и ч а ю щ е е с я тем, что, сцелью сокращения объема памяти микрокоманд, оно содержит блок памяти перенастройки, причем вход кода операции устройства соединен с первым адресным входом блока памяти перенастройки, выход которого соединен с информационным входом регистра команд, выход регистра микрооперацийсоединен с вторым адресным входом 5блока памяти перенастройки, управляющий вход регистра адреса соединен свторым выходом регистра команд, причем регистр адреса содержит группузапоминающих узлов, каждый из которых 1 О содержит 1 К-триггер, первый и второйэлементы И, а также элемент ИЛИ, причем информационный вход каждого запоминакцего узла является разрядом информационного входа регистра адреса 15 и соединен с Е-входом 1 К-триггера,а также с первыми входами первого ивторого элементов И, вторые входы которых соединены между собой и являются разрядом управляющего входа регистра адреса, К-вход 1 К-триггера соединен с выходом элемента ИЛИ, первый и,второй входы которого соединены соответственно с выходами первого и второго элементов И, прямой выход1 К-триггера является разрядом выхода регистра адреса.Корр ек али Заказ 2013 Тираж 570 ПодписноеВНИИПИ Государственного комитета по изобретениям и открытиям при113035, Москва, Ж, .Раушская наб., д. 45 Т СЧСР о"издательский комбина Патент", г, Ужгород, у гарин извод

СмотретьЗаявка

4468460, 10.08.1988

ИНСТИТУТ ПРОБЛЕМ УПРАВЛЕНИЯ

КРИВОРУЧКО ВИТАЛИЙ ФЕДОРОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного

Опубликовано: 23.07.1990

Код ссылки

<a href="https://patents.su/4-1580361-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Устройство для арбитража запросов

Случайный патент: Устройство для определения диэлектрических свойств обуви и ее деталей