Устройство для вычисления функции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

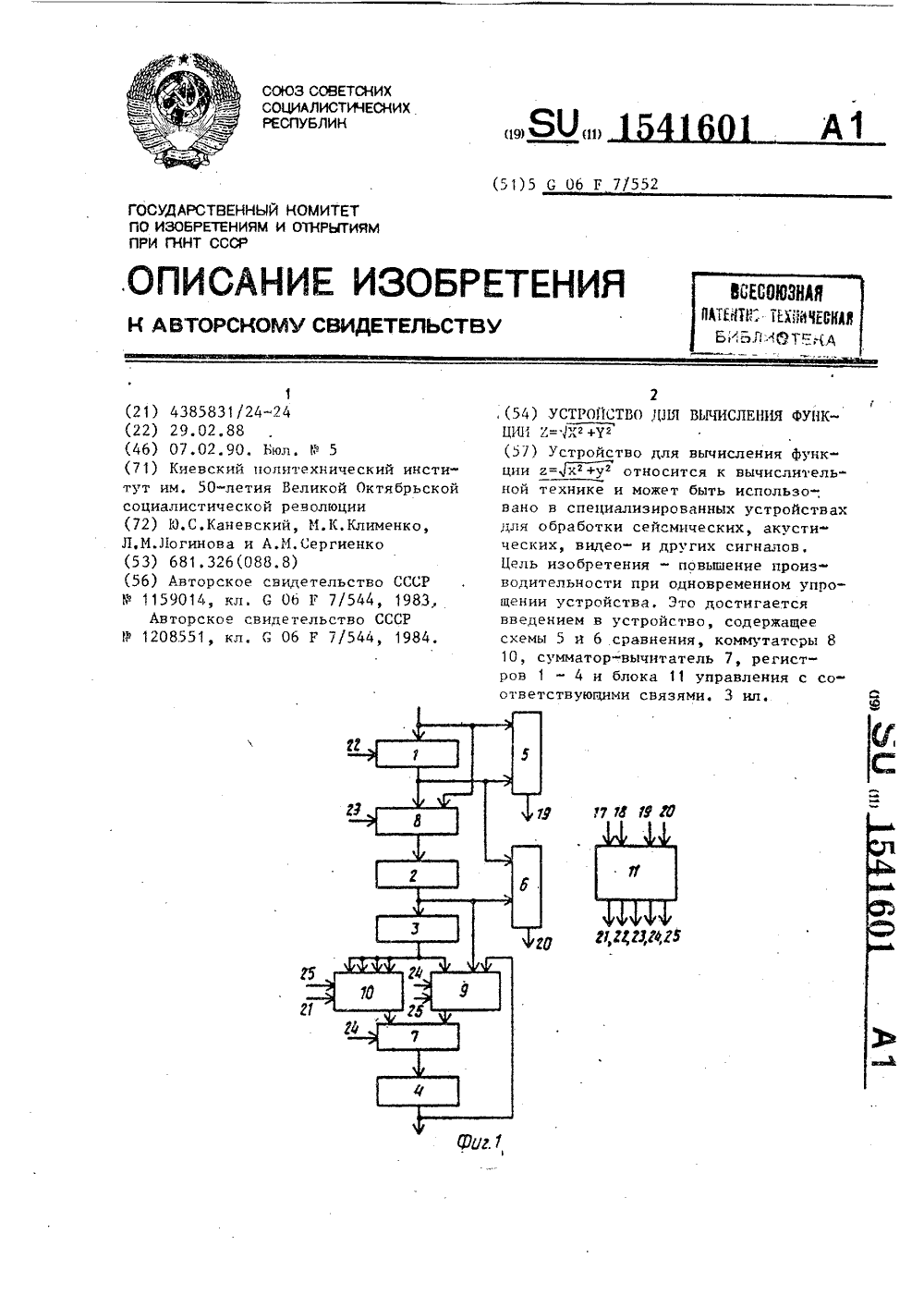

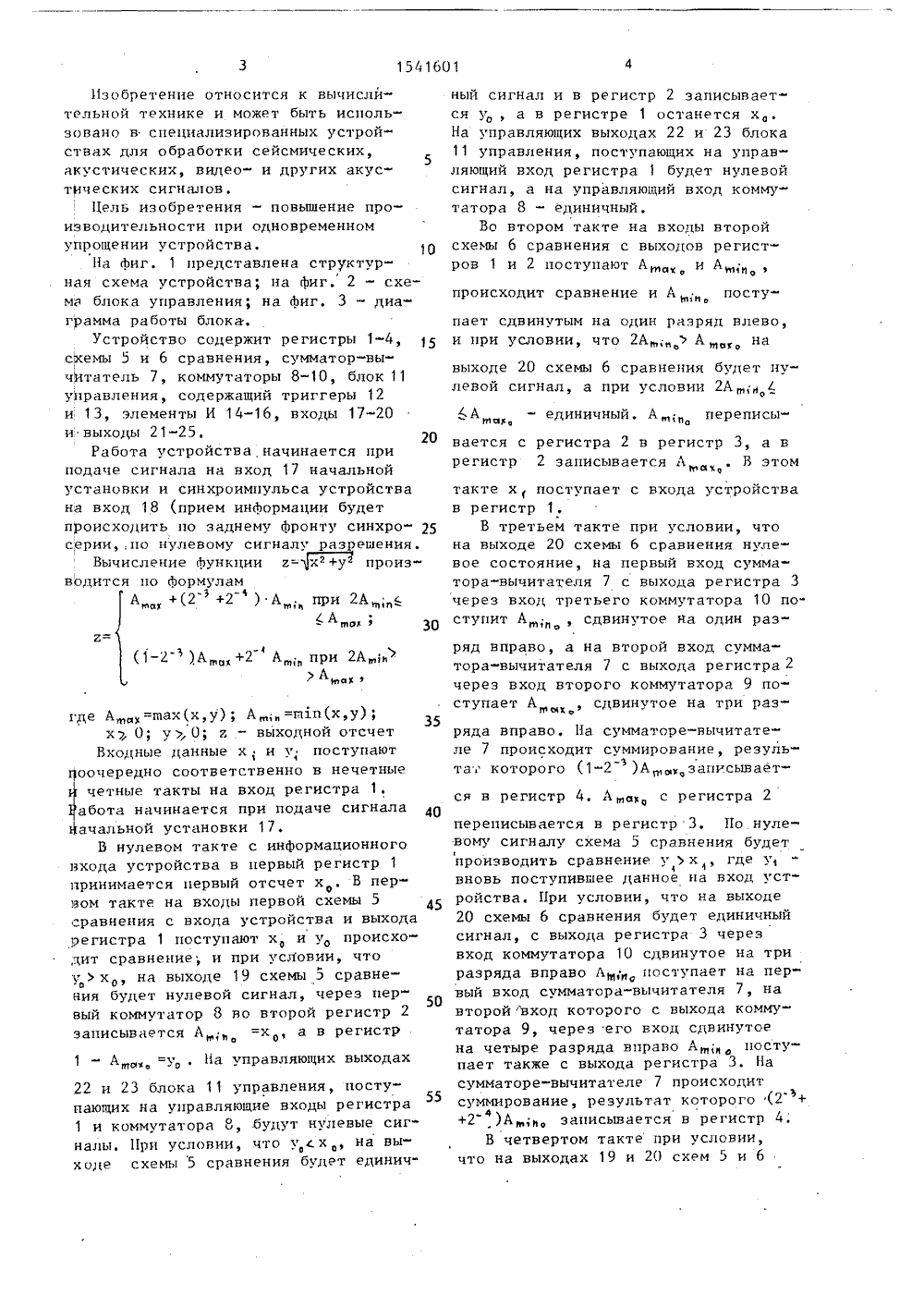

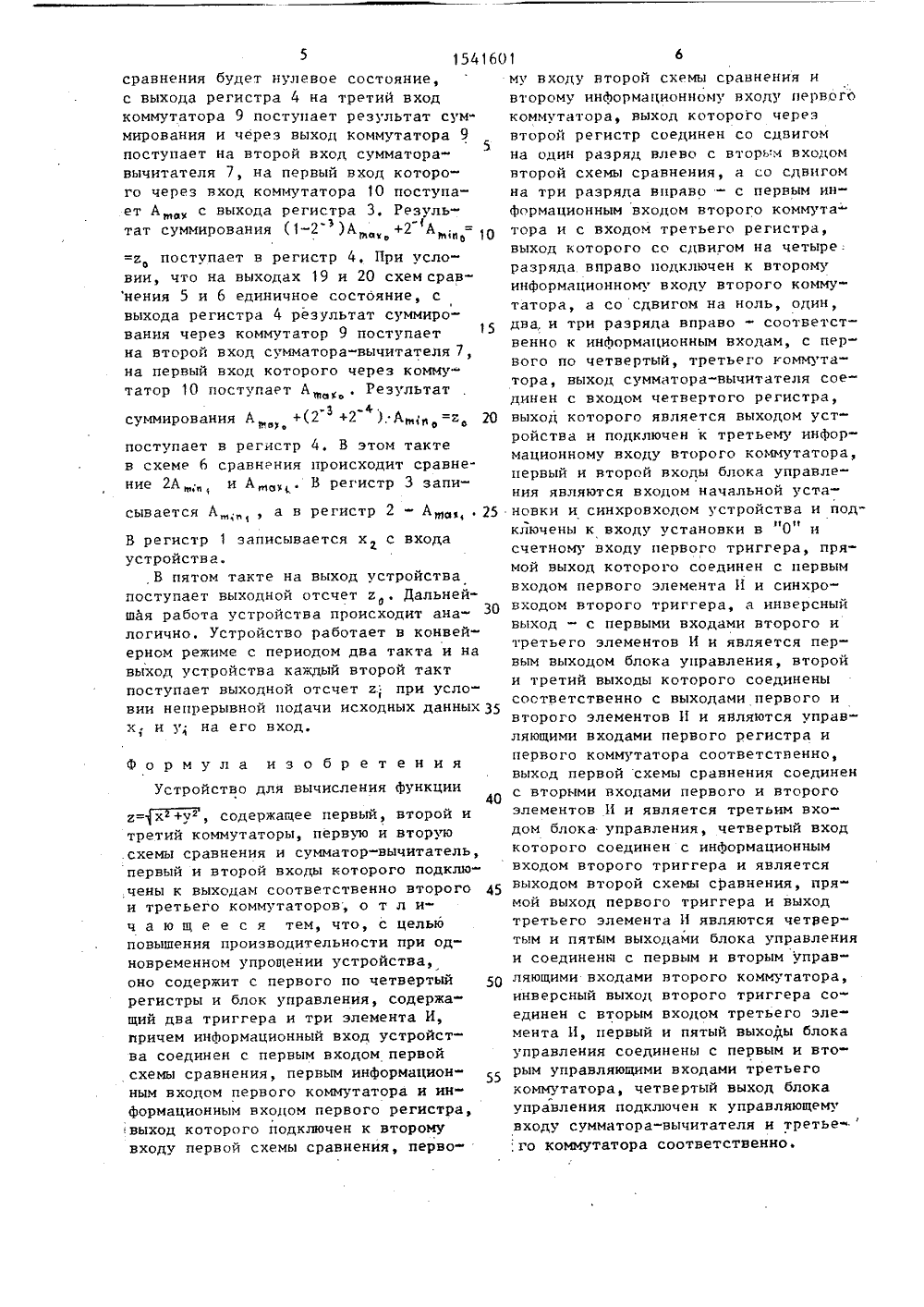

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН 19) Е 11) 51)5 С 06 ПИСАНИЕ ИЗОБРЕТЕНИ 77 78 РУ ГОСУДАРСТВЕННЫЙ НОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР Н АВ ГОРСКОМУ СВИДЕТЕЛЬСТВ(71) Киевский политехнический институт им. 50-летия Великой Октябрьскосоциалистической революции(56) Авторское свидетельство СССРР 1159014, кл. С 06 1 7/544, 1983,Авторское свидетельство СССРР 1208551, кл, С 06 Г 7/544, 1984. 2г 54) УСТРОЙСТВО Л 1 ЬЧ ВИЧИСЛЕИИЯ ФУНКЛИИ Е - г.чг еуг(57) Устройство для вычисления функПии Я=ггхгеУг относитсЯ к вычислительной технике и может быть использо-,вано в специализированных устройствахдля обработки сейсмических, акустических, видео- и других сигналов,Цель изобретения - повышение производительности при одновременном упрощении устройства, Это достигаетсявведением в устройство, содержащеесхемы 5 и 6 сравнения, коммутаторы 810, сумматор-вычитатель 7, регистров 1 - 4 и блока 11 управления с соответствующими связями. 3 ил,Изобретение относится к вычислительной технике и может быть использовано в специализированных устройствах для обработки сейсмических, акустических, видео- и других акустических сигналов,11 ель изобретения - повышение производительности при одновременном упрощении устройства. 10На фиг. 1 представлена структурная схема устройства; на фиг. 2 - схема блока управления; на фиг, 3 - диаграмма работы блока.Устройство содержит регистры 1-4, схемы 5 и 6 сравнения, сумматор-вычгтатель 7, коммутаторы 8-10, блок 11 управления, содержащий триггеры 12 и 13, элементы И 14-16, входы 17-20 и выходы 21-25.20Работа устройства начинается при подаче сигнала на вход 17 начальной установки и синхроимпульса устройства на вход 18 (прием информации будет происходить по заднему фронту синхро серии,.по нулевому сигналу разрешения.Выкиолеиие Фуикиии з-кеу производится по формулам А,+(2 +2 ) Апри 2 А(Авар з 30 (1 - 2 )Ава+2 Арр при 2 Аь))А где А,=пгах(х,у); А зз;=ш 1.п(хрУ) рх) О; у , О; и - выходной отсчетВходные данные х; и у поступают г оочередно соответственно в нечетныечетные такты на вход регистра 1, абота начинается при подаче сигнала 40 ачальной установки 17.В нулевом такте с информационного входа устройства в первый регистр 1 принимается первый отсчет х , В первом такте на входь 1 ервой схем 5 45 сравнения с входа устройства и выхода регистра 1 поступают хр и у происходит сравнение; и при условии, что ;х , на выходе 19 схемы 5 сравнения будет нулевой сигнал, через первый коммутатор 8 во второй регистр 2 записывается А =х , а в регистр 1 - А , =у, . На управляющих выходах 22 и 23 блока 11 управления, посту 55 пающих на управляющие входы регистра 1 и коммутатора 8, будут нулевые сигналы. 11 ри условии, что у,схна выходе схемы 5 сравнения будет единич"ный сигнал и в регистр 2 записывается у , а в регистре 1 останется х На управляющих выходах 22 и 23 блока 11 управления, поступающих на управляющий вход регистра 1 будет нулевой сигнал, а на управляющий вход коммутатора 8 - единичный.Во втором такте на входы второй схемы 6 сравнения с выходов регистров 1 и 2 поступают А,и А;р 1 к 1 О ф происходит сравнение и А ; поступает сдвинутым на один разряд влево,и при условии, что 2 Аъ А, на выходе 20 схемы 6 сравнения будет нулевой сигнал, а при условии 2 А и,4вается с регистра 2 в регистр 3, а врегистр 2 записывается Л. В этомФОатрряд вправо, а на второй вход сумматора-вычитателя 7 с выхода регистра 2 через вход второго коммутатора 9 поступает А, сдвинутое на три раз- ек ряда вправо. На сумматоре-вычитателе 7 происходит суммирование, результа которого (1-2)А,записывается в регистр 4Аа, с регистра 2 переписывается в регистр 3. По нулевому сигналу схема 5 сравнения будет производить сравнение у ) х , где у, вновь поступившее данное на вход устройства, При условии, что на выходе 20 схемы 6 сравнения будет единичный сигнал с выхода регистра 3 через вход коммутатора 10 сдвинутое на три разряда вправо Л поступает на первый вход сумматора-вычитателя 7, на второй вход которого с выхода коммутатора 9, через его вход сдвинутое на четыре разряда вправо А;4 поступает также с выхода регистра 3. На сумматоре-вычитателе 7 происходит-4В четвертом такте при условии, что на выходах 19 и 20 схем 5 и 6 такте х г поступает с входа устройства в регистр 1,В третьем такте при условии, что на выходе 20 схемы 6 сравнения нулевое состояние, на первый вход сумматора-вычитателя 7 с выхода регистра 3 через вход третьего коммутатора 10 по" ступит А; , сдвинутое на один раззз" зП ззсравнения будет нулевое состояние, с выхода регистра 4 на третий вход коммутатора 9 поступает результат сум" мирования и через выход коммутатора 9 поступает на второй вход сумматора 5 вычитателя 7, на первый вход которого через вход коммутатора 10 поступает Ас выхода регистра 3, Результат суммирования (1-2 )А +2 А,; = 10 =г, поступает в регистр 4, При условии, что на выходах 19 и 20 схем сравнения 5 и 6 единичное состояние, с выхода регистра 4 результат суммирования через коммутатор 9 поступает на второй вход сумматора-вычитателя 7, на первый вход которого через коммутатор 10 поступает А , Результат суммирования А, +(2 +2 ). Аы, =г 20 поступает в регистр 4, В этом такте в схеме б сравнения происходит сравне" ние 2 А ;, и А . В регистр 3 записывается А, а в регистр 2 - А 1 ятйв,25В регистр 1 записывается хг с входа устройства.В пятом такте на выход устройства поступает выходной отсчет г, Дальнейшйя работа устройства происходит аналогично, Устройство работает в конвейерном режиме с периодом два такта и на выход устройства каждый второй такт поступает выходной отсчет г.; при условии непрерывной подачи исходных данных 35 х и у на его вход. Формула изобретенияУстройство для вычисления функции40в=хетуе, оодервапее первый, второй итретий коммутаторы, первую и вторую,схемы сравнения и сумматор-вычитатель,первый и второй входы которого подключены к выходам соответственно второго 45и третьего коммутаторов, о т л ич а ю щ е е с я тем, что, с цельюповышения производительности при одновременном упрощении устройства,оно содержит с первого по четвертыйрегистры и блок управления, содержащий два триггера и три элемента И,причем информационный вход устройства соединен с первым входом первойсхемы сравнения, первым информационным входом первого коммутатора и информационным входом первого регистра,.выход которого подключен к второмувходу первой схемы сравнения, первому входу второй схемы сравнения и второму информационному входу первого коммутатора, выход которого через второй регистр соединен со сдвигом на один разряд влево с вторым входом второй схемы сравнения, а со сдвигом на три разряда внряво - с первым информационным входом второго коммута тора и с входом третьего регистра, выход которого сс сдвигом на четыре. разряда вправо подключен к второму информационному входу второго коммутатора, а со сдвигом на ноль, один, два, и три разряда вправо - соответственно к информяционным входам, с первого по четвертый, третьего коммутатора, выход сумматора-вычитателя соединен с входом четвертого регистра, выход которого является выходом устройства и подключен к третьему информационному входу второго коммутатора, первый и второй входы блока управления являются входом начальной установки и синхровходом устройства и подключены к входу установки в 0 и счетному входу первого триггера, прямой выход которого соединен с первым входом первого элемента И и синхровходом второго триггера, я инверсный выход - с первыми входами второго и третьего элементов И и является первым выходом блока управления, второй и третий выходы которого соединены соответственно с выходами первого и второго элементов И и являются управляющими входами первого регистра и первого коммутатора соответственно, выход первой схемы сравнения соединен с вторыми входами первого и второго элементов И и является третьим входом блока управления, четвертый вход которого соединен с информационным входом второго триггера и является выходом второй схемы сравнения, прямой выход первого триггера и выход третьего элемента И являются четвертым и пятым выходами блока управления и соединенш с первым и вторым чправляющими входами второго коммутатора, инверсный выход второго триггера соединен с вторым входом третьего элемента И, первый и пятый выхопы блока управления соединены с первым и вторым управляющими входами третьего коммутатора, четвертый выход блока управления подключен к управляющему входу сумматора-вычитателя и третье го коммутатора соответственно.1541 б 01 ор Т.Малец ри ГКНТ СС ени кая тельский комбинат Патент", г. Ужгород, ул. Гагарина, 10 оизводствецноСоставитель А.дактор А,Козориз Техред Л.Олийн Заказ 281 Тираж 562 ВИИИПИ Государственного комитета по изоб 113035, Москва, Ж, Ра

СмотретьЗаявка

4385831, 29.02.1988

КИЕВСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. 50-ЛЕТИЯ ВЕЛИКОЙ ОКТЯБРЬСКОЙ СОЦИАЛИСТИЧЕСКОЙ РЕВОЛЮЦИИ

КАНЕВСКИЙ ЮРИЙ СТАНИСЛАВОВИЧ, КЛИМЕНКО МАРИЯ КОНСТАНТИНОВНА, ЛОГИНОВА ЛЮДМИЛА МИХАЙЛОВНА, СЕРГИЕНКО АНАТОЛИЙ МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 7/552

Метки: вычисления, функции

Опубликовано: 07.02.1990

Код ссылки

<a href="https://patents.su/4-1541601-ustrojjstvo-dlya-vychisleniya-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления функции</a>

Предыдущий патент: Устройство для преобразования координат

Следующий патент: Устройство для вычисления модуля вектора

Случайный патент: Герметичный электронасосный агрегат