Устройство для обнаружения сигналов и измерения их параметров

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1478145

Авторы: Блюм, Голованов, Кольцова, Прасолов, Сила-Новицкий

Текст

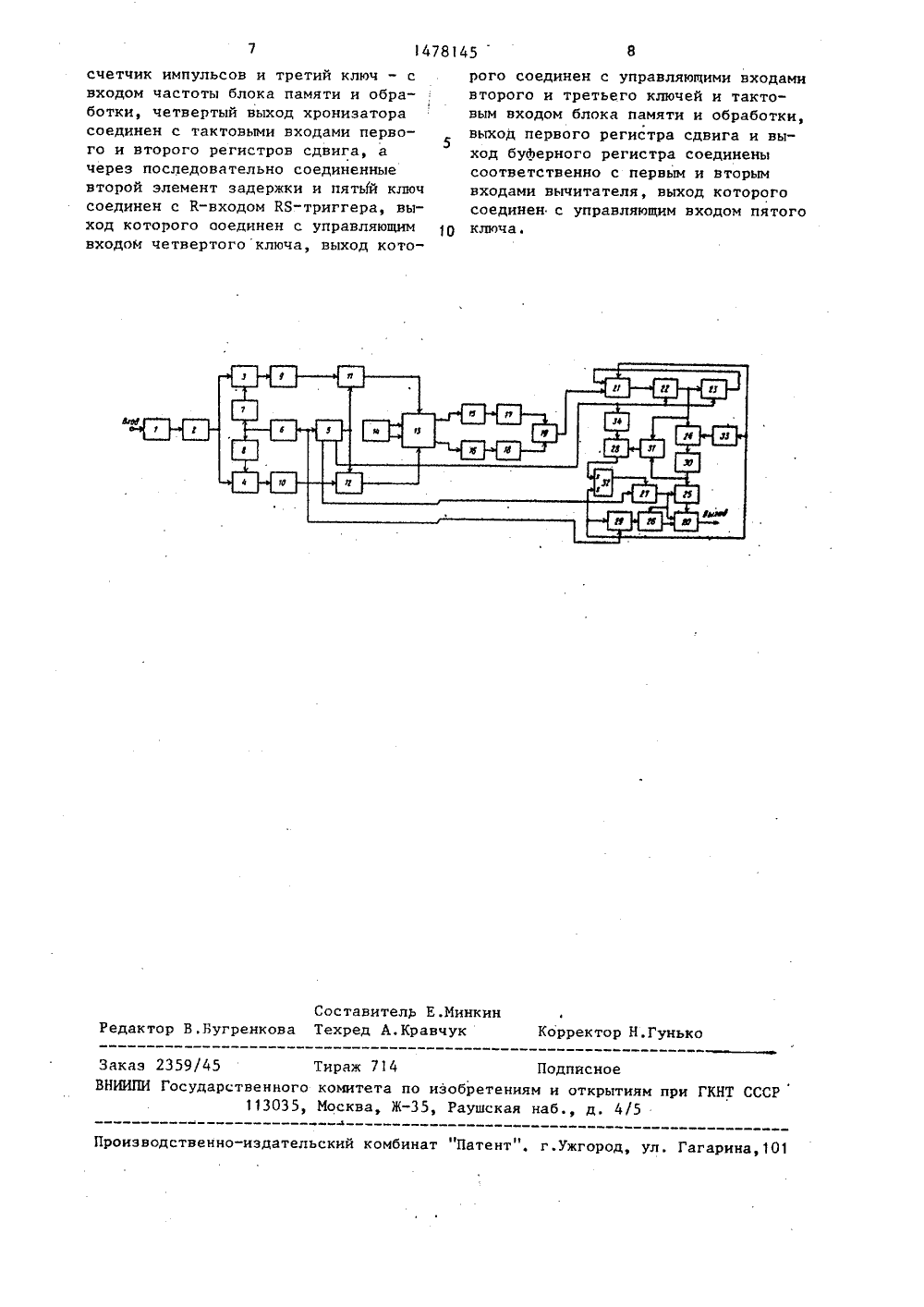

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНРЕСПУБЛИН А 1 В 4 С 01 К 23/16 ГОСУДАРСТВЕННЫЙПО ИЗОБРЕТЕНИЯМ ИПРИ ГКНТ СССР ИТЕТРЫТИЯМ ЮИРЕТЕНИЯ АНИ ЛЬСТВУ ЖЕНИЯАМЕ ТРОВ к анал ретения аружени налов идены комга, пять зобретение отн трального анал елью изобретен е достоверност нике ситс за пек вля ся повыения сигобна ала фу иональ На чертеже показ ная,схема устройств Устройство содер Фильтр 1, аналого-ц зователь 2, первый жители 3 и 4, хронисовои преобра- перемно- генераторой Фазы, 10 ниж- оператив 12, пеит полофровойвторойатор 5,выи и тор 6 кода преобраэов первый и в них частот фазы, пе тели 7 и орой Лил кодры 9 второи п 11 и первыиющие бл е запоми К АВТОРСКОМУ СВ(56) Авторское свидетельство ССС1 742818, кл. С 01 К 23/16, 1976,Авторское свидетельство СССРУ 830251, кл.С О( К 23/16, 1981,(54) УСТРОЙСТВО Лля ОБНАРУ НАЛОВ И ИЗМЕРЕНИЯ ИХ ЛАР (57) Изобретение относится заторам спектра. Цель изо повыщение достоверности об сигналов. Для достижения ц ройство для обнаружения си измерения их параметров вв мутатор, два регистра сдв 80147814 ключей, счетчик импульсов, буферный регистр, вычитатель, КБ-триггер и два элемента задержки. Устройство также содержит полосовой фильтр 1, аналого-цифровой преобразователь, два перемножителя, хрониэатор, генератор кода фазы, два преобразователя кода Фазы, два фильтра. нижних частот, два оперативных запоминающих блока, перемножитель комплексных сигналов, постоянный запоминающий блок, два накапливающих сумматора, два блока возведения в квадрат, сумматор, блок памяти и обработки, Устройство обнаружения сигналов и измерения их параметров может быть использовано в мно-гоканальных приемных системах со случайным доступом для обнаружения не-: скольких сигналов с неизвестными частотой и амплитудой на фоне шума и пирокополосных помех. 1 ил. ремножитель 13 комплексных сигналов, постоянный запоминающий блок 14, первый и второй накапливающие сумматоры 15 и 6, первый и второй блоки 17 и 18 возведения в квадрат, сумматор 19, блок 20 памяти и обработки, коммутатор 21, два регистра 22 и 23 сдвига, пять ключей 24 - 28, счетчик 29 импульсов, буферный регистр 30, вычитатель 31, КБ-триггер 32 и два элемента 33 и 34 задержки.Выход полосового фильтра 1 соединен с входом аналого-цифрового преобразователя 2, выход которого соединен с первыми входами первого и второго перемножителей 3 и 4, первый147845 1 О 15 20 30 35 40 45 50 55 вход хронизлторл 5 соединен с входомгенератора 6 кода Фазы, выход которого через первый преобразователь 7 кодл Фазы соединен с вторым входом первого перемножителя 3 и через второйпреобразователь 8 кода Фазы соединенс вторым входом второго перемножите. -ля 4, выходы первого и второго перемножителей 3 и 4 через Фильтры 9и 1 О нижних частот соединены с входами первого и второго оперативныхзапоминающих блоков 11 и 12, тактовые входы которых соединены с вторымвыходом хронизлтора 5, выходы первого и второго оперативных запоминающих блоков 11 и 12 соединены с первыми входами перемножителя 13 комплексных сигналов, вторые входы которого соединены с выходами постоянного запоминающего блока 14, каждыйиз выходов перемножителя 13 комплексных сигналов через последовательно соединенные накапливающий сумматор 15 (16) и блок 17 (18) возведения в квадрат соединен с соответствующим входом сумматора 19, выход ко.торого соединен с первым входом коммутатора 21. Второй нкод коммутлторл 21 соединен с его выходом черезднл последовательно включенных регистра 22 и 23 сднигл, выход первогогруппового регистра 22 сдвига через последовательно включенные первыйключ 24, буферный регистр 30 и второй ключ 25 соединен с входом уровняблока 20 памяти и обработки. Первыйвыход хронизлторл 5 соединен с входом сброся счетчика 29 импульсов,третий выход хронизатара 5 соединеннепосредственно с 8-нходом КБ-триггера, входом четвертого ключа 27,управляющим входом коммутатора 21,через первый элемент 33 задержки - суправляющим входом первого .ключа 24и через последовательно соединенныесчетчик 29 импульсов и третий ключ26 - с входом частоты блока 20 памяти и обработки, четвертый ключ 26с входом члстоты блока 20 памяти иобработки, четвертый выход хронизатора 5 соединен непосредственно стактовыми входами первого и второгорегистров 22 и 23 сдвига и черезпоследовательно соединенные второйэлемент 34 задержки и пятый ключ 28соединен с К-входом Ю-триггера 32,выход которого соединен с унрлвляющим входом четвертого ключа 27, выхад которого соединен с управляющими входами второго 25 и третьего 26 ключей и тактовым входом блока 20 памяти и обработки, нхы 1 од первого регистрл 22 сдвига и выход буферного регистра 30 соединены соответственно с первым и вторым входами нычитателя 31, выход которого соединен с управляющим входом пятого ключа 28.Устройство работает следующим образом.После предварительной фильтрации сигнала паласовым Фильтром 1 и перевода его н цифровую Форму аналогоцифровым преобразователем 2 вычисляется его дискретный спектр, для чего сначала сигнал при помощи генератора 6 кода Фазы, преобразователей 7 и 8 кода Фазы, перемножителей 3 и 4 и Фильтров 9 и 10 нижних частот преобразуется в импульс с ЛЧМ-заполнением,л затем в согласованном Фильтре, состоящем из двух оперативных злпо 25 минающих блоков 11 и 12, перемножителя 13 комплексных сигнялон и двух на - клплинающих сумматоров 15 и 16 вычис -ляется свертка ЛЧМ-импульса с импульсной характеристикой согласованного Фильтра, записанной в постоянном запоминающем блоке 14, Блоки 17и 18 и сумматор 19 вычисляют мощность спектральных составляющих сигнала. Спектральные отсчеты с выхода сумматора 19 через коммутатор 21 поступают на вход первого регистра 22 сдвига, а с его выхода на вход второго регистра 23 сдвига. Между поступлением двух спектральных отсчетов производится рециркуляция отсчетов. содержащихся в регистрах 22 и 23, и сравнение их при помощи нычитателя 31 с отсчетом с выхода регистра 22, переписанным предварительно через ключ 24 в буферный регистр 30, Если ни адин из отсчетов, записанных в регистрах 22 и 23, не превысил отсчета, находящегося в буферном регистре 30, ключ 28 останется закрытым, Ю-триггер 32 останется в исходном состоянии и тактовый сигнал выхода хронизатора 5 пройдет через ключ 27, обеспечив перезапись спектрального отсчета из буферного регистра 30 и соответствующего этому отсчету знлчения кода частоты из счетчика 29 (через ключи 25 и 26 соответ147845 45 50 стненно) в блок 20 памяти и обработки.Если хотя бы один из отсчетов, находящихся в регистрах 22 и 23, но время рециркуляции превысит отсвет, нпходящийся в буферном регистре 30, то сигнал с выхода вычитятеля 31откроет ключ 28 и К 8-триггер 32 перейдет н состояние, закрывающее 10 ключ 27. При этом перезапись спектрального отсчета из буАерного реги - стра 30 и соответствующего ему значения кода частоты из счетчика 29 в блок памяти и обработки произведена 15 не будет, После поступления очередного спектрального отсчета с выхода сумматора 19 процедура рециркуляции и сравнения повторяется. Хрониэатор 5 обеспечивает также тяктирование генератора 6 кода Ааэы, первого и второго оперативных запоминающих блоков 11 и 12, счетчика 29 импульсов, первого и второго многоразрядных регистров 22 и 23 сдвига, запись оче редного отсчета с выхода сумматора 19 через коммутатор 2 в многоразрядный регистр сдвига 22, сброс счетчика 29, установку К 8-триггера 32 в исходное состояние и перезапись 30 отсчета с выхода регистра 22 в буферный регистр 30. Элементы 33 и Зч задержки служат для того, чтобы перезапись отсчетов происходила н установившемся режиме.35 Положительный эффект от предлагаемого устройства достигается эя счет того, что в блок 20 памяти и обработки будут поступать не все спектральные отсчеты, превышающие заданный порог, а лищь отсчеты, являющиеся локальными максимумами в частотной ок- рестности скорость перестройки частоты нявыходе преобразователей 7 и 8кода Аазы;период поступления отсчетон свыхода сумматора 19;длина регистров 22 и 23 сдвига. Формула изобретения Устройство для обнаружения сигналов и измерения их параметров, содержащее лолосовой фильтр, вход которого является входом устройства, а выход соединен с входом аналого-цифрового преобраэонятеля 1 выход которогосоединен с первыми входами первогои второго перемножителей, первыйвыход хрониэятора соединен с входомгенератора кода Аязы, выход которого через первый преобразователь кода фазы соединен с вторым входомпервого перемножителя, а через второй преобразователь кода Фазы соединен с вторым входом второго перемножителя, выходы первого и второго перемножителей через первый и второйАильтры нижних частот соответственно соединены с входами первого и второго оперативных запоминающих блоков, тактовые входы которых соединены с вторым выходом хрониэатора, выходы первого и второго оперативныхзапоминающих блоков соединены соответственно с первыми и вторыми входами перемножителя, комплексных сигналов, третий и четвертый входы которого соединены с выходами постоянного запоминающего блока, первый и второй выходы перемножителя комплексных сигналов через последовательно соединенные накапливающий сумматор и блок возведения в квадратсоответственно соединены с входамисумматора, а также блок памяти иобработки, выход которого являетсявыходом устройства, о т л и ч а ющ е е с я тем, что, с целью повышения достоверности обнаружения сигна"лов, в него введены коммутатор, дварегистра сдвига, пять ключей, счетчик импульсов, буферный регистр,вычитатель, КЯ-триггер и два элемента задержки, причем выход сумматора соединен с первым входом коммутатора, выход которого через два последовательно соединенных регистра сдвига соединен с вторым входом коммутатора, выход первого регистрасдвига через последовательно соединенные первый ключ, буАерный регистри второй ключ соединен с входом уровня блока памяти и обработки, первыйвыход хронизатора соединен с входомсброся счетчика импульсов, третий выход хронизаторя соединен с Я-входомКЯ-триггера, входом четвертого ключа, управляющим входом коммутатора,через первый элемент задержки - суправляющим входом первого ключа ичерез последовательно соединенныеЗаказ НИИПИ НТ ССС осударств 1ного комитета035, Москва, Ж м Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарин счетчик импульсов и третий ключ - свходом частоты блока памяти и обработки, четвертый выход хронизаторасоединен с тактовыми входами первого и второго регистров сдвига, ачерез последовательно соединенныевторой элемент задержки и пятью ключсоединен с К-входом КБ-триггера, выход которого аоединен с управляющимвходом четвертого ключа, выход которого соединен с управляющими входами второго и третьего ключей и тактовым входом блока памяти и обработки, 5выход первого регистра сдвига и выход буферного регистра соединены соответственно с первым и вторым входами внчитателя, выход которого соединен с управляющим входом пятого 10 ключа.

СмотретьЗаявка

4194043, 12.02.1987

ПРЕДПРИЯТИЕ ПЯ Г-4149

СИЛА-НОВИЦКИЙ СТАНИСЛАВ ЮЛИАНОВИЧ, ПРАСОЛОВ ВИКТОР АНДРЕЕВИЧ, БЛЮМ ВЛАДИМИР АЛЕКСАНДРОВИЧ, КОЛЬЦОВА АННА ЕФИМОВНА, ГОЛОВАНОВ АЛЕКСАНДР ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G01R 23/16

Метки: обнаружения, параметров, сигналов

Опубликовано: 07.05.1989

Код ссылки

<a href="https://patents.su/4-1478145-ustrojjstvo-dlya-obnaruzheniya-signalov-i-izmereniya-ikh-parametrov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения сигналов и измерения их параметров</a>

Предыдущий патент: Измеритель отношения количеств импульсов в двух чередующихся импульсных сериях

Следующий патент: Устройство для измерения нелинейных искажений четырехполюсника

Случайный патент: Устройство для расширения донной части шпура