Дельта-кодер

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

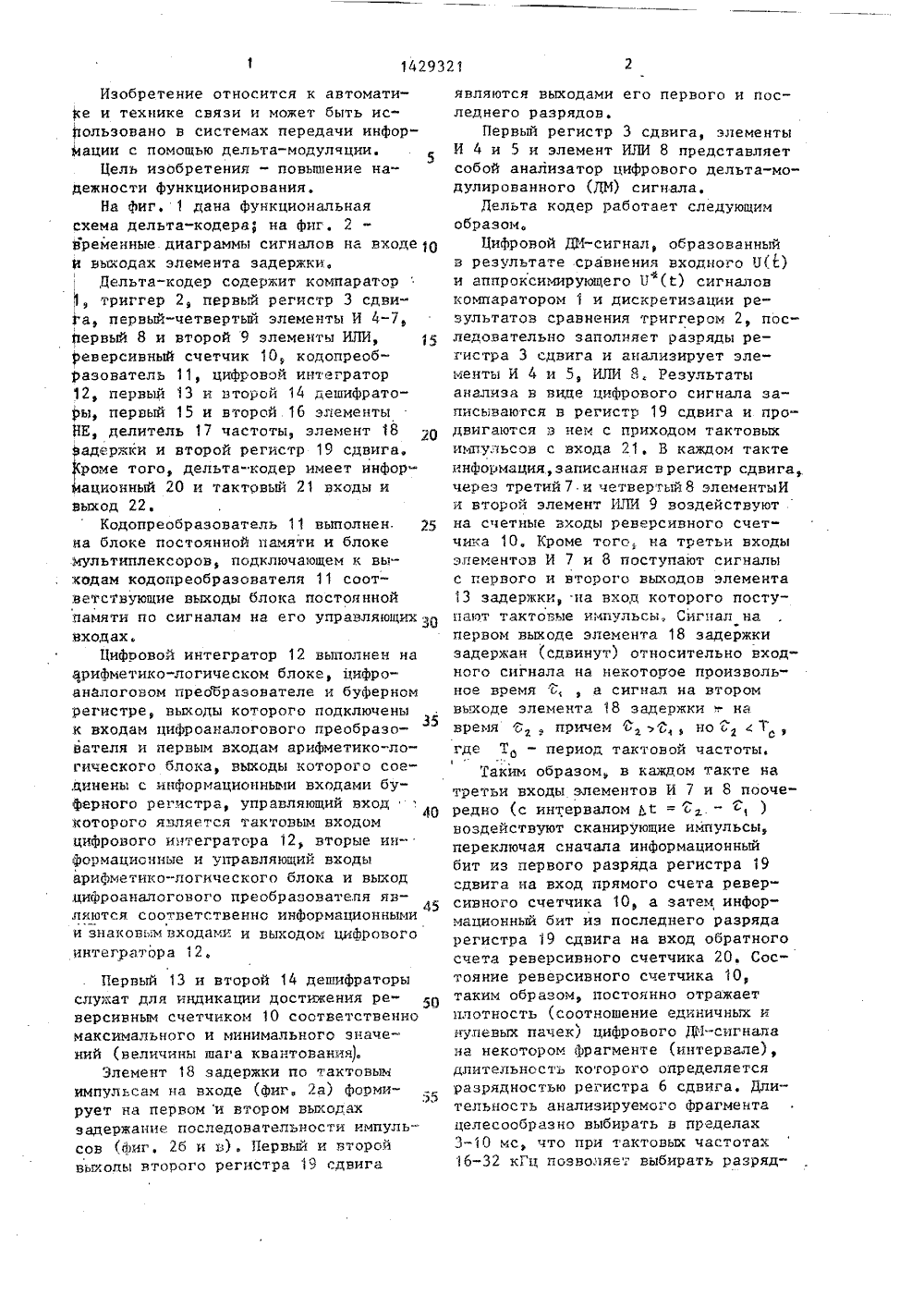

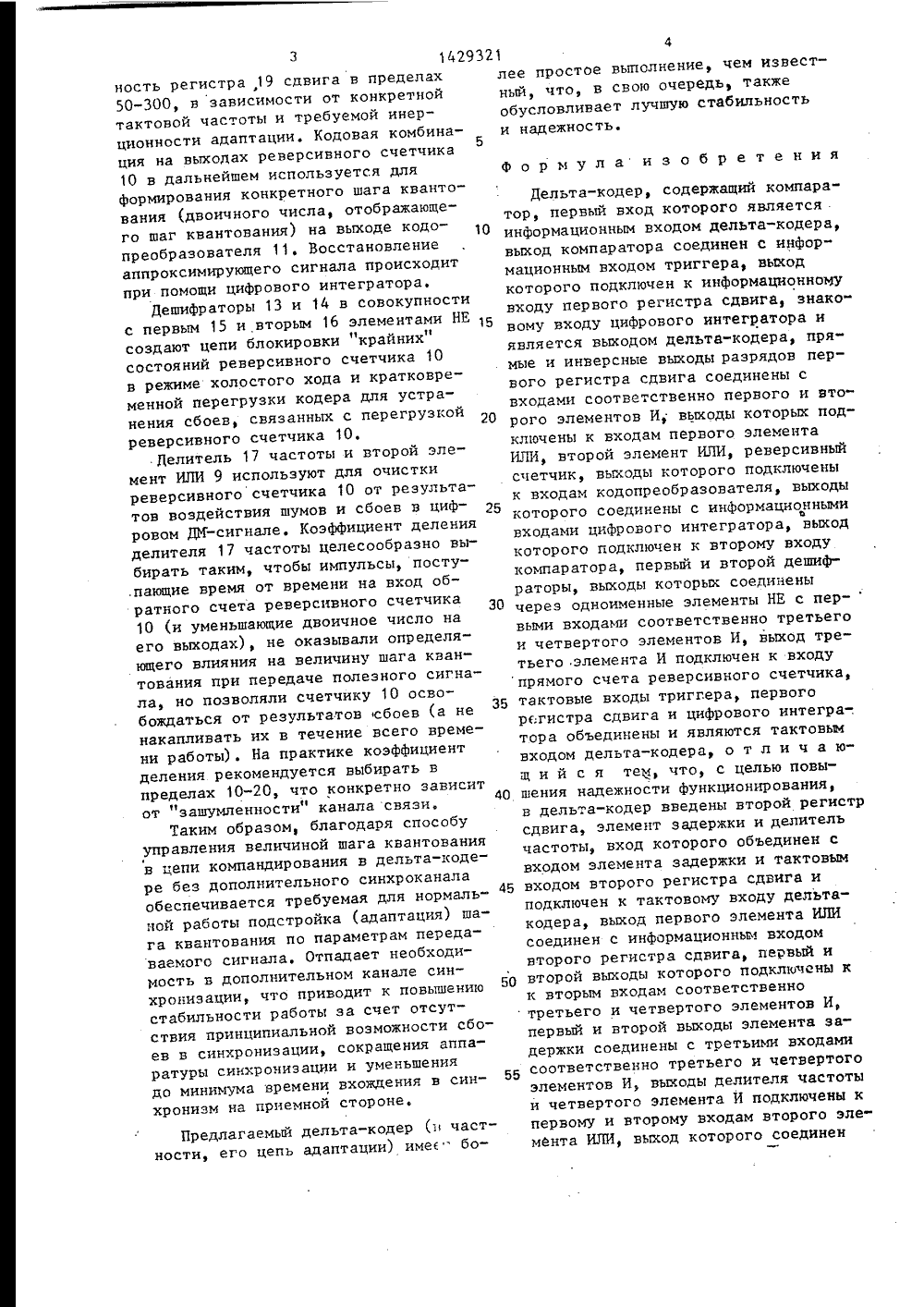

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 4 ноз ГОСУД ПО ДЕ ЗОБРЕТЕН ОПИСА АВТОРСКОМ ститут 984 984.СР985. ри вт ВЕННЫЙ КОМИТЕТ СССР ИЗОБРЕТЕНИЙ И ОТКРЫТ,ЯО 1429321 А 1 вание в системах передачи информациис помощью дельта-модуляции позволяетповысить надежность функционированиядельта-кодера, который содержит компаратор 1, триггер 2, регистр 3 сдвига, элементы И 4-7, элементы ИЛИ8, 9, реверсивный счетчик 10, кодопреобразователь 11, цифровой интегратор 12, дешифраторы 13, 14 и элементы НЕ 15, 16. Благодаря введению делителя 17 частоты, элемента 18 задержки и регистра 19 сдвига упрощается выполнение дельта-кодера, атакже отпадает необходимость в до,полнительном канале синхронизации ипередаче. 2 ил.Изобретение относится к автоматиКе и технике связи и может быть исПользовано в системах передачи информации с помощью дельта-модуляции.Цель изобретения - повышение надежности функционирования,На Фиг, 1 дана Функциональнаясхема дельта-кодера; на Фиг, 2временные диаграммы сигналов на входе 10и выходах элемента задержки.Дельта-кодер содержит компаратор1, триггер 2, первый регистр 3 сдви"га, первый-четвертый элементы И 4-7,Первый 8 и второй 9 элементы ИЛИ,реверсивный счетчик 10, кодопреобразователь 11, цифровой интегратор12, первый 13 и второй 14 дешифраторы, первый 15 и второй 16 элементыВЕ, делитель 17 частоты, элемент 18задержки и второй регистр 19 сдвига,роме того, дельта"кодер имеет информационный 20 и тактовый 21 входы ивыход 22,Кодопреобразователь 11 выполнен. 25на блоке постоянной памяти и блокемультиплексоров, подключающем к выходам кодопреобразователя 11 соответствующие выходы блока постояннойпамяти но сигналам на его управляющих 30вхоцах.Цифровой интегратор 12 выполнен наарифметико"логическом блоке, цифро"аналоговом преобразователе и буферномрегистре, выходы которого подключены.к входам цифроаналогового преобразо 35вателя и первым входам арифметико-логического блока, выходы которого соединены с информационными входами буФерного регистра, управляющий входкоторого является тактовым входомцифрового интегратора 12, вторые информационные и управляющий входыарифметико-логического блока и выходцифроаналогового преобразоватепя яв 45ляются соответственно информационнымии знаковым входами и выходом цифровогоинтегратора 12.Первый 13 и второй 14 дешифраторы служат для индикации достижения реверсивным счетчиком 10 соответственно максимального и минимального значений (величины шага квантования).Элемент 18 задержки по тактовым импульсам на входе (Фиг 2 а) Формирует на первом и втором выходахзадержание. последовательности импульсов фиг, 2 б и в). Первый и второй выхопы второго регистра 19 сдвига являются выходами его первого и последнего разрядов.Первый регистр 3 сдвига, элементы И 4 и 5 и элемент ИЛИ 8 представляет собой анализатор цифрового дельта-модулированного (ДМ) сигнала.Дельта кодер работает следующим образом.Цифровой ДИ-сигнал, образованный в результате сравнения входного 01) и аппроксимирующего Б сигналов компаратором 1 и дискретизации результатов сравнения триггером 2, последовательно заполняет разряды регистра 3 сдвига и анализирует элементы И 4 и 5, ИЛИ 8, Результаты анализа в виде цифрового сигнала записываются в регистр 19 сдвига и продвигаются в нем с приходом тактовых импульсов с входа 21. В каждом такте информация, записанная в регистр сдвига, через третий 7 и четвертый 8 элементыИ и второй элемент ИЛИ 9 воздействуют . на счетные входы реверсивного счетчика 10. Кроме того, на третьи входы элементов И 7 и 8 поступают сигналы с гервого и второго выходов элемента 13 задержки, .на вход которого поступают тактовые импульсы, Сигнал на первом выходе элемента 18 задержки задержан (сдвинут) относительно входного сигнала на некоторое произвольное время ь , а сигнал на втором выходе элемента 18 задержки - на время ь, причем с) ь но 6 ( 1 где Т - период тактовой частоты.1Таким образомв каждом такте ьа третьи входы элементов И 7 и 8 поочередно (с интервалом Ье = 2 - , ) воздействуют сканирующие импульсы, переключая сначала информационный бит из первого разряда регистра 19 сдвига на вход прямого счета реверсивного счетчика 10, а затем информационный бит из последнего разряда регистра 19 сдвига на вход обратного счета реверсивного счетчика 20. Состояние реверсивного счетчика 10, таким образом, постоянно отражает плотность (соотношение единичных и нулевых пачек) цифрового ДИ-сигнала на некотором Фрагменте (интервале), длительность которого определяется разрядностью регистра 6 сдвига. Длительность анализируемого Фрагмента целесообразно выбирать в пределах 3-10 мс, что при тактовых частотах 16-32 кГц позволяет выбирать разряд 3142932ность регистра,19 сдвига в пределах50-300, в зависимости от конкретнойтактовой частоты и требуемой инерционности адаптации, Кодовая комбинация на выходах реверсивного счетчика510 в дальнейшем используется дляформирования конкретного шага квантования двоичного числа, отображающего шаг квантования) на выходе кодопреобраэователя 11. Восстановлениеаппроксимирующего сигнала происходитпри помощи цифрового интегратора,Дешифраторы 13 и 14 в совокупностис первым 15 и вторым 16 элементами НЕ 15создают цепи блокировки "крайних"состояний реверсивного счетчика 10в режиме холостого хода и кратковременной перегрузки кодера для устранения сбоев, связанных с перегрузкойреверсивного счетчика 10.Делитель 17 частоты и второй элемент ИЛИ 9 используют для очисткиреверсивного счетчика 10 от результатов воздействия шумов и сбоев в цифровам ДМ-сигнале. Коэффициент деленияделителя 17 частоты целесообразно выбирать таким, чтобы импульсы, посту.пающие время от времени на вход обратного счета реверсивного счетчика10 (и уменьшающие двоичное число наего выходах), не оказывали определяющего влияния на величину шага квантования при передаче полезного сигнала, но позволяли счетчику 10 освобождаться от результатов сбоев (а ненакапливать их в течение всего времени работы). На практике коэффициентделения рекомендуется выбирать впределах 10-20, что конкретно зависитот "зашумленности" канала связи,Таким образом, благодаря способууправления величиной шага квантованияв цепи компандирования в дельта-кодере без дополнительного синхроканалаобеспечивается требуемая для нормальной работы подстройка (адаптация) шага квантования по параметрам передаваемого сигнала, Отпадает необходимость в дополнительном канале синхронизации, что приводит к повышениюстабильности работы за счет отсутствия принципиальной воэможности сбоев в синхронизации, сокращения аппаратуры сиихронизации и уменьшениядо минимума времени вхоядения в синхронизм на приемной стороне.Предлагаемый дельта-кодер (н частности, его цепь адаптации) име" бо 14лее простое выполнение, чем известный, что, в свою очередь, также обусловливает лучшую стабильность и надежность,Формула изобретенияДельта-кодер, содержащий компаратор, первый вход которого является . информационным входом дельта-кодера, выход компаратора соединен с информационным входом триггера, выход которого подключен к информационному входу первого регистра сдвига, знако" вому входу цифрового интегратора и является выходом дельта-кодера, прямые и инверсные выходы разрядов первого регистра сдвига соединены с входами соответственно первого и второго элементов И; выходы которых подключены к входам первого элемента ИЛИ, второй элемент ИЛИ, реверсивный счетчик, выходы которого подключены к входам кодопреобразователя, выходы которого соединены с информационнымиф входами цифрового интегратора, выход которого подключен к второму входу компаратора, первый и второй дешифраторы, выходы которых соединены через одноименные элементы НЕ с пер-выми входами соответственно третьего и четвертого элементов И, выход третьего,элемента И подключен к входу прямого счета реверсивного счетчика, тактовые входы триггера, первого регистра сдвига и цифрового интегра-. тора объединены и являются тактовым входом дельта-кодера, о т л и ч а ющ и й с я тем, что, с целью повышения надежности функционирования, в дельта-кодер введены второй регистр сдвига, элемент задержки и делитель частоты, вход которого объединен с входом элемента задержки и тактовым входом второго регистра сдвига и подключен к тактовому входу дельта- кодера, выход первого элемента ИЛИ соединен с информационным входом второго регистра сдвига, первый и второй выходы которого подключены к к вторым входам соответственно третьего и четвертого элементов И, первый и второй выходы элемента задержки соединены с третьими входами соответственно третьего и четвертого элементов И, выходы делителя частоты и четвертого элемента И подключены к первому и второму входам второго элемента ИЛИ, выход которого соединенСоставитель О. РевинсТехред Л.Олийнык Редактор О. Головач Корректор С, Чер Заказ 51,44/5 6 Тираж 929 ВНИИПИ Государственного комитета по делам изобретений и открытий 3035, Москва, Ж, Раушскаа наб/5 Производственно-полиграФическое предприятие, г. ужгород, ул. Проектная,5 1429321 6с входом обратного счета реверсивного с входами первого и второго дешифсчетчика, выходы которого соединены ратора.

СмотретьЗаявка

4196250, 17.02.1987

РИЖСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. А. Я. ПЕЛЬШЕ

КОТОВИЧ ГЛЕБ НИКОЛАЕВИЧ, КОМАРОВ КОНСТАНТИН СЕРГЕЕВИЧ

МПК / Метки

МПК: H03M 3/02

Метки: дельта-кодер

Опубликовано: 07.10.1988

Код ссылки

<a href="https://patents.su/4-1429321-delta-koder.html" target="_blank" rel="follow" title="База патентов СССР">Дельта-кодер</a>

Предыдущий патент: Преобразователь перемещения в код

Следующий патент: Преобразователь двоичного кода в код по модулю к

Случайный патент: Реакционный аппарат