Формирователь прямоугольных импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1411940

Авторы: Грейлихс, Яунозолиньш

Текст

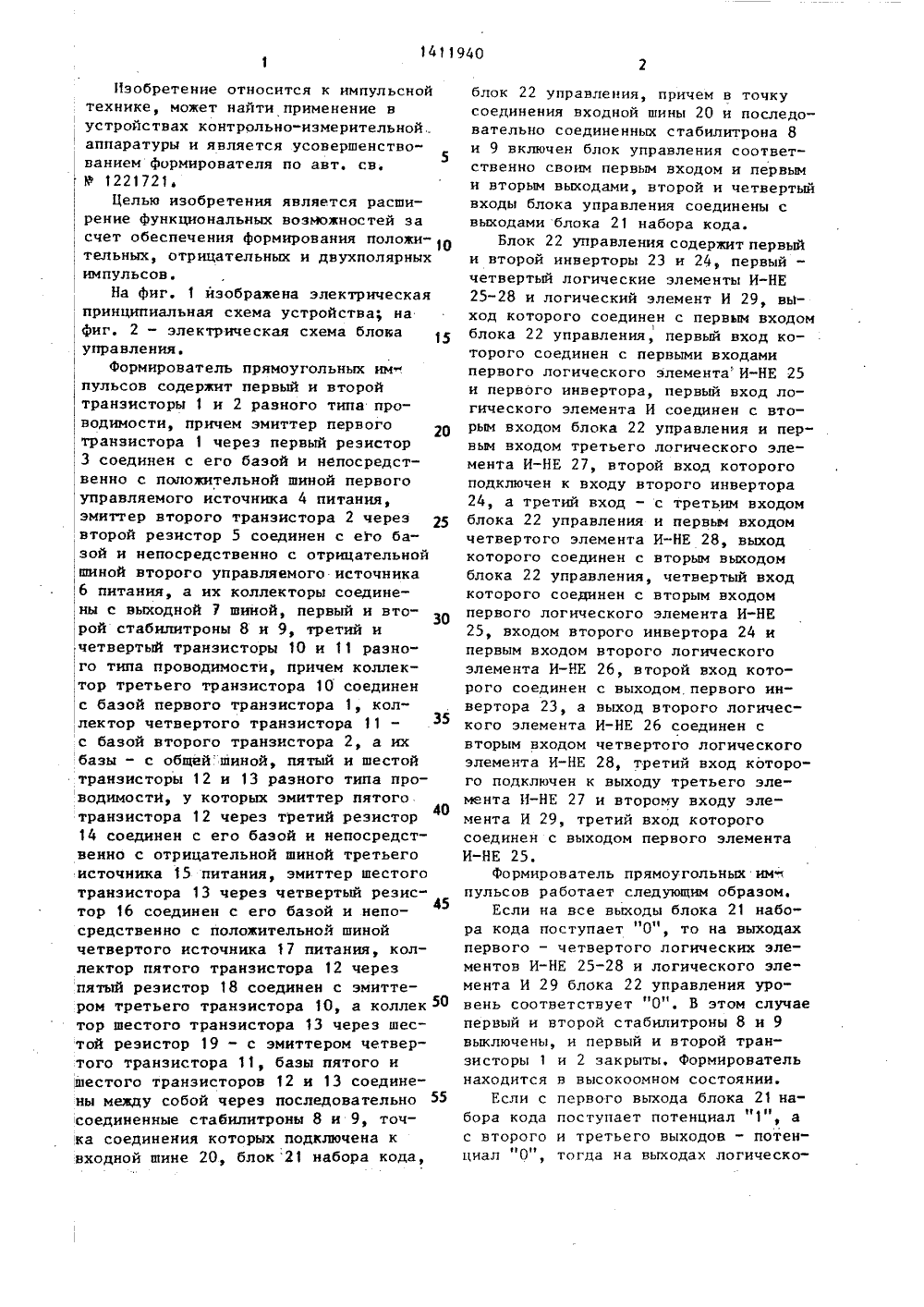

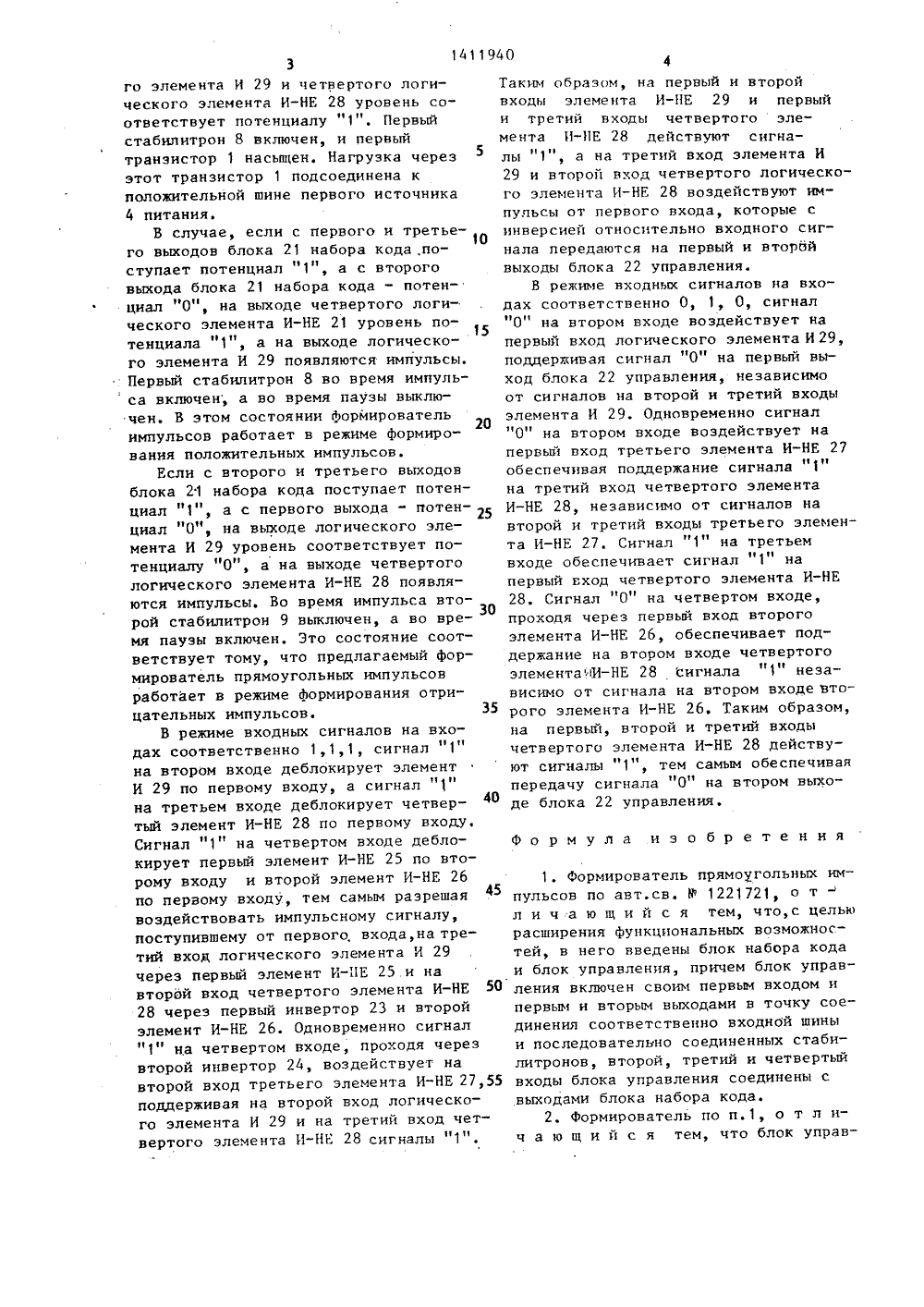

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК А 2 1411 5/О ИСАНИЕ ИЗОБРЕТЕНИ ЛЬСТВ ВТОРСКОМУ СВИ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИ(71) Рижское производственное объединение ВЭФ им. В,И. Ленина(56) Авторское свидетельство СССРВ 1221721, кл. Н 03 К 5/01, 1984.(54) ФОРМИРОВАТЕЛЬ ПРЯМОУГОЛЬНЫХ ИМПУЛЬСОВ(57) Изобретение может быть использовано в устройствах контрольно-иэмерительнои аппаратуры. Формировательпрямоугольных импульсов содержиттранзисторы 1, 2, 10-13 равного типапроводимости, резисторы 3, 5, 14,16,18, 19, управляемые источники 4, 6,15, 17 питания, стабилитроны 8, 9,блок 21 выбора кода и блок 22 управления, включающий два инвертора, четыре логических элемента И-НЕ и логический элемент И. Формирователь имеерасширенные функциональные воэможности за счет обеспечения формированияположительных, отрицательных и двухполярных импульсов. 1 з.п. ф-лы,2 ил.Изобретение относится к импульснойтехнике, может найти применение вустройствах контрольно-измерительной5 . аппаратуры и является усовершенство ваниемформирователя по авт, св.1 Ф 1221721Целью изобретения является расширение функциональных возможностей засчет обеспечения формирования положи- .1 Отельных, отрицательных и двухполярных ,импульсовНа фиг, 1 изображена электрическая принципиальная схема устройства; на,фиг. 2 - электрическая схема блока управления.Формирователь прямоугольных им пульсов содержит первый и второй транзисторы 1 и 2 разного типа проводимости, причем эмиттер первого транзистора 1 через первый резистор 3 соединен с его базой и непосредственно с положительной шиной первого управляемого источника 4 питания, эмиттер второго транзистора 2 через 25 второй резистор 5 соединен с его базой и непосредственно с отрицательной шиной второго управляемого источника 6 питания, а их коллекторы соединены с выходной 7 шиной, первый и второй стабилитроны 8 и 9, третий и ,четвертый транзисторы 10 и 11 разного типа проводимости, причем коллек,тор третьего транзистора 10 соединен с базой первого транзистора 1, коллектор четвертого транзистора 11 с базой второго транзистора 2, а их базы - с общейшиной, пятый и шестой транзисторы 12 и 13 разного типа про- водимостИ, у которых эмиттер пятого.40 транзистора 12 через третий резистор 14 соединен с его базой и непосредственно с отрицательной шиной третьего источника 15 питания, эмиттер шестого транзистора 13 через четвертый резис 45 тор 16 соединен с его базой и непосредственно с положительной шиной четвертого источника 17 питания, коллектор пятого транзистора 12 через пятый резистор 18 соединен с эмиттером третьего транзистора 10, а коллек50 тор шестого транзистора 13 через шестой резистор 19 - с эмиттером четвертого транзистора 11, базы пятого и ,шестого транзисторов 12 и 13 соединены между собой через последовательно 55 соединенные стабилитроны 8 и 9, точка соединения которых подключена к входной шине 20, блок 21 набора кода,блок 22 управления, причем в точку соединения входной шины 20 и последовательно соединенных стабилитрона 8 и 9 включен блок управления соответственно своим первым входом и первым и вторым выходами, второй и четвертый входы блока управления соединены с выходами блока 21 набора кода.Блок 22 управления содержит первый и второй инверторы 23 и 24, первый - четвертый логические элементы И-НЕ 25-28 и логический элемент И 29, выход которого соединен с первым входом блока 22 управления, первый вход которого соединен с первыми входами первого логического элемента И-НЕ 25 и первого инвертора, первый вход логического элемента И соединен с вторым входом блока 22 управления и первым входом третьего логического элемента И-НЕ 27, второй вход которого подключен к входу второго инвертора 24, а третий вход - с третьим входом блока 22 управления и первым входом четвертого элемента И-НЕ 28, выход которого соединен с вторым выходом блока 22 управления, четвертый вход которого соединен с вторым входом первого логического элемента И-НЕ 25, входом второго инвертора 24 и первым входом второго логического элемента И-НЕ 26, второй вход которого соединен с выходом первого инвертора 23, а выход второго логического элемента И-НЕ 26 соединен с вторым входом четвертого логического элемента И-НЕ 28, третий вход которого подключен к выходу третьего элемента И-НЕ 27 и второму входу элемента И 29, третий вход которого соединен с выходом первого элемента И-НЕ 25формирователь прямоугольных им+ пульсов работает следующим образом.Если на все выходы блока 21 набора кода поступает "О", то на выходах первого - четвертого логических элементов И-НЕ 25-28 и логического эле" мента И 29 блока 22 управления уровень соответствует "О". В этом случае первый и второй стабилитроны 8 и 9 выключены, и первый и второй транзисторы 1 и 2 закрыты, Формирователь находится в высокоомном состоянии,Если с первого выхода блока 21 на 1 1 бора кода поступает потенциал 1 , а с второго и третьего выходов - потенциал "О, тогда на выходах логическоТаким образом, на первый и второйвходы элемента И-НЕ 29 и первыйи третий входы четвертого элемента И-НЕ 28 действуют сигналы "1, а на третий вход элемента И29 и второй вход четвертого логического элемента И-НЕ 28 воздействуют импульсы от первого входа, которые синверсией относительно входного сигнала передаются на первый и второйвыходы блока 22 управления,В режиме входных сигналов на входах соответственно О, 1, О, сигнал"О" на втором входе воздействует напервый вход логического элемента И 29,поддерживая сигнал О" на первый выход блока 22 управления, независимоот сигналов на второй и третий входыэлемента И 29Одновременно сигнал"О" на втором входе воздействует напервый вход третьего элемента И-НЕ 27обеспечивая поддержание сигнала "1"на третий вход четвертого элементаИ-НЕ 28, независимо от сигналов навторой и третий входы третьего элемента И - НЕ 27. Сигнал "1" на третьемвходе обеспечивает сигнал "1" напервый вход четвертого элемента И-НЕ28. Сигнал "О" на четвертом входе,проходя через первый вход второгоэлемента И-НЕ 26, обеспечивает поддержание на втором входе четвертогоэлемента"И - НЕ 28 сигнала "1" независимо от сигнала на втором входе второго элемента И-НЕ 26, Таким образом,на первый, второй и третий входычетвертого элемента И-НЕ 28 действуют сигналы "1", тем самым обеспечиваяпередачу сигнала О на втором выходе блока 22 управления. Формула изобретения 1. Формирователь прямоугольных импульсов по авт.св. И 1221721, о т л и ч а ю щ и й с я тем, что,с целью расширения функциональных возможностей, в него введены блок набора кода и блок управления, причем блок управления включен своим первым входом и первым и вторым выходами в точку соединения соответственно входной шины и последовательно соединенных стабилитронов, второй, третий и четвертый входы блока управления соединены с выходами блока набора кода.2. Формирователь по п.1, о т л ич а ю щ и й с я тем, что блок управ 1411940 го элемента И 29 и четвертого логического элемента И-НЕ 28 уровень соответствует потенциалу "1". Первый стабилитрон 8 включен, и первый транзистор 1 насьшен. Нагрузка через этот транзистор 1 подсоединена к положительной шине первого источника 4 питания.В случае, если с первого и третьего выходов блока 21 набора кода,поступает потенциал "1", а с второго выхода блока 21 набора кода - потенциал "О", на выходе четвертого логического элемента И-НЕ 21 уровень пове н15 тенциала 1 , а на выходе логического элемента И 29 появляются импульсы. Первый стабилитрон 8 во время импуль са включен, а во время паузы выключен. В этом состоянии формирователь импульсов работает в режиме формирования положительных импульсов.Если с второго и третьего выходов блока 21 набора кода поступает потенциал "1" а с первого выхода " потенЭ 25 циал "О", на выходе логического элемента И 29 уровень соответствует потенциалу "О", а на выходе четвертого логического элемента И-НЕ 28 появляются импульсы. Во время импульса второй стабилитрон 9 выключен, а во вре 30 мя паузы включен, Это состояние соответствует тому, что предлагаемый формирователь прямоугольных импульсов работает в режиме формирования отрицательных импульсов, 35В режиме входных сигналов на входах соответственно 1,1,1, сигнал "1" на втором входе деблокирует элемент И 29 по первому входу, а сигнал на третьем входе деблокирует четвертый элемент И-НЕ 28 по первому входу, Сигнал "1" на четвертом входе деблокирует первый элемент И-НЕ 25 по второму входу и второй элемент И-НЕ 26 по первому входу, тем самым разрешая 45 воздействовать импульсному сигналу, поступившему от первого, входа,на третий вход логического элемента И 29 через первый элемент И-ПЕ 25 и на второй вход четвертого элемента И-НЕ 50 28 через первый инвертор 23 и второй элемент И-НЕ 26. Одновременно сигнал "1" на четвертом входе, проходя через второй инвертор 24, воздействует на второй вход третьего элемента И-НЕ 27,55 поддерживая на второй вход логического элемента И 29 и на третий вход четвертого элемента И-НЕ 28 сигналы "1".1411940 Составитель ЧижиковРедактор Н. Гунько Техред М,Дидык Корректор М, П Подписноеного комитета СССРений и открытийРаушская наб., д. 4/5 8 Т каз 3671/ ИИПИ Государств по делам изобр 5, Москва, Ж113 лиграфическое предприятие, г, Ужгород, ул. Проектная юноПроиэвод ления содержит первый и второй инверторы, первьп, второй, треий и четвертый логические элементы И-НЕ илогический элемент И, выход которого соединен с первым входом блока управления, первый вход которого соединен с первыми входами первого логического элемента и первого инвертора,первый вход логического элемента И,соединен с вторым входом блока управления и первым входом третьего логического элемента И-НЕ, второй входкоторого подключен к выходу второгоинвертора, а третий вход - к третьему 1 бвходу блока управления и первому вхо 6ду четвертого элемента И-НЕ, выход которо го соединен с вторым входом блока управления, четвертый вход которого соединен с вторым входом первого логического элемента И-НЕ, входом второго инвертора и первым входом второго логического элемента И-НЕ второй вход которого соединен с выходом первого инвертора, а выход второ" го логического элемента И-НЕ соединен с вторым входом четвертого логического элемента И-НЕ, третий вход которого подключен к выходу третьего элемента И-НЕ и второму входу элемента И, третий вход которого соединен с выходом первого элемента И-НЕ,

СмотретьЗаявка

4048343, 03.04.1986

РИЖСКОЕ ПРОИЗВОДСТВЕННОЕ ОБЪЕДИНЕНИЕ ВЭФ ИМ. В. И. ЛЕНИНА

ЯУНОЗОЛИНЬШ ЯНИС КАРЛОВИЧ, ГРЕЙЛИХС ТАЛИС ХАРИЕВИЧ

МПК / Метки

МПК: H03K 5/01

Метки: импульсов, прямоугольных, формирователь

Опубликовано: 23.07.1988

Код ссылки

<a href="https://patents.su/4-1411940-formirovatel-pryamougolnykh-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь прямоугольных импульсов</a>

Предыдущий патент: Имитатор провалов напряжения сети

Следующий патент: Устройство воспроизведения прямоугольных импульсов

Случайный патент: Смеситель-реактор