Цифровое устройство для управления ведомым сетью преобразователем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

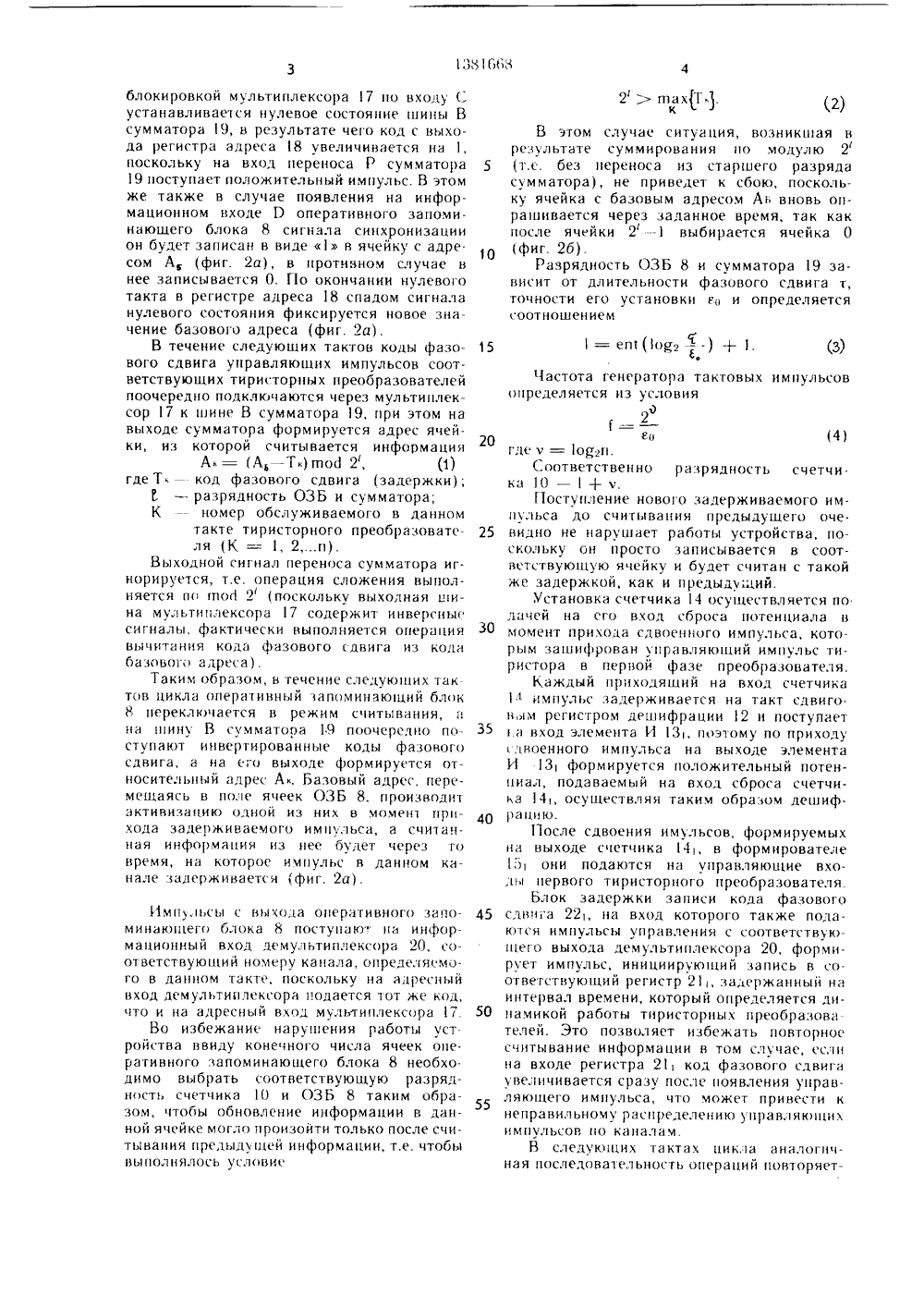

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК А 119 ВСЕ(т)1 О"-11" Я 02 М 7 13,.", 13 ЬЫг Р 1"; ОПИСАНИЕ ИЭОБРЕТЕНИ ВИДЕТЕЛЬСТ ВТОРСК нституттин, В. И. ШаОСУДАРСТВЕННЫИ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(54) ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ВЕДОМЫМ СЕТЪЮ ПРЕОБРАЗОВАТЕЛЕММ(57) Изобретение относится к электротехнике и может быть использовано в статических преобразователях. Цель изобретения - улучшение динамических характеристик и повышение надежности. За счет введения в устройство для управления преобразователем фиксатора нулевого значения, регистров кодов фазового сдвига 21 - 21, мультиплексора кодов фазового сдвига 17, регистра базового адреса 18, сумматора 19 и блоков задержки записи кода фазового сдвига 22 вобеспечивается надежная работа устройства в динамических режимах, когда фазовая задержка импульсов значительно изменяется в течение одного гериода частоты сети. 2 ил.4. 45 50 55 Изобрени относится к электротхике, д имеццц к темам управления тиристорными преобразцдтлями, и может найти прим(ц 1)п В кзчесгблока управ)ения прецбрдзовдтелй, ведомых сетью.1 ель изобретения улучшение динами ческих характеристик и повышение надежности рабцгы лтрц 3 тд.Нд фи. 1 представлена структурная схема устрцйстд: цд фиг. 2пцл( я и ек опратиццгц (зпцмпцдк)щего блока Х 1 РоиТЦ . 0,РКИТ ПЦ ЧИС. У фДЗ ПИ сК)- )и сет фильГры 1,1 1 п, ВхОды которых ПР(.,Цздпс 3(.Ц 1 Д,53 ЦЦДКЛ ТОЧЕНИЯ И фзД М сетевого цапряжни, з вы соды пцфазнц подклкиеп к входдл пуль-оргацо 2,12 ш, выходами пцдклк)чецных и информационным входам мульгиц,нксцрд 3, к выходу кгорого пцдклнчны жлу пии мул ьгивибрд гцр 4 и первый Вход эм(гз ИЛИ 5, выход ждуцегц мулыиибр; тцрд 4 подключен к входу счетчика щ)м( р;( фазы цреобрд 50( Гел 3 5, выход которого и.к,К(ц к адресно;нице мультиплексора 5, сдвигоый реиср щпф рации 7, ход копроо подключен к Выхц дл Ну.Ь-црдцс П( рОИ фд )Ы 2, а ВЫХцд К ВТО рому вхцдх э.Мец Гз ,И 5, Вы.хцл к)п; рого пцдклкчен к Нфцрмдционнцлу ходу опера тивцг(:5 д по м и цз к щего блока (, г( ц Г)дтор Гзктс) ых ц м 3) 1 ьсц 9, ы ход кц 1 црцГО 3 ОДк, 303 ц 3, 1 х)1 б( 1 к 3 ццс ) Г 1(ц 01131 цч 3 к 11,( 3б.цкд 8 и хц,у с нчик) Омпз Гирц(";(ц р(цбрс 1 50 с( 1, 11), пц пслу(црц 1 лы (ьцрлрц); пия Ьхц,сЬХ Пс 31 .Ь 01 1, С.1 рж 33 И(.с ., жып с;,;. ( н33 р .)иНфрсцц2, ЭЛсп П Ы1( ЧИК ПОМЕрс 3)рцтциц ) Рм Р 11 ь (д 50 цпх ил 1 УГЬ ОЬ 1, 3 Х),( (,115111,)010 Р( ("1 Рс) Д( ЦИфРЗПИИ- 01) 3 ссД 1 сп ЦВТ( Ры ) 13 Хсс 1 Мп ЛЛ(П. И 1и (1 тцыл ХцдцМ счетчик; ц р;3( Гцрз 4 и цбр; (- Вхцс УЗ,1) с(ЛЦ)01;и;1 3,)ХОДЦЫХ ИМПХ,11, сцв 11, ь х л п(010 регистр;3 децифрзцип 2,к,ц)3(с 13 рпым Влц,(цм э.е. м(НГ)1 И ) З 3)ьх(. Ь)срцц сц(диц(ц с Вхц. дцм сброс;1 с чик;3 ц )мс р;1 гиритора 14, Вы хо з кц00 го с(н (и ц; п с входцл", фцрм иРц;, ,1313311)х,лпл ьсцв 5. УСТРцисВц Гцц),с,п.ьц (цдбжено фксдтцрцм Гн р 50 ц зцд)ци 6, му.ыилексцрцм кцдц фд,н)цгц (,531, 1), р(гистрцм д,ц). з 18, суммзтцн с 19, мхл,гцп ексцрцм 20. и чи- .,) 3 И 533( ГЦ 015 Р(ГИС Г)сМИ КОДОВ (Рс 50503 Ц СДВИГсП (,ЦЛ)1 М) .с 1,(. РЖКИ:5 с 1 ИСИ КЦ да 22, при " ьч)1 х 1 с ццкд )мрд ги ристорнцО ис ) ,. );1(с ели,ц ( ) ц ДОМ (1)иксд 1 цр 3.1(15) 3 0,533;1(3 И 51 1 ц р(.сн ми пис)с 3,1 лх,ьтц)3.3(к(.цр 20 и лх Л 1,- 15(3,3( ксцрд фд.с и) ц с иа 1. 333(рл:ЦИОЦ ,Е ХОДЫ лцхц (: Ц СНДИЦ(НЫ 5 ХЦ. дд Л ц 5)ГИ 1;ц 3 Кцдц.3 )цо о (, И:.3 2 с, Ьхц.11 КОТцрьХ Прсс) ПсВ 33)1,1,1 110 К,)К).ЦС 31;с И 10)ПКХ КЦДЦфз )ОНОГО ДИ, Ы 10 15 О 5 Я 0 с 5 хц фиксатора нулИ)10 значения соединен с Входом блокировки мультиплексора кодов фззцого сдвига, с входом записи регист. ра адреса 18, входом разрешения записи оперативного запоминаюпего блока 8 и входом переноса сумматора9, вход сложения которого соединен с ыходом мультиплексора кодов фазового сдвига 17, а вход -- с адрецой шиной оперативного запоминаюце блокз 8 и с входной шиной регисгра адреса 18, выход оперативного запоминзкцего блока 8 соединен с информзци(иным входом дмультиплексора 20 и выходов которого и) ч 3,у тиристорных преобрдз(взтелей соединены соответственно с Входами узлов формирования выходных им пульсов 11, а Вход каждого узла формирцдия выходных цмульсц 11 обьединен с вход м соцтветгующего блока задержки записи кода фазц 030дигд 22, выходы которыхццтнетственнц подклкцены к управляюцп ч хцдал реги ров кодов фазового Ви, д - 21.Усрой ство раб( 1 зе г )дуюпим образом.НдцряжЕНИИ фдд ЕИ ццс)двтгя На ВХОД- ны фильтры 1, 1.и, з затем на нуль-орзцы 2 1 2.ш, фикрукщие положительными пмпхльсзми цд (Вцих выходах момент перхц:ш через у)ь напряжения В соотЕтс 115 К) 1,И фд.5.;)Ти ИМИ Л ЬСЫ ПостцдЮТ 01)де( 3 ой нцсл,цдт,льно ти ца ин- (0 И;3 П(нНЫЕ ХЛ 1,тпц.КРД 3, а ЦД ур, цющХц 3 (ступает с Выхода Сц),лд Нс)Л(ср; ф: (ы 3) КОД, цс 13(ЧИ Д)3(ИП ЦЦ,1 КЛК) 3 ЦПЦНОС ЦЗ ПнфОРМД- и 1 33 ц,1 Х ВХО,3)15 1.р( ( 1)1.ОД М)с.3 ЬТ И ц:3(К лр 3 8 к жл),щ( м) му,1 тивибратоу 4 ( р( ь. и л здд(. р,+к 3 т 5. Илпульс с выхода ж,("Со ЛуЬ 13,иб); Гцрс 1 с 1 ПЕ)рКЛЮЧИТ ЧР. р,5 рмя е3 чк 6, цри этол мульгпп.) ксцр 8 переключится ца ожидание им:) 33) с ц С.С)Лс) КП 0 30 ццр 5 ДКу Нулп-Ордц пц,н нч ц проц с Нторяется. 1,ким образом, цд цдццм из Входоь эл- лц;3 ИЛИ 5 фцрмируетс одноканальная пцс,(,1 Од 1 ел ьнцсг сиц х роци)ирую щих импулыц. Импульс с Выхода первого нульорИц. 2 задержид(тя сдвиговым регистрцм 7 цд )дин такт и 1 ос гуает цд Второй Вхз эгм(ггз ИЛИ , цри этом нд егц выходе о,ц(5 кзцдной по(лдовзтельности иму.ь(цв первый из группы является сдвоенным, ч)Г) необходимо в дальнейшем для (цр,деления, к какой из фаз принадлежит КджДЫй ИМУ.)Ы.Рдбгчии цикл усрцйства цстоит из и+1 Г;кто енераторз .актовых импульсов 9, опр. дел яющих сцсцяцис выхода счетчика померз тиристорщц 0 пр(образователя 10, з,е( ь ичисло управляемых тиристоров преобразователей. 11 рц нулевом состоянии фик.пруемый фцксдтцрцм нулевого значения 36 ццс рдтнццй ЗЗПОМИдЮщнй 6 ЛОК 8 ВКЛЮ 133) ся режим зпси и одновременноблокировкой мультиплексора 17 по входу С устанавливается нулевое состояние шины В сумматора 19, в результате чего код с выхода регистра адреса 18 увеличивается на 1, поскольку на вход переноса Р сумматора 19 поступает положительный импульс. В этом же также в случае появления на информационном входе Р оперативного запоминающего блока 8 сигнала синхронизации он будет записан в виде 1 в ячейку с адресом А (фиг. 2 а), в противном случае в нее записывается О. По оконцании нулевого такта в регистре адреса 18 спадом сигнала нулевого состояния фиксируется новое значение базового адреса (фиг. 2 а).В течение следующих тактов коды фазового сдвига управляюших импульсов соответствующих тири торных преобразователей поочередно подключаются через мультиплексор 17 к шине В сумматора 19, при этом на выходе сумматора формируется адрес ячейки, из которой считывается информацияА = (А, - Т) гпос 1 2, (1) где Т. - код фазового сдвига (задержки);- разрядность ОЗБ и сумматора;К - номер обслуживаемого в данномтакте тиристорного преобразователя (К =- 1, 2,п).Выходной сигнал переноса сумматора игнорируется, т.е. операция сложения выполняется по спос 2 (поскольку выходная шина мультиплексора 17 содержит инверсньн сигналы, фактически выполняется операция вычитания кода фазового сдвига из кода базового адреса).Таким образом, в течение следукэщих тактов цикла оперативный запоминающий блок 8 переключается в режим считывания, а на шину В сумматооа 19 поочередно поступают инвертированные коды фазового сдвига, а на его выходе формируется относительный адрес А. Базовый адрес, перемешаясь в поле ячеек ОЗБ 8, производит активизацию одной из них в моменз прихода задерживаемого имп,льса, а считачная информация из нее будет через то время, на которое импульс в данном канале задерживается (фиг. 2 а). Импульсы с выхода операгивного запоминающего блока 8 поступают на информационный вход демультиплексора 20, соответствующий номеру канала, определя мого в данном такте, поскольку на адресный вход демультиплексора подается тот же код, что и на адресный вход мультиплексора 17Во избежание нарушения работы устройства ввиду конечного числа яцеек опе. ративного запоминающего блока 8 необхо. димо выбрать соответствующую разрядность сцетчика 1 О и ОЗБ 8 таким образом, чтобы обновление информации в данной ячейке могло произойти точько после считывания предыдущей информации, т.е. чтобы выполнялось условие(2) 1= еп 1(1 о( - -) + .6,15 Частота генератора тактовых импульсовопределяется из условия2Ео (4) 20где= оди.Соответственно разрядность счетчика 10 - 1 + х.Поступление нового задерживаемого импульса до считывания предыдущего оче видно не нарушает работы устройства, поскольку он просто записывается в соотвстствующую ячейку и будет считан с такой же задержкой, как и предыдугций.Установка счетчика 14 осуществляется подачей на его вход сброса потенциала в момент прихода сдвоенного импульса, которым зашифрован управляюгций импульс тиристора в первой фазе преобразователя.Каждый приходягций на вход счетчика1 з импульс задерживается на такт сдвигов,м регистром дешифрации 12 и поступаета вход элемента И 13 ь поэзому по приходудвоенного импульса на выходе элемента И 13 формируется положительный потенциал, подаваемый на вход сброса счетчика 14 ь осуществляя таким образом дешиф рациюПосле сдвоения имульсов, формируемыхна выходе счетчика 14, в формирователе д они подаются на управляющие входы первого тиристорного преобразователя.Блок задержки записи кода фазового 45 сдвига 22 ь на вход которого также подаются импульсы управления с соответствующего выхода демультиплексора 20, формирует импульс, инициирующий запись в соответствующий регистр 21, задержанный на интервал времени, который определяется ди намикой работы тиристорных преобразователей. Это позволяет избежать повторное считывание информации в том случае, если на входе регистра 21 код фазового сдвига увеличивается сразу после появления управляющего импульса, цто может принести к неправильному распределению управлякщих импульсов по каналам.В следующих тактах цикла аналогичная последовательность операций повторяетВ этом слуцае ситуация, возникшая врезул ьтате суммирования по модулю 2 5 (т.е. без переноса из старшего разрядасумматора), не приведет к сбою, поскольку ячейка с базовым адресом Ав вновь опрашивается через заданное время, так как после ячейки 2 1 выбирается ячейка О 1 О (фиг. 2 б).Разрядность ОЗБ 8 и сумматора 19 зависит от длительности фазового сдвига т, точности его установки е 0 и определяется соотношением1381668 формула изобретения лрада ениео ещенннюй са адреса фиг сБ 11111111 Заказ 8 о 7,5;1 111 ииаволетвенно.полиграфическое и ся по отношеникт к импульсам управления остальных тиристорных преобразователей. Таким образом, применение в данном устройстве по сравнению с известными новых элементов, а именно фиксатора нулевого значения, регистров кодов фазового сдвига 21 21., мультиплексора кодов фазового сдвига 17, регистра базового адреса 18, сумматора 19 и блоков задержки записи кода фазового сдвига 22- 22, позволяет повысить надежность работы цифрового устройства в динамических режимах, когда фазовая задержка импульсов значительно изменяется н течение одного периода частоты сети. Цифровое устройство для управления ведомым сетью преобразователем, содержащее по числу фаз питающей сети фильтры, входы которых предназначены для подключения к фазам сетевого напряжения, выходы пофазпо подключены к входам нуль- органов, выходами подключенных к инфор. мационным входам мультиплексора, к выхо ду которого подкл кцены ждущий мульти вибратор и первый вход элемента ИЛИ, выход ждущего мультивибратора подключен к входу счетчика номера фазы преобразователя, выход которого подключен к адресной шине мультиплексора, слвиговый регистр шифрации, нхол которого подключен к вы. холу нуль-ор ана первой фазы, выход - к нто рому входу элемента ИЛИ, выход которого подключен к информационному входу г перативного запоминающего блока, генера.1,р тактовых импульсон, выход которого под. клюцен к входу выборки оперативного за. помина ющего блока и к входу счетчика но. мера тиристорного преобразователя по числу тиристорных преобразователей, узлы формирования выходных импульсов, каждый из которых содержит сднигоный регистр дешифрации, э, емент И, счетчик номера тиристора и формирователь сдвоенных импульсов, вход 5 10 15 20 25 30 35 40 сдвигового регистра дешифрации объединен с вторым входом элемента И и счетным входом счетчика номера тиристора и об. разует вход узла формирования выходных импульсов, выход сдвигового регистра дешиф рации соединен с первым входом элемента И, выход которого соединен с входом сброса счетчика номера тиристора, выход которого соединен с входом формирователя сдвоенных импульсов, отличающееся тем, что, с целью улучшения надежности работы, оно снабжено фиксатором нулевого значения, мультиплексором кодов фазового сдвига, регистром адреса, сумматором, демультиплексором, по числу тиристорных преобразователей регистрами кодов фазового сдвига и блоками задержки записи кода, причем выход счетчика номера тиристорного преобразователя соединен с входом фиксатора нулевого значения и адресными шинами демультиплексора и мультиплексора фазо ного сдвига, информационные входы которого соединены с выходами регистров кодов фазового сдвига, входы которых предназначены для подключения к источнику кодов фазового сдвига, выход фиксатора первого значения соединен с входом блокировки мультиплексора кодов фазового сдвига, с входом записи регистра адреса, с входом разрешения записи оперативного запо. минакщего блока и с входом переноса сумматоравход сложения которого соединен с выходом мультиплексора кодов фазового сдвига, а выход с адресной шиной оперативного запоминающего блока и с входной шиной регистра адреса, выход оперативного запоминающего блока соединен с ин. формационным входом демультиплексора, п выхолов которого по числу тиристорных преобразователей соединены соответственно с входами узлов формирования входных импульсов, а вход каждого узла формирования выходных импульсов объединен с входом соответствующего блока задержки записи кода фазового сдвига, выходы которых соответственно подключены к управляющим входам регистров кодов фазового сдвига. Тираж 665 11 одп и оное приятие, г. Ужгорось 1 п.роектная,

СмотретьЗаявка

4036688, 17.03.1986

УФИМСКИЙ АВИАЦИОННЫЙ ИНСТИТУТ ИМ. СЕРГО ОРДЖОНИКИДЗЕ

РЫЖИКОВ ОЛЕГ ЛЕОНИДОВИЧ, НИКИТИН АЛЕКСАНДР ВЛАДИМИРОВИЧ, ШАРАБЫРОВ ВИКТОР ИВАНОВИЧ, КАРПОВ ВЛАДИМИР ЮРЬЕВИЧ

МПК / Метки

МПК: H02M 7/00

Метки: ведомым, преобразователем, сетью, цифровое

Опубликовано: 15.03.1988

Код ссылки

<a href="https://patents.su/4-1381668-cifrovoe-ustrojjstvo-dlya-upravleniya-vedomym-setyu-preobrazovatelem.html" target="_blank" rel="follow" title="База патентов СССР">Цифровое устройство для управления ведомым сетью преобразователем</a>

Предыдущий патент: Преобразователь частоты с широтно-импульсной модуляцией

Следующий патент: Устройство для управления вентильным преобразователем

Случайный патент: Бункер хлопкоуборочной машины