Генератор возвратных последовательностей -го порядка

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

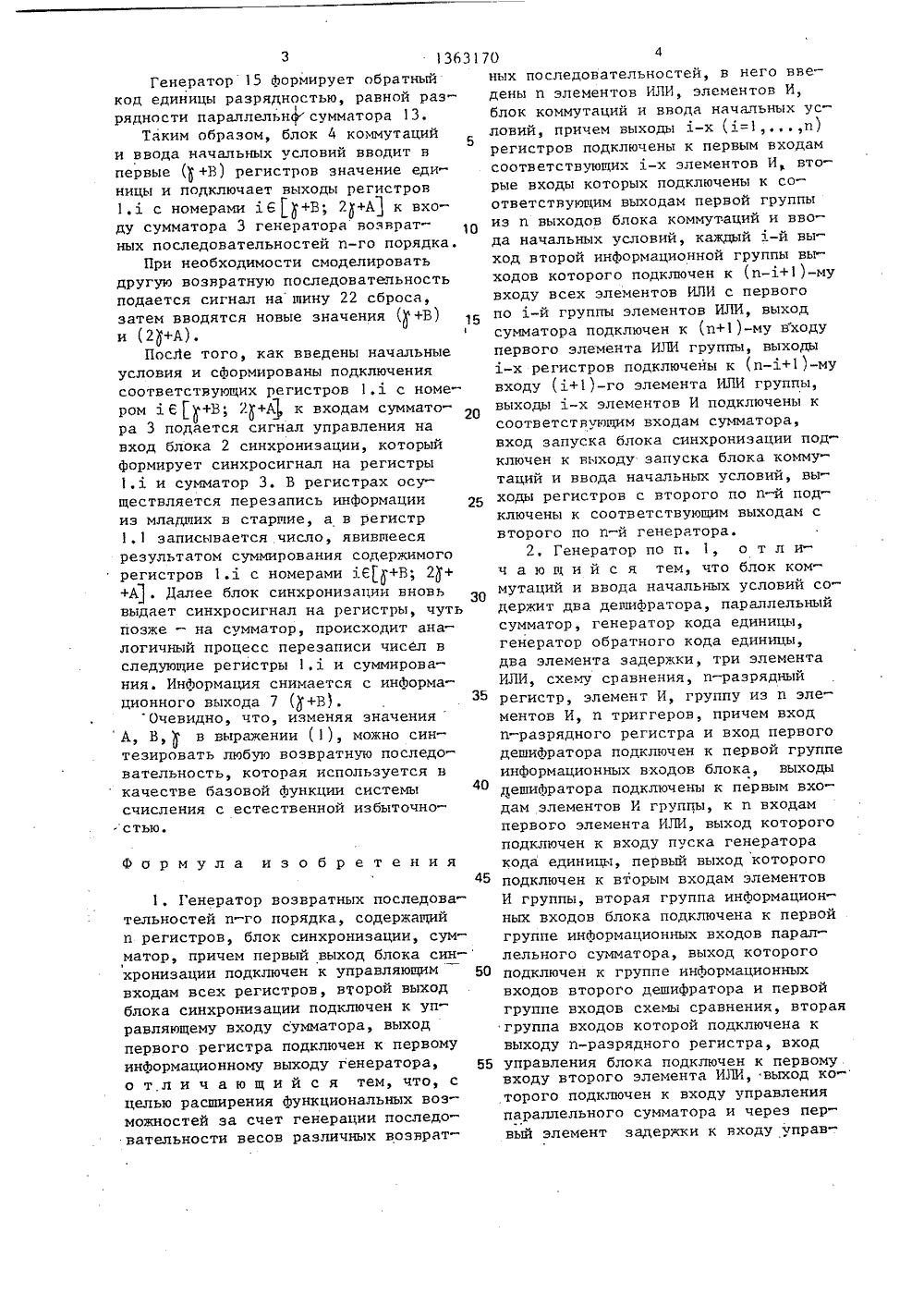

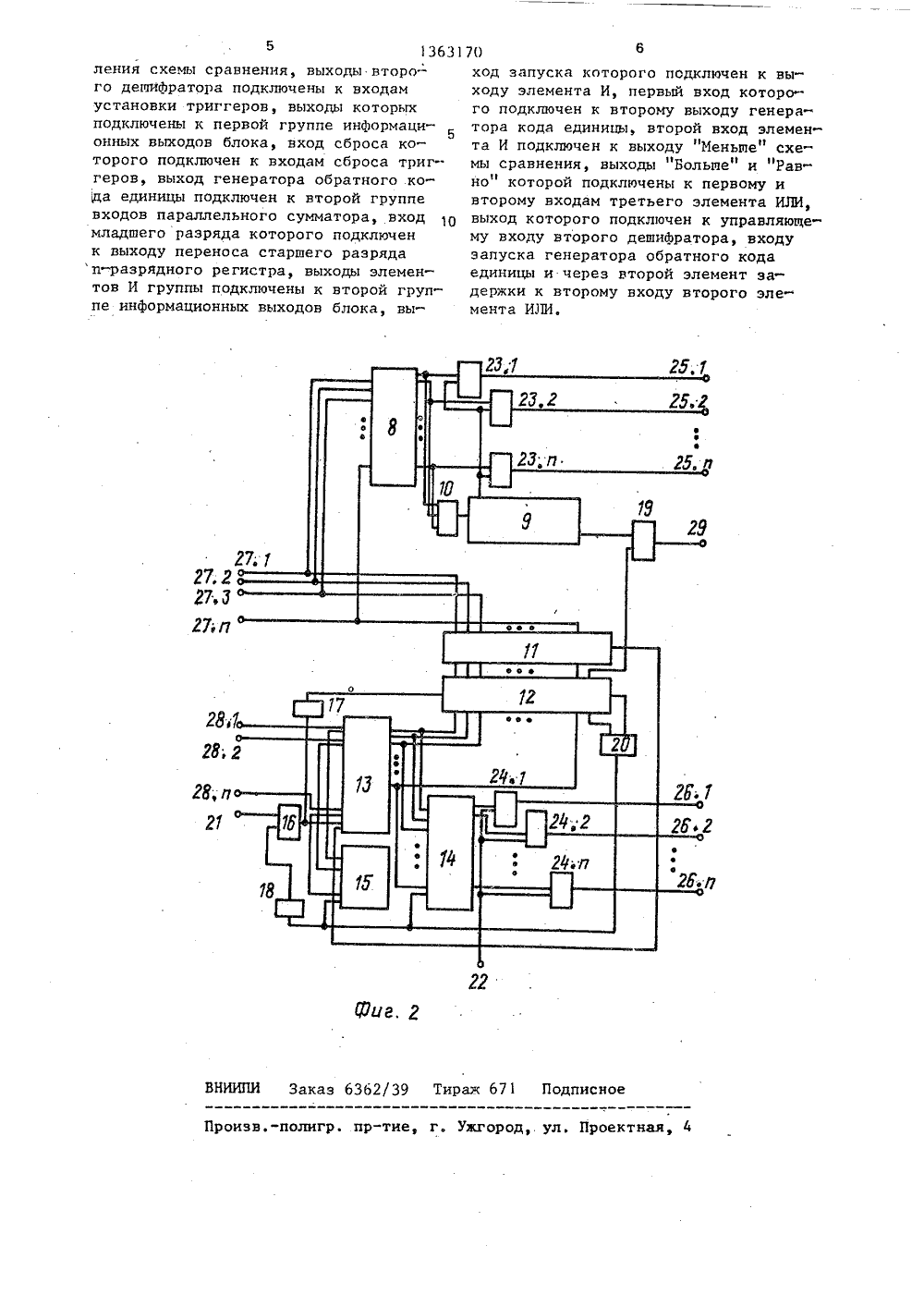

О 8 ЕТСНИХИСТИЧЕСНИ 3631 19) 59 4 8 ОЬ Р 1/02 НИЯ стей последователь для генерир ени нос изоб е к иональных возможрации весов раз ин лич ей(54) ГЕНЕРА ТЕЛЬНОСТЕЙ (57) Изобр лительной й и элеменОСУДАРСТ 8 ЕННЫЙ НОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИ ОПИСАНИЕ ИЗОБРЕ АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(53) 681.325(088.8) кое свидетельство ССС кл. О 06 У 1/02, 1983 е свидетельство СССР л. О 06 Р 1/02, 1979. ТОР ВОЗВРАТНЫХ ПОСЛЕДОВАи-ГО ПОРЯДКАтение относится к вычисехнике и предназначено весов возвратных последовательностеи различного поряд а, Цель р расширение Аункцтей за счет гененых возвратных последовательнос Генератор содержит и резиблок 2 синхронизации, сублок 4 коммутаций и вводусловий, и элементов И,ИЛИ. Поставленная цель дза счет введения блока 4и ввода начальных условийтов И, и элементов ИЛИ.2 ил.1 13631Изобретение относится к вычислительной технике и может быть исполь- зовано для моделирования рядов различ" ных возвратных последовательностей,Выражение (1) позволяет моделировать унарную систему счисления и огромный класс возвратных последовательностей.10О при пО; Б (п) ,1 при ОпД; (1) 1 АА8( и- -,1 ) при и ру,ВФЬПри В=О, Асе, В =1 выражение (1) задает классическую двоичную систему счисления.Цель изобретения - расширение функциональных возможностей за счет способности генерировать последовательности весов различных возвратных 20 последовательностей,Сущность изобретения состоит в реализации выражения (1),На фиг, 1 изображен генератор возвратных последовательностей п-го порядка; на фиг. 2 - блок коммутаций и ввода начальных условий.Генератор содержит и разрядных регистров 1.1; 1,21.п (где п=1-о:В), блок 2 синхронизации, сумматор 3, блокЗ 0 4 коммутаций и ввода начальных ус ловий, п элементов И 5.1, 5.,25.п, и элементов ИЛИ 6.1,6.26,п, информационные выходы 7.1, 7.27,п.Блок 4 коммутаций и ввода начальныхз 5условий содержит первый дешифратор 8, генератор 9 кода единицы, первый элемент ИЛИ 10, и-разрядный регистр 11, схему 12 сравнения, параллельный сумматор 13, второй дешифратор 14, гене ратор 15 обратного кода единицы, второй, элемент ИЛИ 16, два элемента 17 и 18 задержки, элемент И 19, третий элемент 20, вход 21 управления, вход 22 сброса, группу из и элементов И 45 23123,п, и триггеров 24.124.п, первую группу п выходов 25.125.п, вторую группу п выходов 26.126.п, первую группу и входов 27.127.п, вторую группу и входов 28.128.п, 50выход 29. Блок 4 коммутаций и ввода начальных условий служит для ввода начальных условий в х первых регистров, а также подключения к сумматору выходов соответствующих регистров 1-пв в зависимости от принятых для данного случая А, В,70 2Для того, чтОбы рассмотреть работугенератора возвратных последовательностей п-го порядка, проанализируемсначала работу блока коммутаций иввода начальных условий,Блок коммутаций и ввода начальныхусловий работает следующим образом.На входные шины 27.1, 27.227.ппоступает значение (+В) в двоичнойклассической системе счисления, записывается в регистр 11 и поступаетна входы дешифратора 8. В зависимостиот значения (+В) на выходе дешифратора 8 с номером (+В) появляется логическая "1", которая через элементИ 31 И 10 включает генератор,9 и открывает соответствующий элемент И 23.1,23.223.п. Генератор 9 выдает последовательным кодом единицу, которая через элемент И поступает на соответствующую выходную шину 25.1,25.225 п. Тем временем на входныешины 28,1, 28,228 ец поступает значение (2+А) в двоичной классическойсистеме счисления и записывается втриггеры параллельного сумматора 13.По сигналу на управляющей шине 21значение (2+А) выдается из сумматора 13 на входы схемы 12 сравнения идешифратора 14. По сигналу с выходаэлемента 17 задержки происходит сравнение значений (2+А) и (+В) в схеме 12 сравнения, выдается сигнал(2+А)( +В), то сигнал через элементИЛИ 10 поступает на вход управления дешифратора 14, на выходе дешифратора с номером (21+А) появляетсясигнал "1", который запоминается соответствующим триггером 24. и подключает выходную шину 26.х, Этим жесигналом запускается генератор 15,который выдает параллельным кодом навходы сумматора 13 обратный кодединицы. По этому же сигналу, задержанному в элементе 18 задержки, происходит выдача результата на вход схемы 12 сравнения, которая по сигналус выхода элемента 17 задержки производит сравнение значений (2+А) и(+В). Если (2+А) В (1+В), то процесс, только что описанный, повторяется до тех пор, пока (2 а+А-) нестанет меньше+В, В этом случаесигнал 1 поступает на вход элемента1 1 Ь.И 19, Если генератор 9 уже выдал код1, то с выхода элемента И .19 по шине29 включается блок 2 синхронизациигенератора.Формула изобретения451. Генератор возвратных последовательностей п-го порядка, содержащий п регистров, блок синхронизации, сум матор, причем первый выход блока сиь- хронизации подключен к управляющим 50 входам всех регистров, второй выход блока синхронизации подключен к управляющему входу сумматора, выход первого регистра подключен к первому информационному выходу генеРатоРа, 55 о т,л и ч а ю щ и й с я тем, что, с целью расширения функциональных возможностей за счет генерации последовательности весов различных возврат 3 13631Генератор 15 формирует обратный код единицы разрядностью, равной разрядности параллельн сумматора 13.Таким образом, блок ч коммутаций5 и ввода начальных условий вводит в первые ( +В) регистров значение единицы и подключает выходы регистров1. с номерами хб +В; 2+А к входу сумматора 3 генератора возвратных последовательностей и-го порядка.При необходимости смоделировать другую возвратную последовательность подается сигнал на шину 22 сброса, затем вводятся новые значения ф +В) и (2+А).ПосЛе того, как введены начальные условия и сформированы подключениясоответствующих регистров 1. с номеромб +В; 2+А к входам суммато 20 ра 3 подается сигнал управления навход блока 2 синхронизации, который формирует синхросигнал на регистры1. и сумматор 3. В регистрах осуществляется перезапись информации 25 из младших в старшие, а в регистр1,1 записывается число, явившееся результатом суммирования содержимогорегистров 1. с номерами И+В; 2++А . Далее блок синхронизации вновьвыдает синхросигнал на регистры, чутьпозже - на сумматор, происходит аналогичный процесс перезаписи чисел вследующие регистры 1, и суммирования. Информация снимается с информационного выхода 7 (+В).Очевидно, что, изменяя значенияА, В,в выражении (1), можно синтезировать любую возвратную последовательность, которая используется в качестве базовой функции системы40 счисления с естественной избыточно.стью. 7 О4ных последовательностей, в него введены и элементов ИЛИ, элементов И, блок коммутаций и ввода начальных условий, причем выходы -х (1=1п) регистров подключены к первым входам соответствующих .-х элементов И, вторые входы которых подключены к соответствующим выходам первой группы из п выходов блока коммутаций и ввода начальных условий, каждый -й выход второй информационной группы выходов которого подключен к (п-.+1)-му входу всех элементов ИЛИ с первого по .-й группы элементов ИЛИ, выход сумматора подключен к (и+1)-му входу первого элемента ИЛИ группы, выходы .-х регистров подключены к (п-.+1)-му входу (+1)-го элемента ИЛИ группы, выходы -х элементов И подключены к соответствующим входам сумматора, вход запуска блока синхронизации подключен к выходу запуска блока коммутаций и ввода начальных условий, выходы регистров с второго по и-й подключены к соответствующим выходам с второго по п-й генератора.2. Генератор по п. 1, о т л ич а ю щ и й с я тем, что блок коммутаций и ввода начальных условий содержит два дешифратора, параллельный сумматор, генератор кода единицы, генератор обратного кода единицы, два элемента задержки, три элемента ИЛИ, схему сравнения, и-разрядный регистр, элемент И, группу из и элементов И, и триггеров, причем вход п-разрядного регистра и вход первого дешифратора подключен к первой группе информационных входов блока, выходы пешифратора подключены к первым входам элементов И группы, к и входам первого элемента ИЛИ, выход которого подключен к входу пуска генератора кода единицы, первый выход которого подключен к вторым входам элементов И группы, вторая группа информационных входов блока подключена к первой группе информационных входов параллельного сумматора, выход которого подключен к группе информационных входов второго дешифратора и первой группе входов схемы сравнения, вторая группа входов которой подключена к выходу и-разрядного регистра, вход управления блока подключен к первому входу второго элемента ИЛИ, выход которого подключен к входу управления параллельного сумматора и через первый элемент задержки к входу чправ,"Ц О Фиг, Г аз 6362/39 Тираж 671 Подписное ИИПИ роизв.-полигр. пр- Ужгород, ул. Проектная,тие, г. ления схемы сравнения, выходы второго дешийратоора подключены к входам установки триггеров, выходы которых подключены к первой группе информаци 5 онных выходов блока, вход сброса которого подключен к входам сброса триггеров, выход генератора обратного .ко 1 ца единицы подключен к второй группе входов параллельного сумматора, вход младшего разряда которого подключен к выходу переноса старшего разряда и-разрядного регистра, выходы элементов И группы подключены к второй группе информационных выходов блока, вы 70Бход запуска которого подключен к выходу элемента И, первый вход которого подключен к второму выходу генератора кода единицы, второй вход элемента И подключен к выходу "Меньше" схемы сравнения, выходы "Больше" и "Равно" которой подключены к первому и второму входам третьего элемента ИЛИ, выход которого подключен к управляюшему входу второго дешифратора, входу запуска генератора обратного кода единицы и через второй элемент задержки к второму входу второго элемента ИЛИ.

СмотретьЗаявка

4092620, 11.05.1986

КРАСНОДАРСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК

ТКАЧЕНКО АЛЕКСАНДР ВАСИЛЬЕВИЧ, ДУДКИН ВЛАДИСЛАВ ВАЛЕРЬЕВИЧ

МПК / Метки

МПК: G06F 1/02

Метки: возвратных, генератор, го, порядка, последовательностей

Опубликовано: 30.12.1987

Код ссылки

<a href="https://patents.su/4-1363170-generator-vozvratnykh-posledovatelnostejj-go-poryadka.html" target="_blank" rel="follow" title="База патентов СССР">Генератор возвратных последовательностей -го порядка</a>

Предыдущий патент: Устройство для контроля

Следующий патент: Устройство для останова микропроцессора

Случайный патент: Тастатурный электронный номеронабиратель