Сумматор -разрядного единичного кода

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

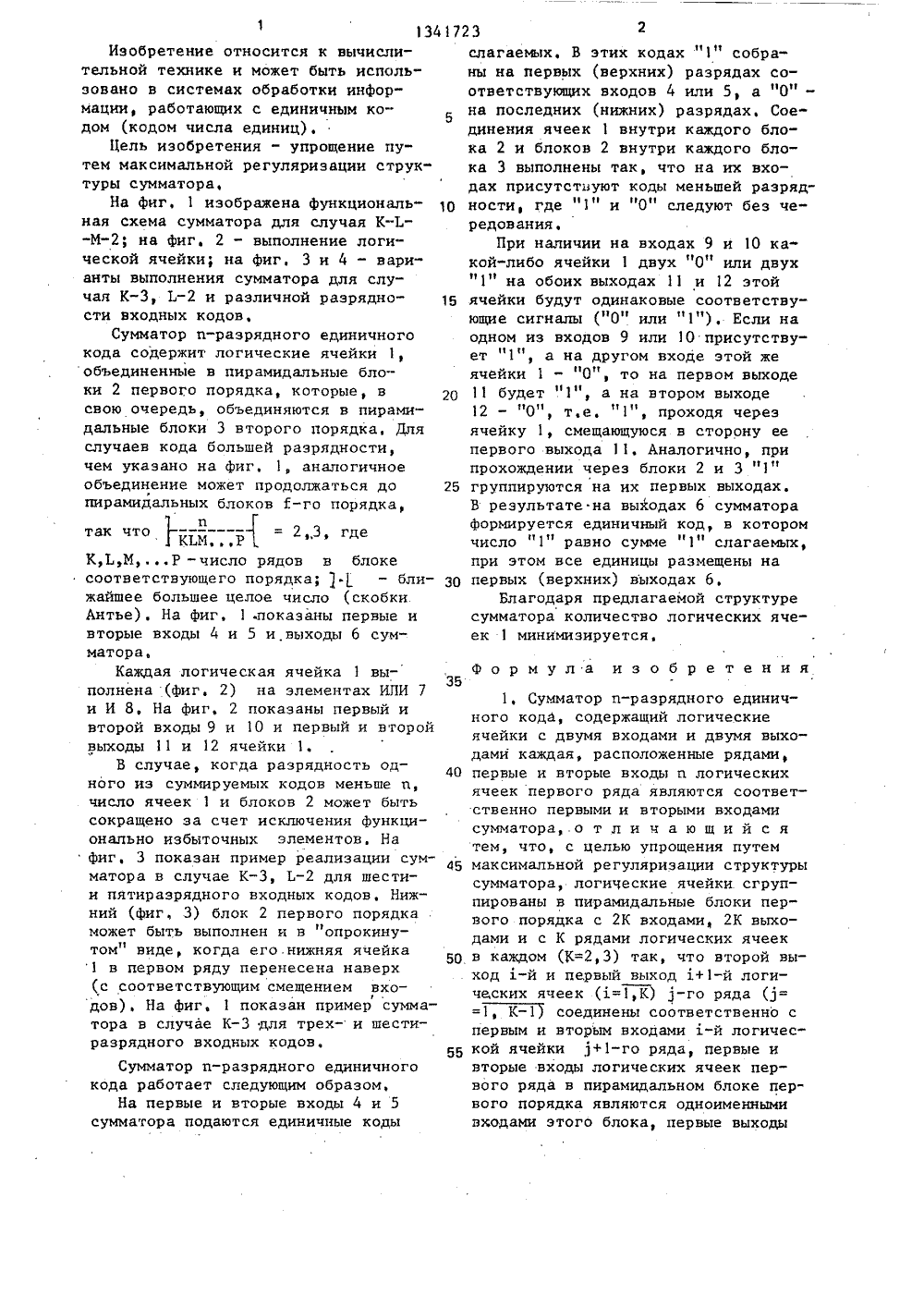

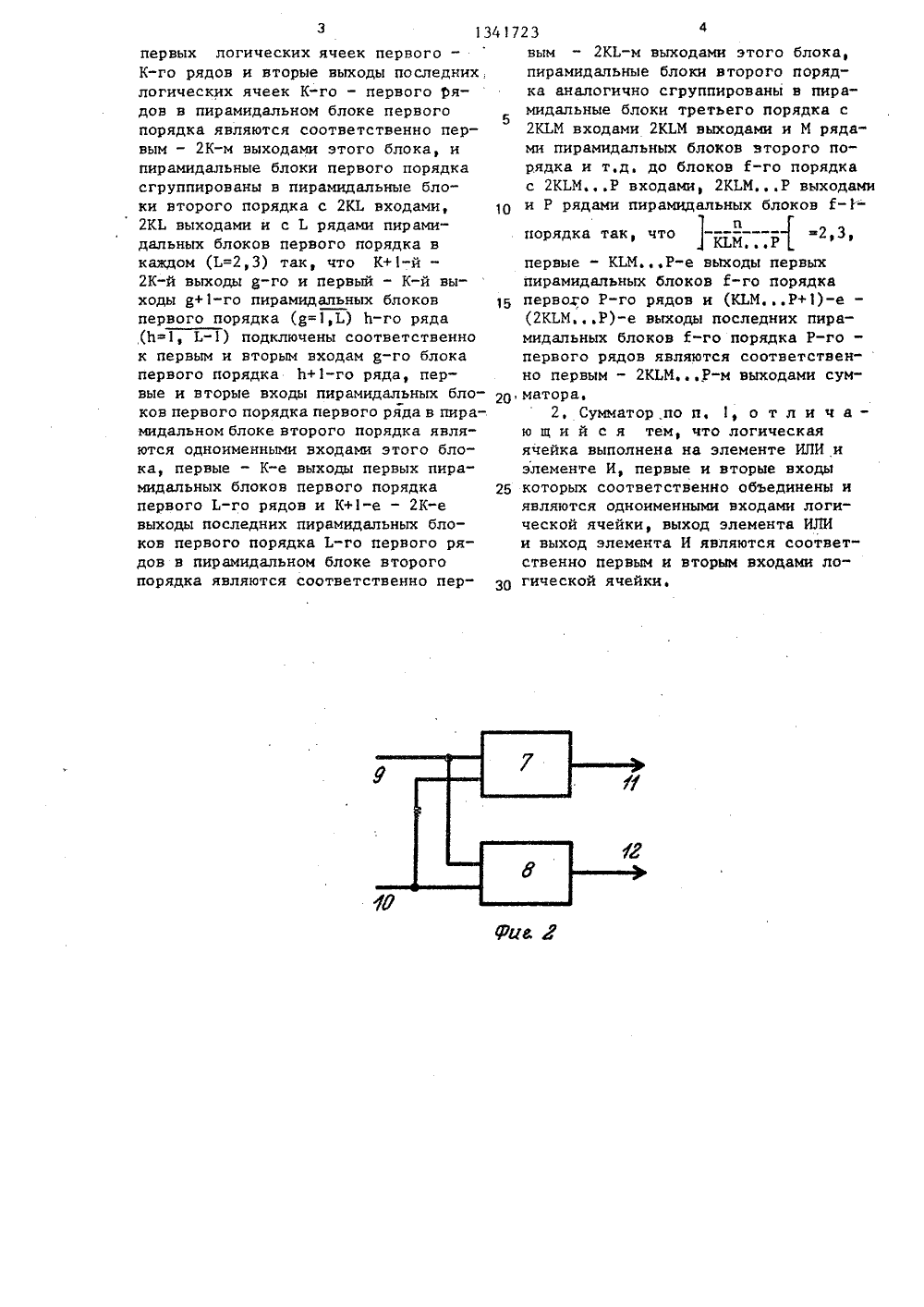

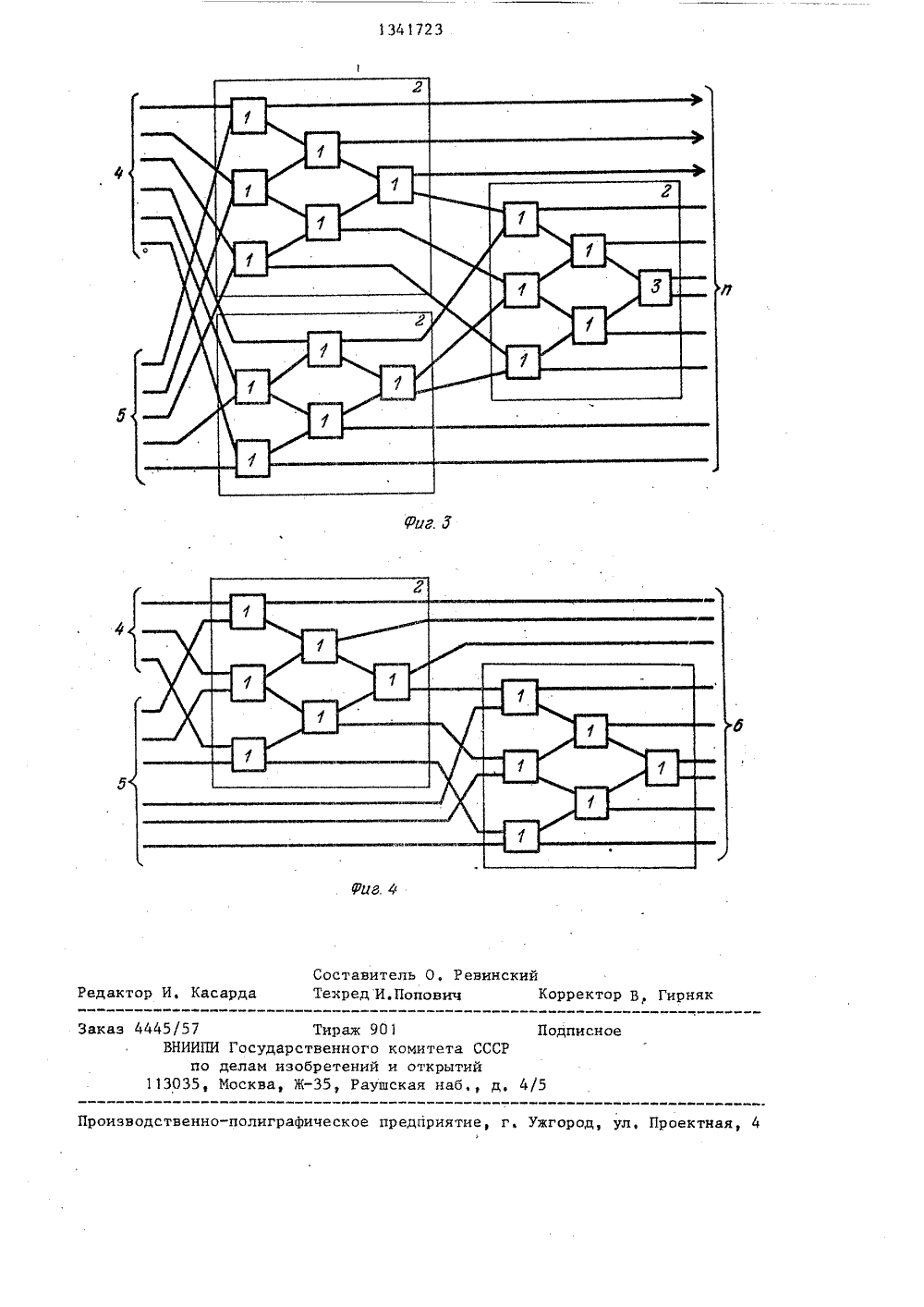

1134Изобретение относится к вычислительной технике и может быть использовано н системах обработки информацки, работающих с единичным кодом (кодом числа единиц).11 ель изобретения - упрощение путем максимальной регуляризации струк"туры сумматора,На фиг, 1 изображена функциональная схема сумматора для случая К-Ь-М; на фиг, 2 - выполнение логической ячейки; на фиг, 3 и 4 - варианты выполнения сумматора для случая К-З, 1-2 и различной разрядности входных кодов,Сумматор и-разрядного единичногокода содержит логические ячейки 1,объединенные в пирамидальные блоки 2 первого порядка, которые, всвою очередь, объединяются в пирамидальные блоки 3 второго порядка, Дляслучаев кода большей разрядности,чем указано на фиг, 1, аналогичноеобъединение может продолжаться допирамидальных блоков Й-го порядка,итак что - = 23, гдеК,Ь,М,Р в чис рядов в блокесоответствующего порядка; 1.1 - ближайшее большее целое число (скобкиАнтье), На фиг, 1 .показаны первые ивторые входы 4 и 5 и выходы б сумматора,Каждая логическая ячейка 1 выполнена (фиг. 2) на элементах ИЛИ 7и И 8, На фиг. 2 показаны первый ивторой входы 9 и 10 и первый и второйвыходы 11 и 12 ячейки 1.В случае, когда разрядность одного из суммируемых кодов меньше и,число ячеек 1 и блоков 2 может бытьсокращено за счет исключения функционально избыточных элементов, Нафиг, 3 показан пример реализации сумматора в случае К-З, Ьдля шестии пятиразрядного входных кодов, Нижний (фиг 3) блок 2 первого порядкаможет быть выполнен и в "опрокинутом" виде, когда его.нижняя ячейка1 в первом ряду перенесена наверх(с соответствующим смещением вхо(дов), На фиг. 1 показан пример сумматора в случае Кдля трех- и шестиразрядного входных кодов,1123 2слагаемых, В этих кодах "1" собраны на первых (верхних) разрядах соответствующих входов 4 или 5, а "0" -на последних (нижних) разрядах. Соединения ячеек 1 внутри каждого блока 2 и блоков 2 внутри каждого блока 3 выполнены так, что на их входах присутствуют коды меньшей разряд 10 ности, где "1" и "0" следуют без чередования,При наличии на входах 9 и 10 какой-либо ячейки 1 двух "0" или двух"1" на обоих выходах 11 и 12 этой15 ячейки будут одинаковые соответстнующие сигналы ("0" или "1"). Если наодном из входов 9 или 10 присутствует "1", а на другом входе этой жеячейки 1 - "0", то на первом выходе2 п 11 будет "1", а на втором выходе12 - "0", т,е. "1", проходя черезячейку 1, смещающуюся в сторону еепервого выхода 11. Аналогично, припрохождении через блоки 2 и 3 "1"25 группируются на их первых выходах.В результате на выходах 6 сумматораформируется единичный код, в которомчисло "1" ранно сумме "1" слагаемых,при этом все единицы размещены наЗО первых (верхних) выходах б,Благодаря предлагаемой структуресумматора количество логических ячеек 1 минимизируется,Сумматор и-разрядного единичного кода работает следующим образом,На первые и вторые входы 4 и 5 сумматора подаются единичные кодыФормула изобретения35 1, Сумматор и-разрядного единичного кода, содержащий логическиеячейки с двумя входами и двумя выходами каждая, расположенные рядами, 40 первые и вторые входы и логическихячеек первого ряда являются соответственно первыми и вторыми входамисумматора,.о т л и ч а ю щ и й с ятем, что, с целью упрощения путем 45 максимальной регуляризации структурысумматора, логические ячейки сгруппированы н пирамидальные блоки первого порядка с 2 К входами 2 К выходами и с К рядами логических ячеек 50 н каждом (К=2,3) так, что второй выход д-й и первый выход +1-й логических ячеек (=1,К) 1-го ряда Ц=Ксоединены соотеетственно спервым и вторым входами 1.-й логичес кой ячейки 1+1-го ряда, первые ивторые входы логических ячеек первого ряда в пирамидальном блоке первого порядка являются одноименнымивходами этого блока, первые выходы13417 15 первых логических ячеек первого -К-го рядов и вторые выходы последних.логических ячеек К-го - первого рядов в пирамидальном блоке первогопорядка являются соответственно первым - 2 К-м выходами этого блока, ипирамидальные блоки первого порядкасгруппированы в пирамидальные блоки второго порядка с 2 КЬ входами,2 КЬ выходами и с Ь рядами пирамидальных блоков первого порядка вкаждом (Ь=2,3) так, что К+1-й -2 К-й выходы я-го и первый - К-й выходы р+1-го пирамидальных блоковпервого порядка (д=,Ь) Ь-го ряда(Ь 1, Ь) подключены соответственнок первым и вторым входам я-го блокапервого порядка 5+1-го ряда, первые и вторые входы пирамидальных бло,ков первого порядка первого ряда в пирамидальном блоке второго порядка являются одноименными входами этого блока, первые - К-е выходы первых пирамидальных блоков первого порядка 25первого Ь-го рядов и К+1-е - 2 К-евыходы последних пирамидальных блоков первого порядка Ь-го первого рядов в пирамидальном блоке второгопорядка являются соответственно пер 234вым - 2 КЬ-м выходами этого блока,пирамидальные блоки второго порядка аналогично сгруппированы в пирамидальные блоки третьего порядка с2 КЬМ входами 2 КЬМ выходами и М рядами пирамидальных блоков второго порядка и т,д, до блоков Е-го порядкас 2 КЬМР входами, 2 КЬМР выходамии Р рядами пирамидальных блоков Гипорядка так что --- Х 2 391 КЬМР 1 ф фпервые - КЬМР-е выходы первыхпирамидальных блоков Е-го порядкапервоо Р-го рядов и (КЬМР+1)-е(2 КЬМР)-е выходы последних пирамидальных блоков Й-го порядка Р-го -первого рядов являются соответственно первым - 2 К 1 МР-м выходами сумматора,2. Сумматор,по п, 1, о т л и ч аю щ и й с я тем, что логическаяячейка выполнена на элементе ИЛИ иэлементе И, первые и вторые входыкоторых соответственно объединены иявляются одноименными входами логической ячейки, выход элемента ИЛИи выход элемента И являются соответственно первым и вторым входами логической ячейки,1341723 и 8. Составитель О, Техред И.Попов вински Редактор И. Касарда рректор В, Гир 5/57 Тираж 901 ВНИИПИ Государственного комитетпо делам изобретений и откры 3035, Москва, Ж, Раушская на аказ 44 писно СССРй Ужгород, ул ктная, 4 Производственно-полиграфическое предприяти

СмотретьЗаявка

4016996, 06.02.1986

ПРЕДПРИЯТИЕ ПЯ Г-4149

СОЛОДУХИН БОРИС МИХАЙЛОВИЧ, ФЕДОРОВ СЕРГЕЙ МИХАЙЛОВИЧ, СЕРКОВ АЛЕКСАНДР СЕРГЕЕВИЧ, ИЗМАЛКОВ ВИКТОР ВАЛЕНТИНОВИЧ

МПК / Метки

МПК: H03M 7/00

Метки: единичного, кода, разрядного, сумматор

Опубликовано: 30.09.1987

Код ссылки

<a href="https://patents.su/4-1341723-summator-razryadnogo-edinichnogo-koda.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор -разрядного единичного кода</a>

Предыдущий патент: Преобразователь кода числа во временной интервал

Следующий патент: Устройство для автовыбора каналов по временным искажениям двоичных сигналов

Случайный патент: Способ производства цементного клинкера