Устройство формирования сигнала отсчета для дифференциального кодера изображений

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1332562

Авторы: Копылов, Райхельсон

Текст

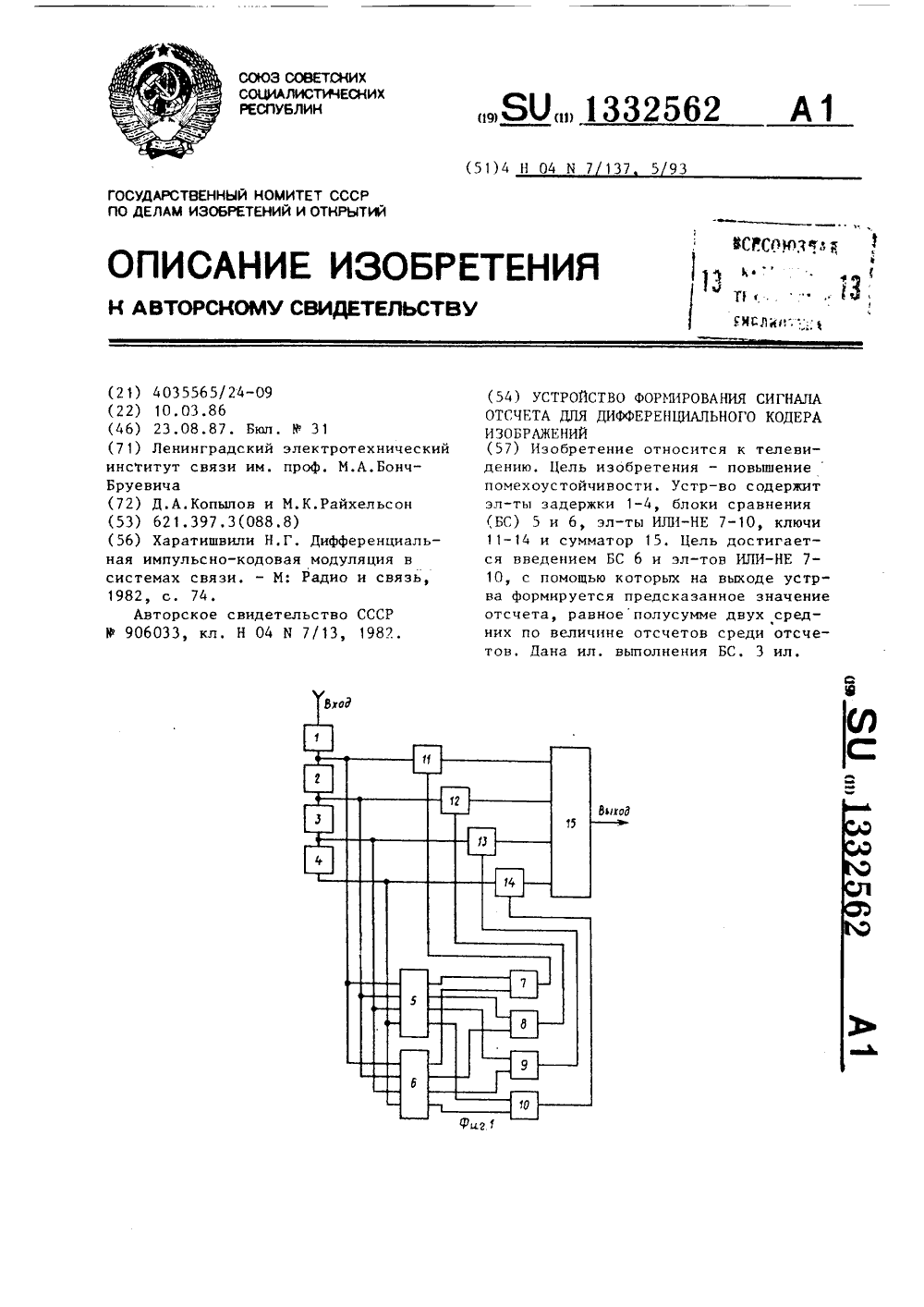

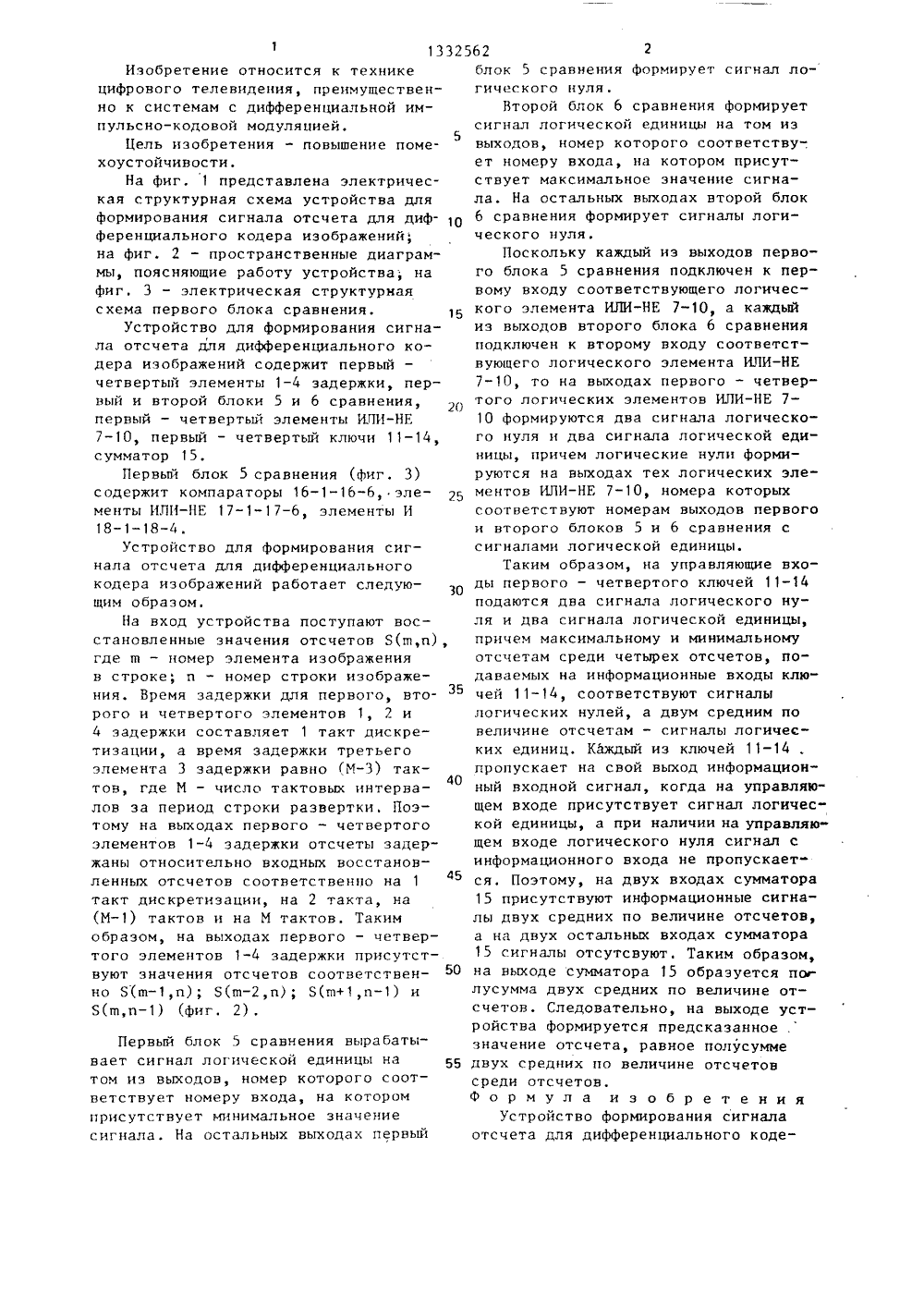

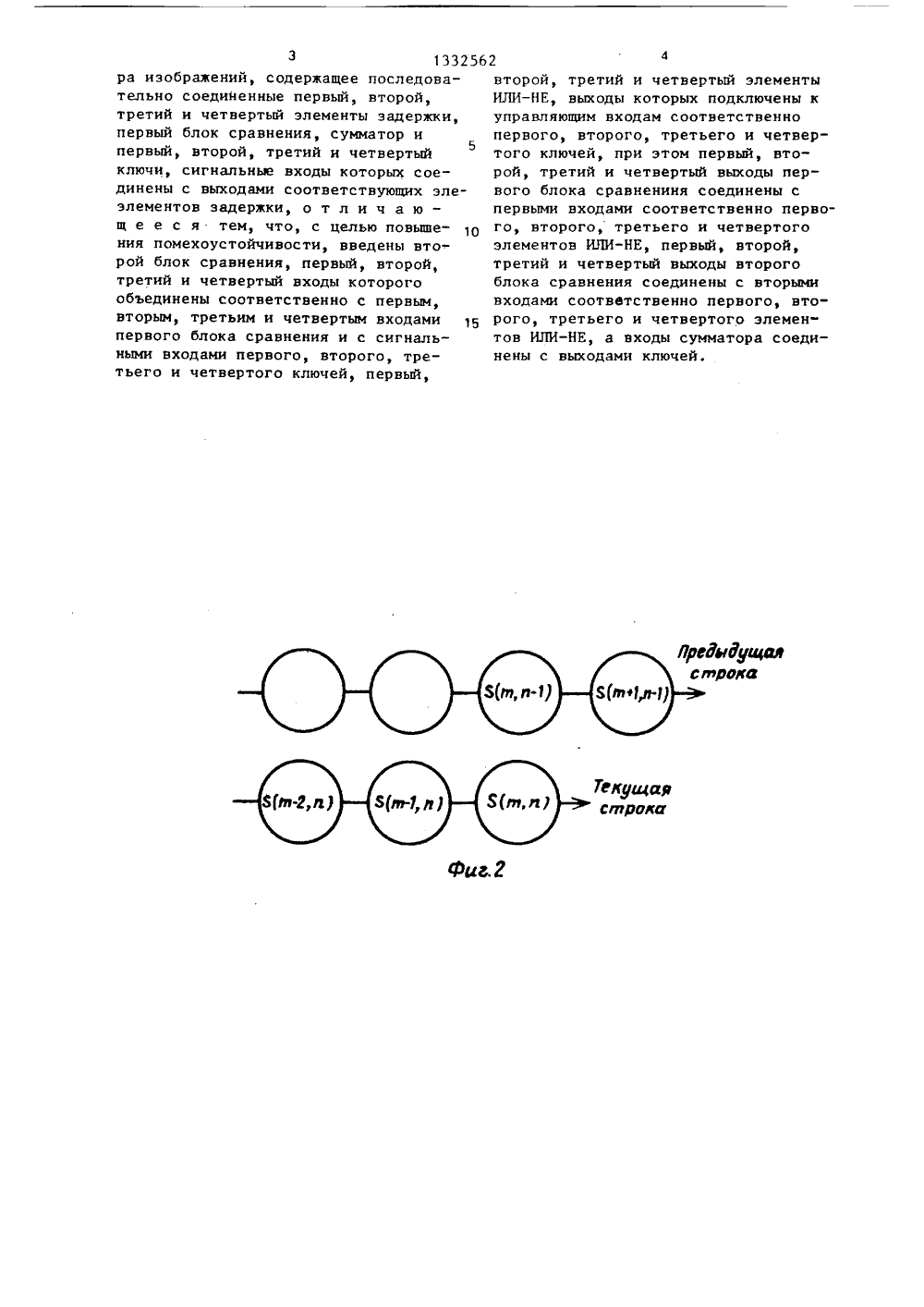

ивос о содержит сравнения - 10, ключи достигает- ИЛИ-НЕ 7- ыходе устр М. К.Райхельсон8) Г. Дифференциа ая модуляция вРадио и связ ато ся введением 10, с помощь ва формирует и э рьж ю ко сказанное значе ельство СССР М 7/13, 198,отсчет олусумме двух средтсчетов среди отсче олнения БС. 3 ил. них по велич тов. Дана ил в ГОСУДАРСТВЕНКЫИ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИ А ВТОРСНОМУ СВИДЕТЕЛЬСТВ(54) УСТРОЙ ОТСЧЕТА ДЛЯ ИЗОБРАЖЕНИЙ (57) Иэобре дению, Цель помехоустой эл-ты задер (БС) 5 и 6, 11-14 и сум ТВО ФОРМИРОВАНИЯ СИГНАЛАДИФФЕРЕНЦИАЛЬНОГО КОДЕР1 1332Изобретение относится к техникецифрового телевидения, преимущественно к системам с дифференциальной импульсно-кодовой модуляцией,5Цель изобретения - повышение помехоустойчивости.На фиг, 1 представлена электрическая структурная схема устройства дляформирования сигнала отсчета для дифференциального кодера изображений,на фиг. 2 - пространственные диаграммы, поясняющие работу устройства, нафиг. 3 - электрическая структурнаясхема первого блока сравнения, 15Устройство для формирования сигнала отсчета для дифференциального кодера иэображений содержит первый -четвертый элементы 1-4 задержки, первый и второй блоки 5 и 6 сравнения,первый - четвертый элементы ИЛИ-НЕ7-10, первый - четвертый ключи 11-14,сумматор 15,Первый блок 5 сравнения (фиг. 3)содержит компараторы 16-1-16-6, элементы ИЛИ-НЕ 17-1 - 17-6, элементы И18-1 - 18-4.Устройство для формирования сигнала отсчета для дифференциальногокодера изображений работает следующим образом.На вход устройства поступают восстановленные значения отсчетов Б(ш,п),где ш - номер элемента изображенияв строке, и - номер строки изображения. Время задержки для первого, второго и четвертого элементов 1, 2 и4 задержки составляет 1 такт дискретизации, а время задержки третьегоэлемента 3 задержки равно (М) тактов, где М - число тактовых интерва 40лов за период строки развертки. Поэтому на выходах первого - четвертогоэлементов 1-4 задержки отсчеты задержаны относительно входных восстановленных отсчетов соответственно на 1такт дискретизации, на 2 такта, на(М) тактов и на М тактов. Такимобразом, на выходах первого - четвертого элементов 1-4 задержки присутствуют значения отсчетов соответственно Ят,п); 8(т,п); Б(оп+1,и) иЯ(гп,п) (фиг. 2),Первый блок 5 сравнения вырабатывает сигнал логической единицы на 55 том из выходов, номер которого соответствует номеру входа, на котором присутствует минимальное значение сигнала, На остальных выходах первый 562 2блок 5 сравнения формирует сигнал ло-гического нуля.Второй блок 6 сравнения формируетсигнал логической единицы на том извыходов, номер которого соответствует номеру входа, на котором присутствует максимальное значение сигнала. На остальных выходах второй блок 6 сравнения формирует сигналы логического нуля.Поскольку каждый из выходов первого блока 5 сравнения подключен к первому входу соответствующего логического элемента ИЛИ-НЕ 7-10, а каждый из выходов второго блока 6 сравнения подключен к второму входу соответствующего логического элемента ИЛИ-НЕ 7-10, то на выходах первого - четвертого логических элементов ИЛИ-НЕ 7- 10 формируются два сигнала логического нуля и два сигнала логической единицы, причем логические нули формируются на выходах тех логических элементов ИЛИ-НЕ 7-10, номера которых соответствуют номерам выходов первого и второго блоков 5 и 6 сравнения с сигналами логической единицы.Таким образом, на управляющие входы первого - четвертого ключей 11-14 подаются два сигнала логического нуля и два сигнала логической единицы, причем максимальному и минимальному отсчетам среди четырех отсчетов, подаваемых на информационные входы ключей 11-14, соответствуют сигналы логических нулей, а двум средним по величине отсчетам - сигналы логических единиц, Каждый из ключей 11-14 пропускает на свой выход информационный входной сигнал, когда на управляю" щем входе присутствует сигнал логической единицы, а при наличии на управляющем входе логического нуля сигнал с информационного входа не пропускается. Поэтому, на двух входах сумматора 15 присутствуют информационные сигналы двух средних по величине отсчетов, а на двух остальных входах сумматора15 сигналы отсутсвуют. Таким образом,на выходе сумматора 15 образуется пог лусумма двух средних по величине отсчетов. Следовательно, на выходе устройства формируется предсказанное . значение отсчета, равное полусумме двух средних по величине отсчетов среди отсчетов.Формула и з обретенияУстройство формирования сигнала отсчета для дифференциального коде1332562 Фи оставитель Э,Борисов ехред И.Попович Корректор В,Бутяг Редактор Н. каз 3851/57 Тираж 638 ВНИИПИ Государственног по делам изобретений 113035, Москва, Ж, исное омитета Соткрытий ушская на роизводственно-полиграфическое предприятие Входы 1234 город, ул. Проектная, 4

СмотретьЗаявка

4035565, 10.03.1986

ЛЕНИНГРАДСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. ПРОФ. М. А. БОНЧ-БРУЕВИЧА

КОПЫЛОВ ДМИТРИЙ АНДРЕЕВИЧ, РАЙХЕЛЬСОН МИХАИЛ КУСЕВИЧ

МПК / Метки

МПК: H04N 5/93, H04N 7/30, H04N 7/42

Метки: дифференциального, изображений, кодера, отсчета, сигнала, формирования

Опубликовано: 23.08.1987

Код ссылки

<a href="https://patents.su/4-1332562-ustrojjstvo-formirovaniya-signala-otscheta-dlya-differencialnogo-kodera-izobrazhenijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство формирования сигнала отсчета для дифференциального кодера изображений</a>

Предыдущий патент: Устройство формирования сигналов изображения

Следующий патент: Устройство для определения центров интерференционных полос

Случайный патент: Еская библиотека