Устройство для обнаружения ошибок в параллельном п разрядном коде

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1325482

Автор: Музыченко

Текст

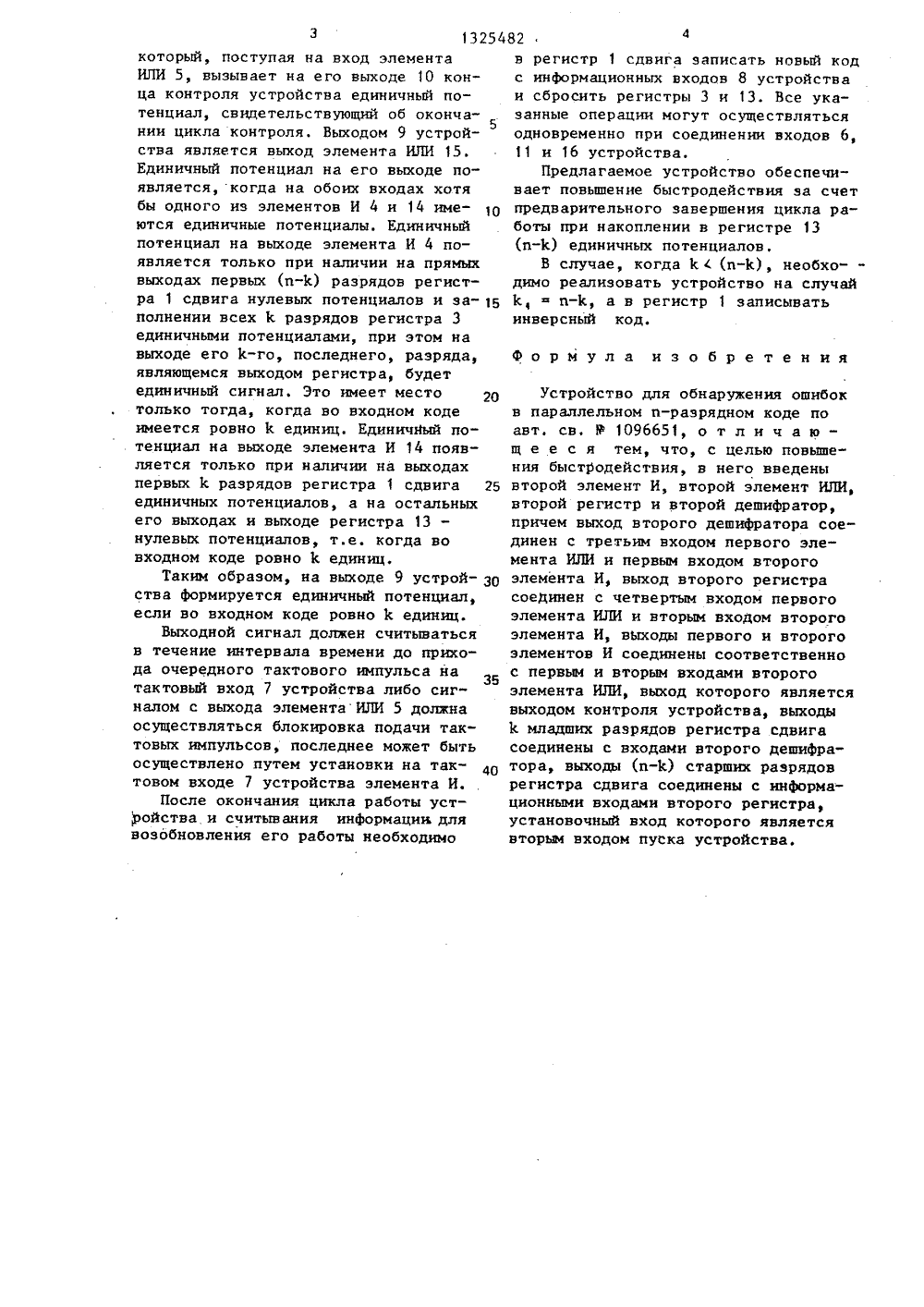

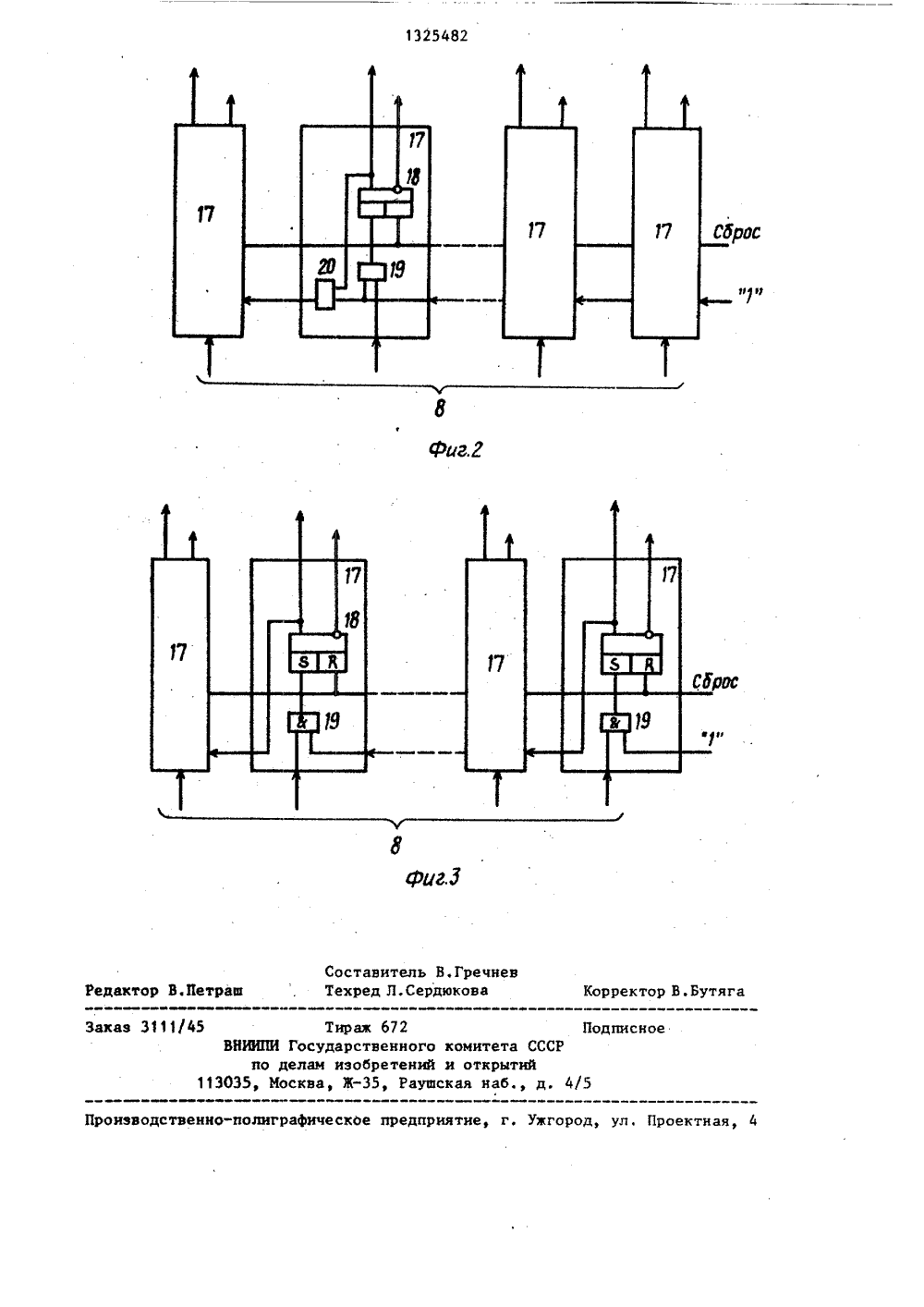

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКРЕСПУБЛИК 19) О 1) 6 Р 11/08 51) ХНИЯ ОБР ОПИС ИДЕТ ЕЛЬС АВТОРСНО ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(56) Авторское свидетельство СССРВ 1096651, кл. С 06 Р 11/08, 1982.(54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОШИБОК В ПАРАЛЛЕЛЬНОМ и-РАЗРЯДНОМ КОДЕ(57) Изобретение относится к автоматике и вычислительной технике и можетиспользоваться для построения различных устройств передачи и переработкидискретной информации. Цель изобретения - повышение быстродействия,Сигнал, поступающий на вход 6 разрешения записи устройства, записываетна регистр 1 сдвига информацию с информационного входа 8 устройства.Сигналы, поступающие на входы пуска11, 16 устройства, устанавливают внулевое состояние регистры 3, 13. Импульсы с тактового входа 7 устройстваначинают сдвигать информацию на регистре 1 сдвига. Единичный сигнал навыходе первого дешифратора 2 формируется, когда (и-к) младших разрядоврегистра 1 сдвига находятся в нулевомсостоянии. Единичный сигнал на выхо 1;де первого регистра 3 формируется,когда 1 с старших разрядов регистра 1сдвига находятся в единичном состоянии. Отсутствие ошибки в принятом коде означает, что на выходах первогодешифратора 2 и первого регистра Эединичные сигналы появятся одновременно. При этом сработает первый элемент И 4 и на выходе 9 контроля устройства будет единичный сигнал. Второй дешифратор 12 и второй регистр 13фиксируют моменты возникновения единичных сигналов на выходах всехмладших разрядов и нулевых сигналовна выходах всех (и) старших разрядов регистра 1 сдвига соответственно,Одновременное появление единичныхсигналов на выходах дешифратора 12 ирегистра 13 фиксируется вторым элементом И 14, выход которого соединен1325482 с входом второго элемента ИЛИ 15. Появление единичного сигнала на выходехотя бы оДного из дешифраторов 2, 12или одного из регистров 3, 13 фиксируется первым элементом ИЛИ 5, выходкоторого является выходом 10 конца Изобретение относится к автоматикеи вычислительной технике, может использоваться для построения различныхустройств передачи и переработки дис 5кретной информации и является усовершенствованием устройства по авт. св.,У 1096651.Цель изобретения " повышение быстродействия. 10На фиг.1 приведена функциональнаясхема устройства; на фиг.2 и 3 - схема регистров, варианты выполнения.Устройство для обнаружения ошибокв параллельном и-разрядном коде содержит регистр 1 сдвига, первый дешифратор 2, первый регистр 3, первыйэлемент И 4, первый элемент ИЛИ 5,фвход 6 разрешения записи устройства,тактовый вход 7 устройства, информационный вход 8 устройства, выход 9контроля и выход 10 конца контроляустройства, первый вход 11 пуска устройства, второй дешифратор 12, второйрегистр 13, второй элемент И 14, второй элемент ИЛИ 15, второй вход 16пуска устройства,Регистр 3 (13) содержит группу 17разрядов, в состав которых входиттриггер 18 и элементы И 19 и 20. 30Дешифратор 2 (12) может быть выполнен в виде элемента И, соединенно"го входами с инверсными (прямыми) выходами младших и-К (К) разрядов регистра 1 сдвига (первым является крайний левый разряд), либо в виде элемента И с инверсными входами, соединенного с прямыми (инверсными) выходами младших иЬ) разрядов регистра 1 сдвига.40Регистр 3 (13) может быть выполнен, ка в известном устройстве (Фиг.2),в виде последовательно соединенныхразрядов, каждый из которых содержитКБ-триггер и два элемента И, либо контроля устройства. Одновременноепоявление единичных сигналов на выходах 9, 10 устройства говорит о правильном приеме кода. Наличие единичного кода только на выходе 10 устройства говорит об ошибке в приеме. 3 ил,(Фиг,З) в виде последовательно соединенных разрядов, каждый из которых содержит элемент И и КБ-триггер.Устройство работает следующим образом.В исходном состоянии регистр 1 сдвига, регистры 3 и 13 сброшены, На вход 6 разрешения записи устройства и регистра 1 сдвига подается сигнал разрешения записи, при этом в регистр 1 сдвига записывается код с информационного входа 8 устройства. На входы 11 и 16 регистров 3 и 13 подаются сигналы сброса (можно одновременно с сигналом на вход 6 устройства). По окончании сигнала разрешения записи на тактовый вход 7 устройства, являющийся входом сдвига регистра 1.сдвига, подаются тактовые импульсы. При подаче тактового импульса код в регистре 1 сдвига сдвигается на один разряд вправо. При появлении единичного потенциала на выходе и-го разряда регистра 1 сдвига (нулевого потенциала на выходе и-го разряда) в первый разряд регистра 3 (13) записывается единичный потенциал, При появлении единичного (нулевого) потенциала на выходе (и)-го разряда регистра 1 сдвига единичный потенциал записывается во второй разряд регистра 3 (13), нри этом разрешается запись в его очередной разряд и т.д. Если единичный (нулевой) потенциал появляется сразу на нескольких очередных выходах регистра 1 сдвига, то он записывает сразу во все следующие разряды регистра 3 (13) единичный потенциал, при этом разрешается запись в его очередной разряд.функционирование происходит таким образом до появления единичного потенциала на выходе дешифратора 2 или 12 ипи на выходе регистра 3 или 13, 3 13254 который, поступая на вход элемента ИЛИ 5, вызывает на его выходе 10 конца контроля устройства единичный потенциал свидетельствующий об окончаУ5 нии цикла контроля, Выходом 9 устройства является выход элемента ИЛИ 15. Единичный потенциал на его выходе появляется, когда на обоих входах хотя бы одного из элементов И 4 и 14 име ются единичные потенциалы. Единичный потенциал на выходе элемента И 4 появляется только при наличии на прямых выходах первых (п-Е) разрядов регистра 1 сдвига нулевых потенциалов и за полнении всех Е разрядов регистра 3 единичными потенциалами, при этом на выходе его Е-го, последнего, разряда, являющемся выходом регистра, будет единичный сигнал. Это имеет место 2 О только тогда, когда во входном коде имеется ровно Е единиц. Единичный потенциал на выходе элемента И 14 появляется только при наличии на выходах первых к разрядов регистра 1 сдвига 25 единичных потенциалов, а на остальных его выходах и выходе регистра 13 - нулевых потенциалов, т.е. когда во входном коде ровно К единиц.Таким образом, на выходе 9 устрой- ЗО ства формируется единичный потенциал, если во входном коде ровно Е единиц.Выходной сигнал должен считываться в течение интервала времени до прихода очередного тактового импульса на тактовый вход 7 устройства либо сигналом с выхода элемента ИЛИ 5 должна осуществляться блокировка подачи тактовых импульсов, последнее может быть осуществлено путем установки на тактовом входе 7 устройства элемента И.После окончания цикла работы уст,ройства и считывания информации, для возобновления его работы необходимо 824в регистр 1 сдвига записать новый кодс информационных входов 8 устройстван сбросить регистры 3 и 13. Все указанные операции могут осуществлятьсяодновременно при соединении входов 6,11 и 16 устройства,Предлагаемое устройство обеспечивает повышение быстродействия за счетпредварительного завершения цикла работы при накоплении в регистре 13(и-к) единичных потенциалов,В случае, когда Е С (п-Е), необхо димо реализовать устройство на случайп-Е, а в регистр 1 записыватьинверсный код.Формула изобретенияУстройство для обнаружения ошибок в параллельном и-разрядном коде по авт. св, У 1096651, о т л и ч а ю щ е е с я тем, что, с целью повышения быстРодействия, в него введены второй элемент И, второй элемент ИЛИ, второй регистр и второй дешифратор, причем выход второго дешифратора соединен с третьим входом первого элемента ИЛИ и первым входом второго элемента И, выход второго регистра соединен с четвертым входом первого элемента ИЛИ и вторым входом второго элемента И, выходы первого и второго элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого является выходом контроля устройства, выходы 1 младших разрядов регистра сдвига соединены с входами второго дешифратора, выходы (ис) старших разрядов регистра сдвига соединены с информационными входами второго регистра, установочный вход которого является вторым входом пуска устройства.Заказ 311 1 одпис 1130 Проектная, 4 оизводственно-полиграфическое предприятие, г. Умгоро Тираж 672 ИИПИ Государственно по делам изобретен 5, Москва, Ж, Ра комитета СССРи открытийская наб., д. 4/5

СмотретьЗаявка

4032748, 06.03.1986

ВОЙСКОВАЯ ЧАСТЬ 31303

МУЗЫЧЕНКО ОЛЕГ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 11/08

Метки: коде, обнаружения, ошибок, параллельном, разрядном

Опубликовано: 23.07.1987

Код ссылки

<a href="https://patents.su/4-1325482-ustrojjstvo-dlya-obnaruzheniya-oshibok-v-parallelnom-p-razryadnom-kode.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения ошибок в параллельном п разрядном коде</a>

Предыдущий патент: Устройство для сдвига информации с контролем

Следующий патент: Устройство для вычисления контрольного элемента и обнаружения ошибок

Случайный патент: Вибрационная машина