Аналого-цифровой сумматор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

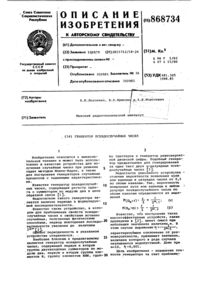

(504 С 06 С 7/1 ИСАНИЕ ИЗОБРЕТ ни ели оманцовий гические оснольной техники.1972, с, 155,а цифровс, 142,ализ тв,ГОСУДАРСТВЕННЫЙ КОМИТЕТ ССПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫ ТОРСКОМУ СВИДЕТЕЛЬС(71) Институт проблемв энергетике АН УССР(56) Папернов А.А. Ловы цифровой вычислитеМ.: Советское радио,рис. 1.Карцев М,А. АрифметмашинМ.: Наука, 1969рис, 2-1,4) АНАЛОГО-ЦИФРОВОЙ СУММАТОР7) Изобретение относится к гибрй вычислительной технике и може ыть использовано при построении спеванных вычислительных уст риентированных на решение систем алгебраических дифференциаль.ных и разностных уравнений. Цельюизобретения является повышение точности и разрешающей способности сумматораАналого-цифровой сумматорсодержит цифровой и-разрядный комбинационный сумматор 1, аналоговыйинвертор 3, первый компаратор 4, КБтриггер 5, второй компаратор 6, первый 7, второй 8 и третий 9 ключи,первую, вторую и третью шины эталонных напряжений 10, 11 и 12, входы13 и выходы 14, Достижение цели обеспечивается благодаря введению в цифровой комбинационный сумматор дополнительного аналогового разряда, содержащего аналоговый сумматор с четырьмя входами, аналоговый инвертор,схему сравнения ВБ-триггер, два компаратора, первый, второй и третийключи, а также новым связям междуперечисленными элементами, 1 ил.6006 2лонного напряжения единицы аналогово.го переноса, а информационный входвторого ключа 8 - с шиной 1 О эталонного напряжения, соответствующегоцифровой единице. Третий и четвертыйвходы 13 аналогового сумматора 2 вместе с первыми и вторыми входами 13 иразрядов цифрового п-разрядного комбинационного сумматора 1 являются 1 О двумя (и+1)-разрядными входами 13устройства, а выход 14 аналоговогоинвертора 3 вместе с выходами 14 празрядов цифрового п-разрядного комбинационного сумматора 1 является вы ходом (и+1)-го разряда сумматора.Рассмотрим работу сумматора напримерах суммирования чисел при п=3,т.е. когда устройство содержит трицифровых одноразрядных сумматорадля суммирования целых частей и одинаналоговый разряд для суммированиядробных частей чисел.В двоичной системе счисления любое число может быть представлено 25 последовательностью двоичных цифр 13 0, ЫО "о М-Ф.1 Изобретение относится к вычислительной технике, в частности к гибридной вычислительной технике, и может быть использовано для построенияспециализированных вычислительныхустройств для решения алгебраическихи дифференциальных уравнений и многих других применений.Целью изобретения является повышение точности и разрешающей способности сумматора,На чертеже приведена схема (и+1)разрядного аналого-цифрового сумматора,Сумматор содержит цифровой и-разрядщй комбинационный сумматор 1,аналоговый сумматор 2, аналоговыйсумматор 2, аналоговый инвертор 3,первый компаратор 4, КБ-триггер 5,второй компаратор 6, первый ключ 7,второй ключ 8, третий ключ 9, первуюшину 10 эталонного напряжения, соответствующего цифровой единице,вторую шину 11 эталонного напряжения,соответствующего единице аналоговогопереноса, третью шину 12 эталонногонапряжения, соответствующего инвертированной цифровой единице, входы13 и выходы 14. где М; либо О, либо 1, а запятая отделяет целую часть числа от дробной.Выход переноса старшего разряда цифрового п-разрядного комбинационного сумматора 1 подключен к управляющему входу первого ключа 7, выход которого соединен с первым входом аналогового сумматора 2 с четырьмя входами, Выход аналогового сумматора 2 через аналоговый инвертор 3 подключен к первому входу компаратора 4, второй вход которого соединен с шиной 1 О эталонного напряжения цифровой единицы. Выход упомянутого компаратора 4 соединен с Б установочным входом триггера 5, выход которого подключен к управляющему входу второго ключа 8 и к управляющему входу третьего ключа 9, Вход третьего ключа 9 соединен с шиной 12 эталонного инвертированного напряжения цифровой единицы, а выход - с вторым входом аналогового сумматора 2. Выход второго ключа 8 соединен с шиной младшего разряда цифрового и-разрядного комбинационного сумматора 1. Выход аналогового сумматора 2 подключен к первому входу компаратора 6, второй вход которого соединен с шиной нулевого потенциала, а выход - с К входом КЯ- триггера 5. Информационный вход первого ключа 7 соединен с шиной 11 эта 30Эта запись соответствует сумместепеней числа 2, взятых с указанными в ней коэффициентамиЩ э 1 1 ох=с 2 +Ы.,2 ++о,2 +с(О 2 ++ 2 +с 12 +(2)Для ш=2 имеем2о -1х=6.,2 +о 2 +о 2 + 2 (3)В этом выражении представлены тристарших разряда числа для заданияего целой части и младший разряд длязадания его дробной части, Как видно из (3), в дробной части числа могут быть заданы только ноль либоединица с весом 0,5.В предлагаемом сумматоре младшийразряд является аналоговым, принципработы которого основан на суммировании токов. Информация на его входах 50 может задаваться в виде любого уровня напряжения в диапазоне от нуля доодного вольта,Выражение (3) для данного сумматора может быть представлено в видех=ос 2 +к,2 +м 2 +3,г, (4)где г - основание системы счисления (не обязательно двоичной);3 16006 4влет второй ключ 8, и ца вход шины переноса младшего разряда трс храэрядного цифрового сумматора 1 от шины 10 эталонного напряжения, соответствующего цифровой единице, подается единичный уровень, Единичный сигнал с выхода КБ-триггера 5 одновременно открывает третий ключ 9, и на второй вход аналогового сумматора 2 от шины 12 эталонного напряжения, соответствующего инвертированной цифровой единице, подается напряжение, равное ло уровню - 1 В. Следовательно, на выходе аналогового сумматора 2 устанавливается напряжение 11 =-(О 6+О 8 ььа . ь- 1,0) В=-0,4 В, а на выходе аналогового инвертора 3 - напряжение П =+0,4 В.На выходах 14 трехразрядного цифрового сумматора 1 устанавливается с учетом переноса из аналогового разряда код001 - целая часть 1-го числа, 001 - целая часть 2-го числа, 25 001 - перенос из младшего разряда т.е. У=1,6+1,8=3,4,(5) Работа сумматора начинается с момента подачи на шину 10 эталонногонапряжения, соответствующего цифровой единице, Ь,= В (при двоичнойсистеме счисления н цифровом сумматоре 1); на шину 12 эталонного напряжения, соответствующего инвертированной цифровой единице - Ь =1 В наь цЕ ь 30шину 11 эталонного напряжения, соответствующего единице аналогового переноса 1 =0,1 В (те, аналогоныйразряд является дробными в десятичной системе счисления перенос н этотразряд имеет вес младшей единицы это го же разряда и задается уровнем н0,1 В),Дноичные коды целых частей слагаемых х, и х (0,01 и 001 соотнетст- щненно) суммируются в трехразрядномцифровом сумматоре 1, а дробные части слагаемых х, и х задаются на треттьем и четвертом входах 13 аналогового сумматора 2 в виде напряжений, 45соответственно равных +0,6 В и+0,8 В и суммируются в аналоговомразряде,Напряжение на выходе аналоговогосумматора 2 П должно меняться от2 вылнулевого уровня до уровня в (0,6+0,8)==-1,4 В, а напряжение на выходе инвертора 3 П,В соответственно от нуЗВыьлевого уровня до уровня +1,4 В, Однако когда напряжение П достигаеть Вых 55уровня 1 В, срабатывает компаратор 4и по Б входу устанавливает КБ-триггер5 в единичное состояние. Единичныйсигнал с ныхода КБ-триггера 5 открыа,М., Я - сиьц олы чисс.л г-й системысчисления (для г=10 принимает любое значение из рядасимволов 0,1,29).Таким образом, если н единичныеуровни в цифровом сумматорезадаются напряжением 1 В, то в аналоговом разряде, например, при г=10 (ндесятичной системе счисления) входная информация (дробная часть чисел)может быть задана любым уровнем напряжения из ряда разрешенных уровней: 0,0 В, 0,1 В, ,0,9 В,Работу предлагаемого сумматорарассмотрим в предположении, что егоаналоговый младший разряд работаетс десятичной системе счисления,П р и м е р 1, Пусть необходимонайти сумму У чисел х,=1,6 и х=1,8,011 - целая часть суммы. Таким образом, целая часть полученной суммы чисел х, и х равна (011)=3 ю 1, а дРобнаЯ часть этих же чисел,полученная на выходе 14 аналоговогоразряда, равна (0,4),0 . Окончательноимеем правильный результат У=1,6+1,8==3,4,П р и м е р 2. Сумматоры с круговым (циклическим) переносом предназначены для суммирования чисел, заданных в прямых и обратных кодах: положительным числам соответствует прямой код, отрицательным - обратный,Старший разряд является знаковым,причем 0 знакового разряда соответствует положительному числу, а 1отрицательному.В соответствии с общим правиломнахождения обратного кода отрицательного числа, для отрицательных десятичных чисел, например для г -0 6Эи г =-0,8, обратные кодь равны соответственно (г,) =9,3 (г ) =9овр ь ььбр ь ьгде символ 9 (по аналогии с двоичным символом 1) в знаковом разрядесвидетельствует, что данный кодотрицательный. П р и м е р 3 Пусть необходимополучить сумму У чисел х,=-1,6 их =-1,8, У=-1,6-1,8=-3,4. Обратныедноичные коды целых частей чисел хи х равны соответственно (110) и2(110) , где третий старший разрядявляется знаковым, Обратные десятичные коды дробных частей чисел х их равны соответственно 9,3 и 9.1,где второй разряд является знаковым.В рассматриваемом сумматоре знак числа находится в старшем разряде цифрового трехразрядного сумматора 1Этот знак в равной мере относитсякак к целой части, числа, так и к 10его дробной части, Поэтому дробнаячасть чисел х, и х . задается в виденапряжений соответственно 0,3 В и0,1 В без знакового разряда.Итак, при задании исходной информации в цифровом трехразрядномсумматоре 1 на линии кругового (циклического) переноса появляется единичный сигнал, поступающий на управляющий вход первого ключа 7, Первый 20ключ 7 открывается, и от шины 1эталонного напряжения, соответствующей единице аналогового переноса,на первый вход аналогового сумматора 2 поступает эталонное напряжение 25единицы аналогового переносаЕВП фравное Б =0,1 В (младшая единицаГ 4 П хдробной части десятичного числа),В результате выходное напряжениеаналогового су 1 ыатора с четырьмявходами 2 ц становится равным2 вьхО =-(0,1+0,3+0,1)=-0)5 В. из обратного кода в прямой со знаком.Обратный код дробной части со знакомранен 9.5. Отсюда прямой код равенв (99-9,5)=-0,4. эультат Формула и з обретения Аналого-цифровой сумматор, содержащий цифровой и-разрядный комбинационный сумматор, два входа и выход которого являются соответственно цифровыми информационными входами и цифровым выходом сумматора, о т л и ч а ю щ и й с я тем, что, с целью повышения точности и разрешающей способности, он содержит последовательно включенные аналоговые сумматор и инвертор, КБ-триггер, первый и второй компараторы и первый, второй и третий ключи, информационные входы которых подключены соответственно к первой, второй и третьей шинам эталонных напряжений, выходы первого, второго и третьего ключей подключены соответственно к первому входу аналогового сумматора, к шине переноса младшего разряда цифрового п-разрядного комбинационного сумматора и к второму входу аналогового сумматора, третий и четвертый входы которого являются дополнительными аналоговыми информационными входами аналогоцифрового сумматора, управляющий вход первого ключа соединен с шиной переноса старшего разряда цифрового и- разрядного комбинационного сумматора, а управляющие входы второго и третьего ключей подключены к выходу КБ-триггера, установочные входы которого соединены с выходами соответственно первого и второго компараторов, входы первого компаратора подключены соответственно к информационному входу первого ключа и к выходу инвертора, а входы второго компаратора - соответственно к выходу аналогового сумматора и к шине нулевого потенциала, выход инвертора является дополнительным аналоговым выходом аналого-цифрового сумматора,1)=+0,5 В,Б =+(0,1+0,3+О,ЭвыхНа выходных шинах 14 разрядного сумматора ются коды: цифрового трех 1 устанавливаВНИИПИ Заказ 2365/52 Тираж 672 Подписное Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4 Выходное напряжение аналогового инвертора 3 и, следовательно, напряжение на выходной шине 14 аналогового разряда становятся равными 110 - целая часть 1-го числа,+ 110 - целая часть 2-го числа, 000 - перенос младших разрядов 45 1100 - целая часть суммы1 - единица кругового(циклического) переноса в младший разряд 50устройства, Таким образом, целая часть полученной суммы чисел х, и х равна (100), = -3 а дробная часть этих же чиселоравна +0,5. Преобразуем дробную часть Окончательно имеем правильный реУ=х,+х =-1,6-1,8=-3-0,4=-3,4,

СмотретьЗаявка

4015415, 24.01.1986

ИНСТИТУТ ПРОБЛЕМ МОДЕЛИРОВАНИЯ В ЭНЕРГЕТИКЕ АН УССР

ГРЕЗДОВ ГЕННАДИЙ ИВАНОВИЧ, РОМАНЦОВ ВЛАДИМИР ПЕТРОВИЧ, КОСМАЧ ЮЛИЙ ПЕТРОВИЧ, НОВИЦКИЙ АЛЕКСАНДР ФЕДОРОВИЧ

МПК / Метки

МПК: G06G 7/14

Метки: аналого-цифровой, сумматор

Опубликовано: 07.06.1987

Код ссылки

<a href="https://patents.su/4-1316006-analogo-cifrovojj-summator.html" target="_blank" rel="follow" title="База патентов СССР">Аналого-цифровой сумматор</a>

Предыдущий патент: Пневматическое устройство прямого предварения

Следующий патент: Умножитель частоты

Случайный патент: Токосъемник