Дельта-кодер

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

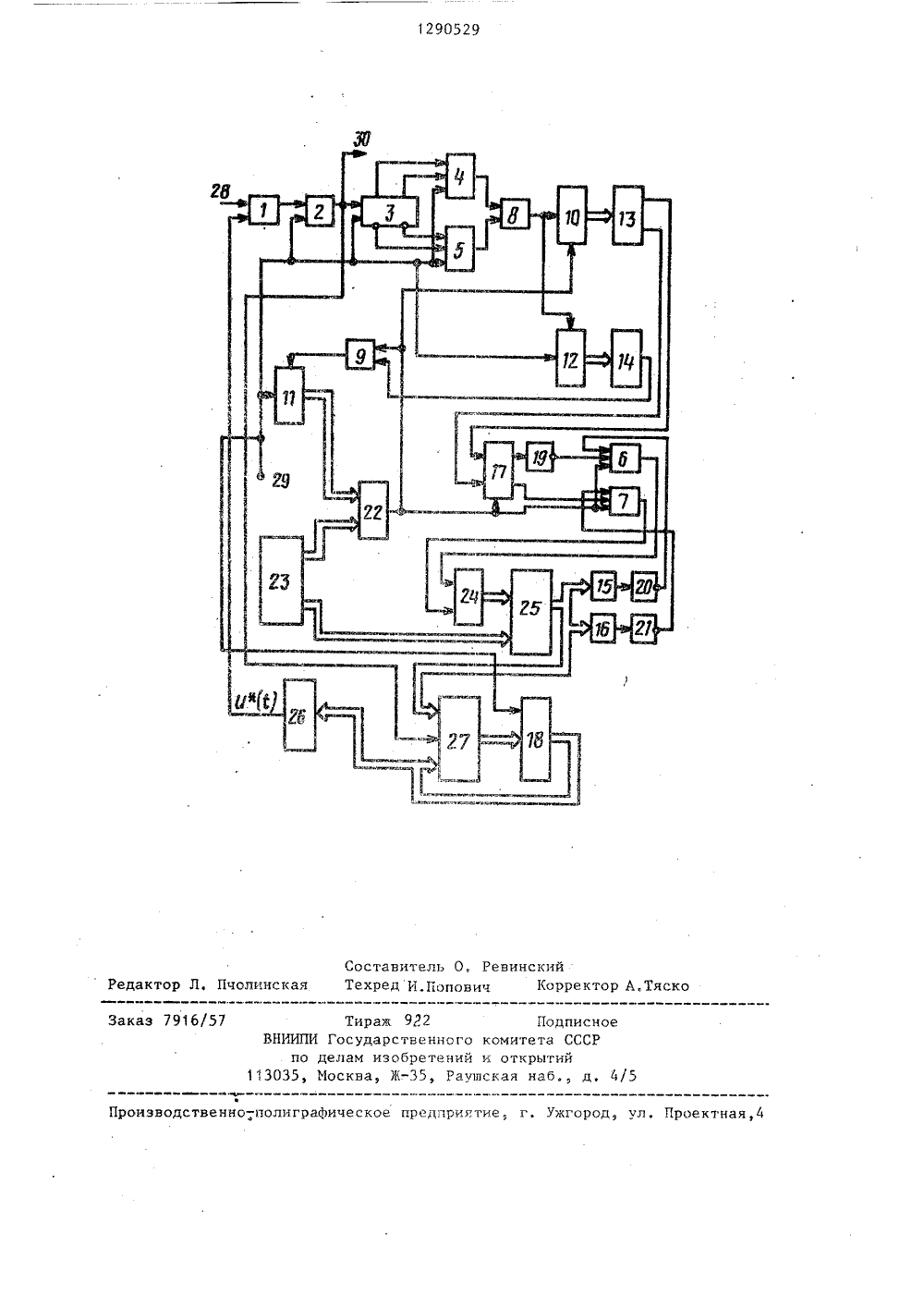

,12905 1)4 Н 3 0 ТЕНИ ф ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ПИСАНИЕ ИЗОБ ВТОРСНОМУ СВИДЕТЕЛЬСТ(71) Рижский политехнический институт им. А.Я, Пельше(57) Изобретение относится к автоматике и технике связи. Его использование в системах передачи позволяет повысить функциональную наде ность и достоверность преобразования Дельта-кодер содержит компаратор, триггер, регистр сдвига, четыре элемента И, элемент ИЛИ, элемент НЕ,два счетчика, дешифратор, два буферных регистра, элемент эквивалентности, блок постоянной памяти, реверсивный счетчик, блок мультиплексоров, цифроаналоговый преобразователь и ари - метико-логический блок. Введение дополнительно счетчика, элемента ИЛИ, "двух дешифраторов и двух элемен.тов НЕ обеспечивает блокировку ре-. версивного счетчика в крайних состояниях, а также вбзможность допол-. нительной синхронизации передаваемого сигнала, 1 ил.1 12Изобретение относится к автоматике и технике связи и может использоваться в системах передачи сигналов (например, речевых).Цель изобретения - повышение функциональной надежности и достоверности преобразования.На чертеже изображена функциональная схема устройства.Дельта-кодер содержит компаратор1,- триггер 2, регистр 3 сдвига,первый 4, второй 5, третий 6 и четвер тый 7 элементы И, первый 8 и второй 9 элементы ИЛИ, первый 10, второй 11 и третий 12 счетчики, первый 13, второй 14, третий 15 и четвертый 16 дешифраторы, первый 17 и второй 18 буферные регистры, первый 19, второй 20 и третий 21 элементы,НЕ,элемент 22 эквивалентности, блок 23 постоянной памяти,реверсивный счетчик 24, блок 25 мультиплексоров, цифроаналоговый преобразователь (ЦАП) 26, арифметика-логический блок 27, информационный вход 28, вход 29 синхронизации и выход 30.Устройство работает следующим образом.Аналоговый сигнал, поступающий на информационный вход 28 устройства, сравнивается в компараторе 1 с аппроксиммирующим сигналом с ЦАП 26. Полученная цифровая последовательность дискретизируется в тригере 2 сигналом синхронизации с входа 29 и поступает на вход ЗО устройства, а также в регистр 3 сдвига. Сигналы с выходов регистра 3 анализируются элементами И 4 и 5, ИЛИ 8, первым счетчиком 10 и первым дешифратором 13. Одновременно второй счетчик 11,подсчитывает синхроимпульсы с входа 29. Результат это 1 о подсчета сравнивается на элементе 22 эквивалентности с числом из блока 23 постоянной памяти, соответствующим некоторому заранее заданному интервалу Танализа. По истечении каждого интервала Т счетчики 10 и11 обнуляются. Если при этом за время Т в выходном сигнале дельта-коАдера число сдвоенных символов (единиц или нулей) не превысило некото"рого числа Нто на выходах первогодешифратора 13 сигналы отсутствуют,если это число больше некоторогочисла Нто сигналы присутствуют на обоих выходах дешифра 90529 гтора 13. Когда число сдвоенных символов находится между Ии МиИ 6 к сигнал имеется лишь на первом выходЕдешифратора 13. С .интервалом Т сигналы с дешифратора 13 записываютсяв первый буферный регистр 17, причем сигнал с его первого выхода инвертируется элементом НЕ 19. В конце каждого интервала Тд открываются 10 элементыИ 6 и 7 и пропускают соот-ветствующие сигналы на входы реверсивного счетчика 24, В результате,если сдвоенных символов меньше Ысодержимое реверсивного счетчика 24уменьшается на единицу, а еслисдвоенных символов больше Ы.увеличивается. Сигналы с реверсивно го счетчика 24 при помощи блока 25мультиплексоров управляют подключе кием на арифметика-логический блок27 с блока 23 постоянной памяти сигналов, соответствующих требуемому(большему или меньшему) шагу кванг 5тования. Арифметика-логический блок27 в сочетании со вторым буфернымрегистром 18 и ЦАП 26 представляетблок восстановления аппроксимирующего напряжения.Третий счетчик 12 ведет подсчет 30 синхроимпульсов с входа 29, приэтом наличие в выходном сигналедельта-кодера сдвоенных импульсоввызывает обнуление этого счетчика 12.,Таким образам счетчик 12 подсчиты вает число синхроимпульсов в паузахвходного сигнала и при достижениинекоторого числа, выбранного с учетом того, что в сигнале холостогохода дельта-кодера практически отсутствуют шумы свободного канала,второй дешифратор 14,выдает сигнал,ко"тарый через второй элемент ИЛИ 9 обнуляет второй счетчик 11. Так какэто происходит одновременно в кодере и декодере, то по окончании паузы второй счетчик 11 кодера и аналогичный счетчик декодера работаютсинхронно, благодаря чему повышается функциональная надежность и дос"товерность преобразования.Третий и четвертый дешифраторы15 и 16 фиксируют состояния реверсивного счетчика 24, соответствующиеминимальному и максимальному шагу квантования. Сигналы с этих дешифраторов после инвертирования на элементах НЕ 20 и 21 запрещают прохождение сигналов через элементы И 6 и7 на соответствующие входы реверсивного счетчика 24. В результате этого предотвращается переход кодера в режиме холостого хода от минимального и максимальному шагу квантования, а в режиме перегрузки по крутизне от максимального к минимальному, что обеспечивает быстрое вхождение кодера в нормальный режим по окончании перегрузки, а также повьппает достоверность преобразования и надежность функционирования устройства.Формула изобретения 10 40 Дельта-кодер, содержащий компа ратор, первый вход которого является информационным входом устройства, триггер, регистр сдвига, первый и второй счетчики, первый дешифратор, блок постоянной памяти, арифметико .логический блок, реверсивный счетчик, блок мультиплексоров, первый и второй буферные регистры, элемент эквивалентности, первый элемент НЕ, первый элемент ЙЛИ, первый, второй, третий и четвертый элементы И и цифроаналоговый преобразователь, выход которого соединен с вторым входом компаратора, выход которого подключен к информационному входу тригге- З 0 ра, выход которого, являющийся выходом устройства, соединен с управляющим входом арифметико-логического блока и информационным входом регистра сдвига, прямые и инверсные выходы первого и второго разрядов которого подключены к первому и второму входам соответственно первого и второго элементов И, третьи входы которых объединены с входами синхронизации регистра сдвига и триггера, счетным входом второго счетчика и входом обнуления второго буферного регистра и подключены к, входу синхронизации устройства, выходы 45 первого и второго элементов И соединены с входами первого элемента ИЛИ, выход которого подключен к счетному входу первого счетчика, выходы которого соединены с соответствующими 5 входами первого дешифратора, первый и второй выходы которого подключены к соответствующим информационным входам первого буферного регистра,первый выход которого через первыйэлемент НЕ, а второй непосредственно соединены с первыми входами соответственно третьего и четвертогоэлементов И, вторые входы которыхобъединены с входами обнуления первых счетчика и буферного регистра иподключены к выходам элемента эквивалентности, первые и вторые входыкоторого соединены соответственно свыходами второго счетчика и первымивыходами блока постоянной памяти,вторые выходы которого подключены кинформационным входам блока мультиплексоров, управляющие входы которого соединены с выходами реверсивно"о счетчика, входы прямого и обратного счета которого подключены квыходам соответственно четвертогои третьего элементов И, выходы арифметико-логического блока соединеныс.информационными входами второгобуферного регистра, выходы которогоподключены к соответствующим входамцифроаналогового преобразователя ипервым входам арифметико-логическогоблока, отличающийся тем,что, с целью повышения функциональной надежноГти и достоверности преФобразования, в него введены второй,третий и четвертый дешифраторы,второй элемент ИЛИ, второй и третийэлементы НЕ и третий счетчик, счетный вход которого объединен со счетным входом второго счетчика, входобнуления подключен к выходу первого элемента ИЛИ, а выходы соединеныс соответствующими входами второгодешифратора, выход которого подключен к первому входу второго элемента ИЛИ, второйвход которого соединен с выходом элемента эквивалентности, а выход подключен к входуобнуления второго счетчика, выходыблока мультиплексоров подключены ксоответствующим вторым входам арифметико-логического блока и входамтретьего и четвертого дешифраторов,выходы которых через соответственновторой и третий элементы НЕ соединены с третьими входами соответственно третьего и четвертого элементов И;1290529 нский Составитель О Р Техред И.Попович Редактор Л, Пчолинска орре кто я каз 7916/57 Тираж 9 Р 2 Подп Государственного комитета С елам изобретений и открытии осква, Ж.-Э 5, Раущская наб. ис СС ВНИИПИ 30 дф П зводственно-.полиграФическое предприятие, г. Ужгород, ул, Проектная,

СмотретьЗаявка

3882991, 11.04.1985

РИЖСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. А. Я. ПЕЛЬШЕ

КОТОВИЧ ГЛЕБ НИКОЛАЕВИЧ, КОМАРОВ КОНСТАНТИН СЕРГЕЕВИЧ, ПАЛКОВ АНДРЕЙ ИМАНТОВИЧ, МАЛАШОНОК ИГОРЬ МИХАЙЛОВИЧ

МПК / Метки

МПК: H03M 3/02

Метки: дельта-кодер

Опубликовано: 15.02.1987

Код ссылки

<a href="https://patents.su/4-1290529-delta-koder.html" target="_blank" rel="follow" title="База патентов СССР">Дельта-кодер</a>

Предыдущий патент: Дельта-модулятор

Следующий патент: Дифференциальный импульсный кодер телевизионного сигнала

Случайный патент: Землеройно-метательная машина