Стереодекодер

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

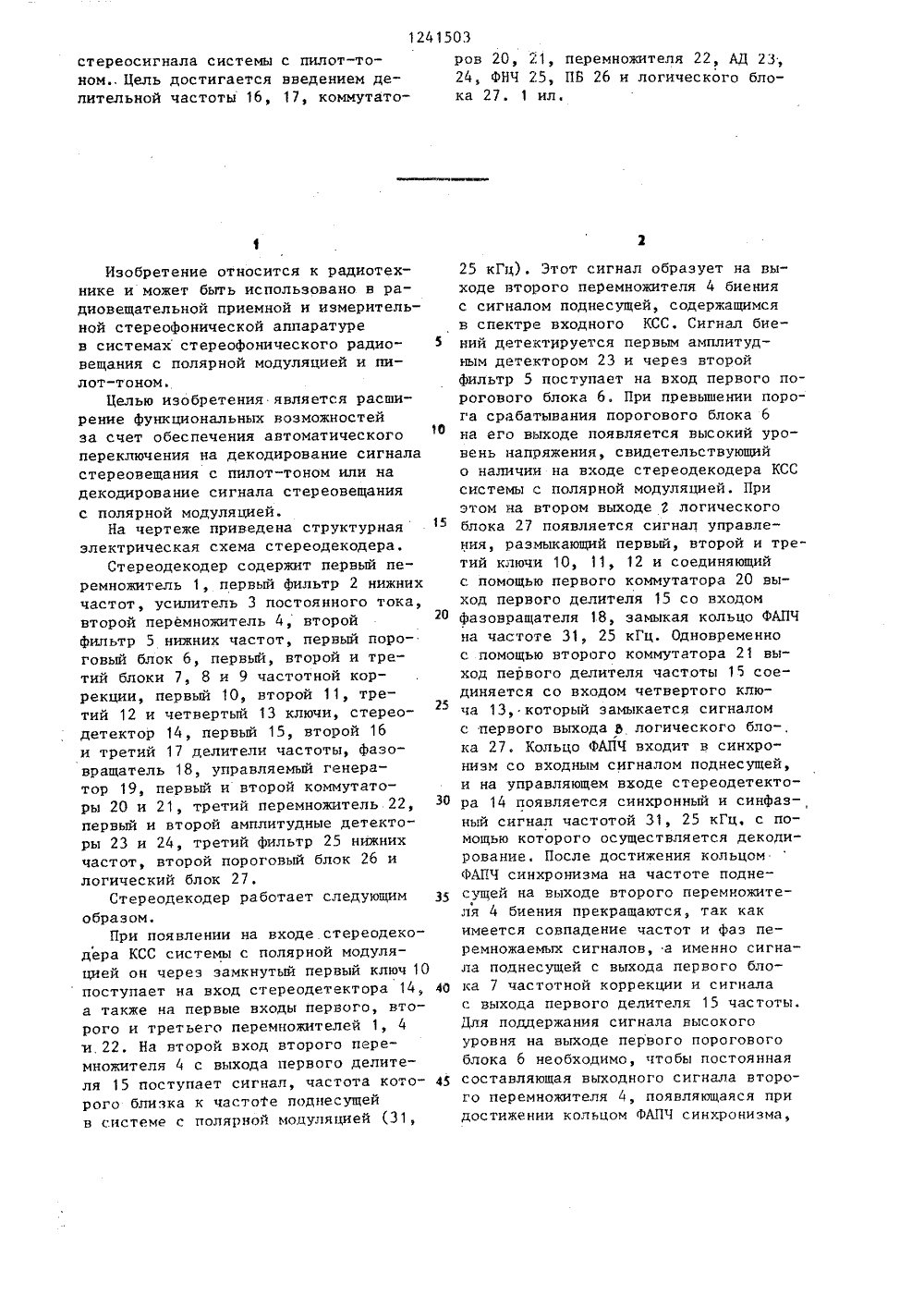

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 119) 111) а)4 Н 04 Н 40 ИСАНИЕ ИЗОБРЕТЕНИ ГОСУДАРСТ 8 ЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВ(57) Изобретение относится к радиотехнике. Расширяются функциональные возможности за счет обеспечения автоматического переключения на декодирование сигнала стереовещания с пилот-тоном. Устр-во содержит три перемножителя 1, 4 и 22, три ФНЧ 2, 5 и 25, усилитель постоянного тока 3, два пороговых блока (ПБ) 6 и 26, три блока частотной коррекции 7, 8 и 9,четыре ключа 10; 11, 12 и 13, стерео детектор 14, три делителя частоты 15 16 и 17, фазовращатель 18, управляемый генератор 19, два коммутатора 20 и 21, два амплитудных детектора (АД) 23 и 24 и логический блок 27. При поступлении на вход устр-ва комплексного стереосигнала системы с пи лот-тоном на выходе перемножителя 22 образуются биения сигнала пилот-тона содержащегося в спектре входного сиг нала, и сигнала с выхода делителя частоты 17, частота которого близка к частоте пилот-тона. Сигнал биений детектируется АД 24 и через ФНЧ 25 поступает на вход ПБ 26. При превышении порога срабатывания ПБ 26 на его выходе появляется высокий уровен напряжения, свидетельствующий о наяичии на входе устр-ва комппексногоЮмхИ4124 1503стереосигнала системы с пилот-то- ров 20, 21, перемножителя 22, АД 23, ном Цель достигается введением де, ФНЧ 25, ПБ 26 и логического блолительной частоты 16, 17, коммутато- ка 27. 1 ил.Изобретение относится к радиотехнике и может быть использовано в радиовещательной приемной и измерительной стереофонической аппаратуре в системах стереофонического радиовещания с полярной модуляцией и пилот-тоном.Целью изобретения является расширение функциональных возможностей за счет обеспечения автоматического переключения на декодирование сигнала стереовещания с пилот-тоном или на декодирование сигнала стереовещания с полярной модуляцией.На чертеже приведена структурная электрическая схема стереодекодера.Стереодекодер содержит первый перемножитель 1, первый фильтр 2 нижних частот, усилитель 3 постоянного тока, второй перемножитель 4, второй фильтр 5 нижних частот, первый пороговый блок 6, первый, второй и третий блоки 7, 8 и 9 частотной коррекции, первый 10, второй 11, третий 12 и четвертый 13 ключи, стерео- детектор 14, первый 15, второй 16 и третий 17 делители частоты, фазовращатель 18, управляемый генератор 19, первый и второй коммутаторы 20 и 21, третий перемножитель 22, первый и второй амплитудные детекторы 23 и 24, третий фильтр 25 нижних частот, второй пороговый блок 26 и логический блок 27.Стереодекодер работает следующим образом.При появлении на входе стереодекодера КСС системы с полярной модуляцией он через замкнутый первый ключ 10 поступает на вход стереодетектора 14, а также на первые входы первого, второго и третьего перемножителей 1, 4 и 22. На второй вход второго пере- множителя 4 с выхода первого делителя 15 поступает сигнал, частота которого близка к частоте поднесущей в системе с полярной модуляцией (31,5 10 15 20 25 ЗО 35 40 45 25 кГц). Этот сигнал образует на выходе второго перемножителя 4 биения с сигналом поднесущей, содержащимся в спектре входного КСС. Сигнал биений детектируется первым амплитудным детектором 23 и через второй фильтр 5 поступает на вход первого порогового блока 6, При превышении порога срабатывания порогового блока 6 на его выходе появляется высокий уровень напряжения, свидетельствующий о наличии на входе стереодекодера КСС системы с полярной модуляцией. При этом на втором выходе 3 логического блока 27 появляется сигнал управления, размыкающий первый, второй и третий ключи 10, 1, 12 и соединяющий с помощью первого коммутатора 20 выход первого делителя 15 со входом фазовращателя 18, замыкая кольцо ФАПЧ на частоте 31, 25 кГц. Одновременно с помощью второго коммутатора 21 выход первого делителя частоты 15 соединяется со входом четвертого ключа 13, который замыкается сигналом с первого выхода В логического бло-,Гка 27, Кольцо ФАПЧ входит в синхронизм со входным сигналом поднесущей, и на управляющем входе стереодетектора 14 появляется синхронный и синфазный сигнал частотой 31, 25 кГц, с помощью которого осуществляется декодирование. После достижения кольцом ФАПЧ синхронизма на частоте подне - сущей на выходе второго перемножителя 4 биения прекращаются, так как имеется совпадение частот и фаз перемножаемых сигналов, а именно сигнала поднесущей с выхода первого блока 7 частотной коррекции и сигнала с выхода первого делителя 15 частоты. Для подцержания сигнала высокого уровня на выхоце первого порогового блока б необхоцимо, чтобы постоянная составляющая выходного сигнала второго перемножителя 4, появляющаяся при достижении кольцом ФАПЧ синхронизма, 1241503передавалась через первый амплитудный детектор 23 и второй фильтр 5 к входу первого порогового блока 6, т.е. первый амплитудный детектор 23 должен пропускать постоянную состав ляющую.При появлении на входе стереодекодера КСС системы с пилот-тоном, он через первый блок 7 поступает на первые входы первого, второго и10 третьего перемножителей 1, 4 и 22.На другой вход третьего перемножителя 22 с выхода третьего делителя 17 поступает сигнал с частотой, близкой к частоте пилот-тона 19 кГц, 15 Этот сигнал образует на выходе третьего перемножителя 22 биения с сигналом пилот-тона, содержащемся в спект - ре входного КСС. Сигнал биений детектируется вторым амплитудным детекто ром 24 и через третий фильтр 25поступает на вход второго порогового блока 26, при превыщении порога срабатывания которого на его выходе появляется высокий уровень напряжения, свидетельствующий о наличии на входе стереодекодера КСС системы с пилот- тоном. При этом на втором выходе 2 логического блока 27 появляется сигнал управления, замыкающий первый, 30 второй и третий ключи 10, 11 и 12 и соединяющий с помощью первого коммутатора 20 выход третьего делителя 17 частоты со входом фазовращателя 18, замыкая кольцо ФАПЧ, на час тоте 19 кГц, Одновременно с помощью второго коммутатора 21 выход второго делителя 16 частоты соединяется со входом четвертого ключа 13, который замыкается сигналом первого выхо да Ь логического блока 27, Кольцо ФАПЧ входит в синхронизм со входным сигналом пилот-тона, и на управляющем входе стереодетектора 14 появля- ется синхронный и синфазный сигнал частотой 38 кГц, с помощью которого осуществляется декодирование. После достижения кольцом ФАПЧ синхронизма на частоте пилот-тона на выходе треть- его перемножителя 22 биения прекращаются, так как имеется совпадение частот и фаз перемножаемых сигналов (сигнала пилот-тона с выхода ключа 10 и сигнала с выхода третьего делителя 17 частоты). Лля поддержания сигнала высокого уровня на выходе второго порогового блока 26 необходимо, чтобы постоянная составляющая выходного сигнала третьего перемножителя 22, проявляющаяся при достижении кольцом ФАПЧ синхронизма, передавалась через вто рой амплитудной детектор 24 и третий фильтр 25 к входу второго порогового блока 26.При появлении на входе стереодекодера моносигнала на выходах первого и второго пороговых блоков 6 и 26 будет низкий уровень ввиду отсутствия сигналов поднесущей или пилот-тона на первых входах перемножителей 4 и 22. При этом на втором выходе г логического блока 27 появляется замыкающий сигнал, первый, второй и третий ключи 10, 11 и 12. На первом выходе ь логического блока 27 появляется сигнал, размыкающий четвертый ключ 13. Таким образом, моносигнал, минуя первый блок 7 частотной коррекции через замкнутый первый ключ 10, поступает на вход 14 стереодетектора 14. Поскольку сигнал управления на стерео- детектор 14 не подается, то декодиро-. вание не происходит, и моносигнал без изменений, минуя второй и третий блоки частотной коррекции 8 и 9, через замкнутые второй и третий ключи 11, 12 поступает на входы стерео- декодера. Формула изобретенияСтереодекодер, содержащий последовательно соединенные цепь из параллельно соединенных первого блока частотной коррекции и первого ключа, первый перемножитель, первый фильтр нижних частот, усилитель постоянного тока, управляемый генератор, первый делитель частоты и второй перемножитель, второй вход которого соединен с выходом первого блока частотной коррекции и объединен с входом стереодетектора, первый и второй выходы которого подключены к цепям из параллельно соединенных второго блока частотной коррекции и второго ключа и из параллельно соединенных третьего блока частотной коррекции и третьего ключа соответственно, а также фазовращатель, выход которого подключен к второму входу первого перемножителя, четвертый ключ, выход которого подключен к управляющему входу стерео- детектора, и последовательно соединенные второй фильтр нижних частот и первый пороговый блок, причем управляющие входы первого, второго и третьего1241503 Составитель В.ШевцовРедактор А.Долинич Техред Л.Олейник Корректор В.Бутяга Заказ 36 15/57 Тираж 624 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раущская наб., д. 4/5. Ирс изноя:твенно-ттсннграфическое предприятие, г. Ужгород, ун. Проектная, 4 ключей объединены, о т л и ч а ю -щ и й с я тем, что, с целью расширения функциональных воэможностей засчет обеспечения автоматического переключения на декодирование сигналастереовещания. с пилот-тоном или надекодирование сигнала стереовещания с полярной модуляцией, в неговведены последовательно соединенныевторой и третий делители частоты ипервый коммутатор, выход которогоподключен к входу фазовращателя,второй коммутатор, выход. которогоподключен к входу четвертого ключа,первый амплитудный детектор, включенный между выходом второго перемножителя и входом второго фильтранижних частот, а также последовательно соединенные третий перемножитель,второй амплитудный детектор, третийфильтр нижних частот, второй пороговый блок и логический блок, первый выход которого подключен к управляющему входу четвертого ключа, при 5 этом второй вход второго перемножителя объединен с первым входом третьего перемножитепя, второй вход которого соединен с выходом третьегоделителя частоты, вход второго дели- О теля частоты обЪединен с входом первого делителя частоты, выход которого соединен с вторым входом первого коммутатора, управляющий входкоторого объединен с управляющимивходами первого ключа и второго коммутатора и подключен к второму выходу логического блока, второй входкоторого соединен с выходом первогопорогового блока, первый и второй 20 входы второго коммутатора соединеныс выходами соответственно первогои второго делителей частоты.

СмотретьЗаявка

3854196, 04.01.1985

ПРЕДПРИЯТИЕ ПЯ В-2322

МОРЕЙН САМУЭЛ ЗАЛЬМАНОВИЧ, ТРИЗНА ЭРНЕСТ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: H04H 5/00

Метки: стереодекодер

Опубликовано: 30.06.1986

Код ссылки

<a href="https://patents.su/4-1241503-stereodekoder.html" target="_blank" rel="follow" title="База патентов СССР">Стереодекодер</a>

Предыдущий патент: Устройство для контроля канала связи

Следующий патент: Многоканальная система с дельта-модуляцией

Случайный патент: Способ оценки качества подшипников в сборе с ротором