Запоминающее устройство с исправлением ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1236559

Автор: Делендик

Текст

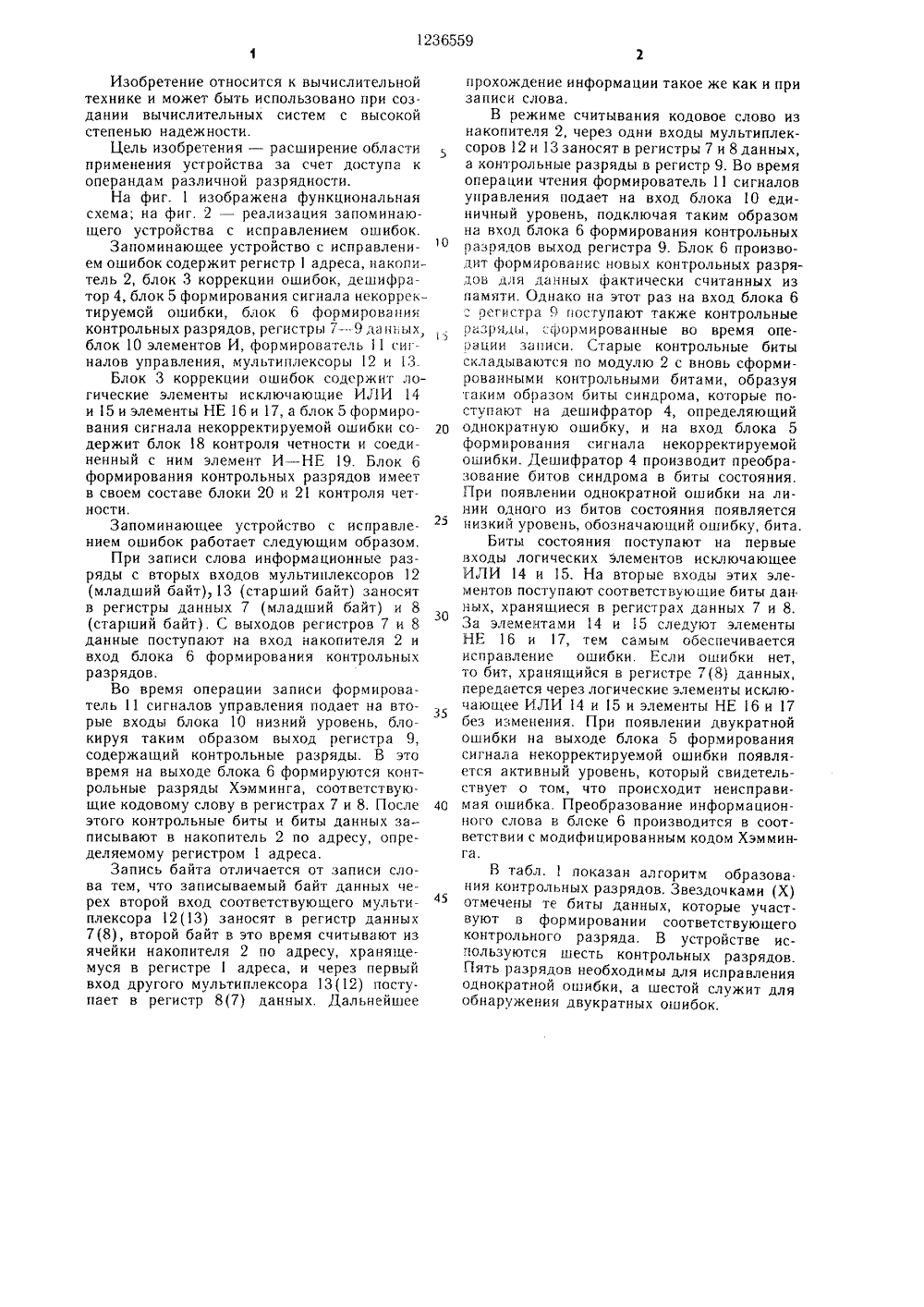

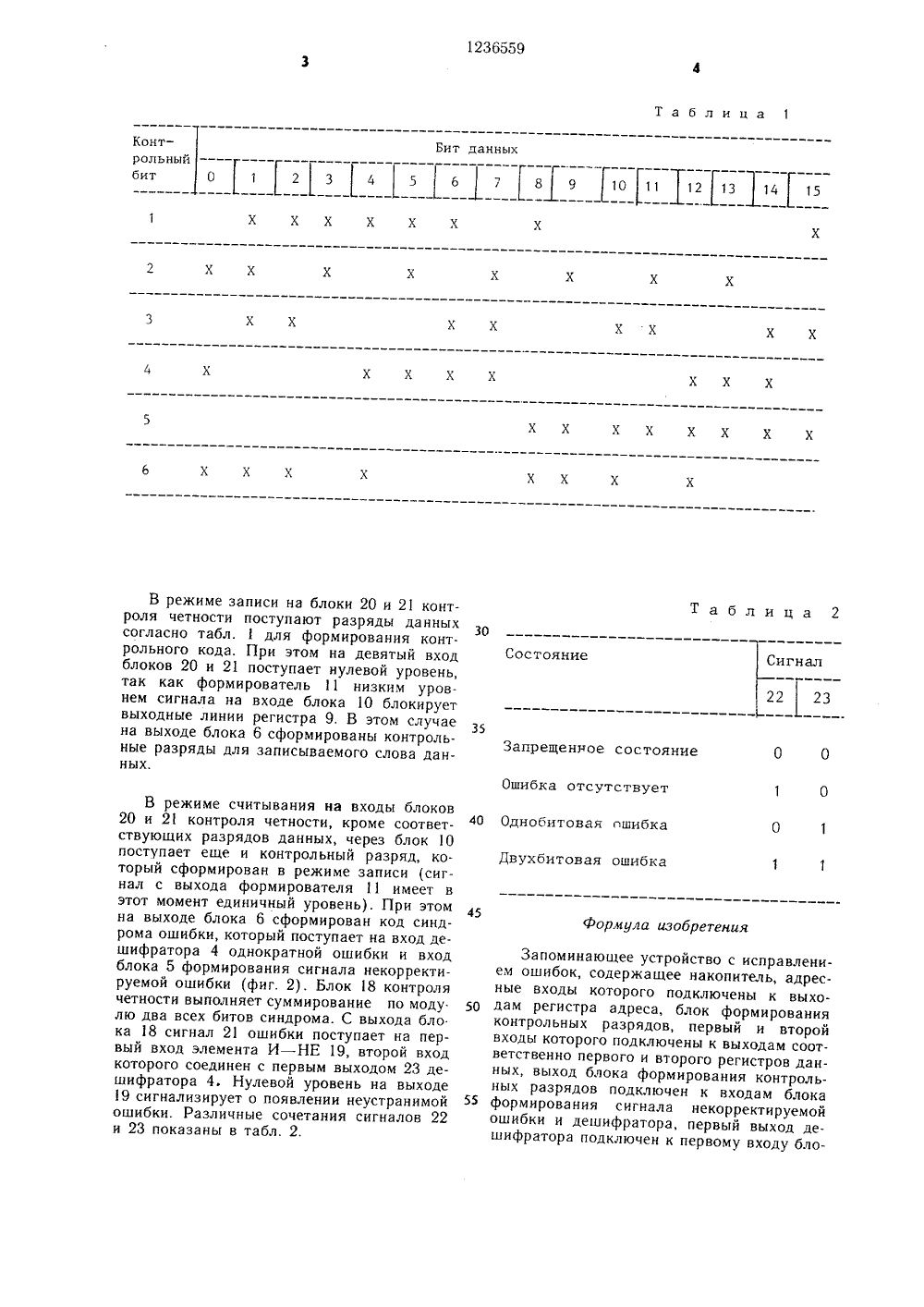

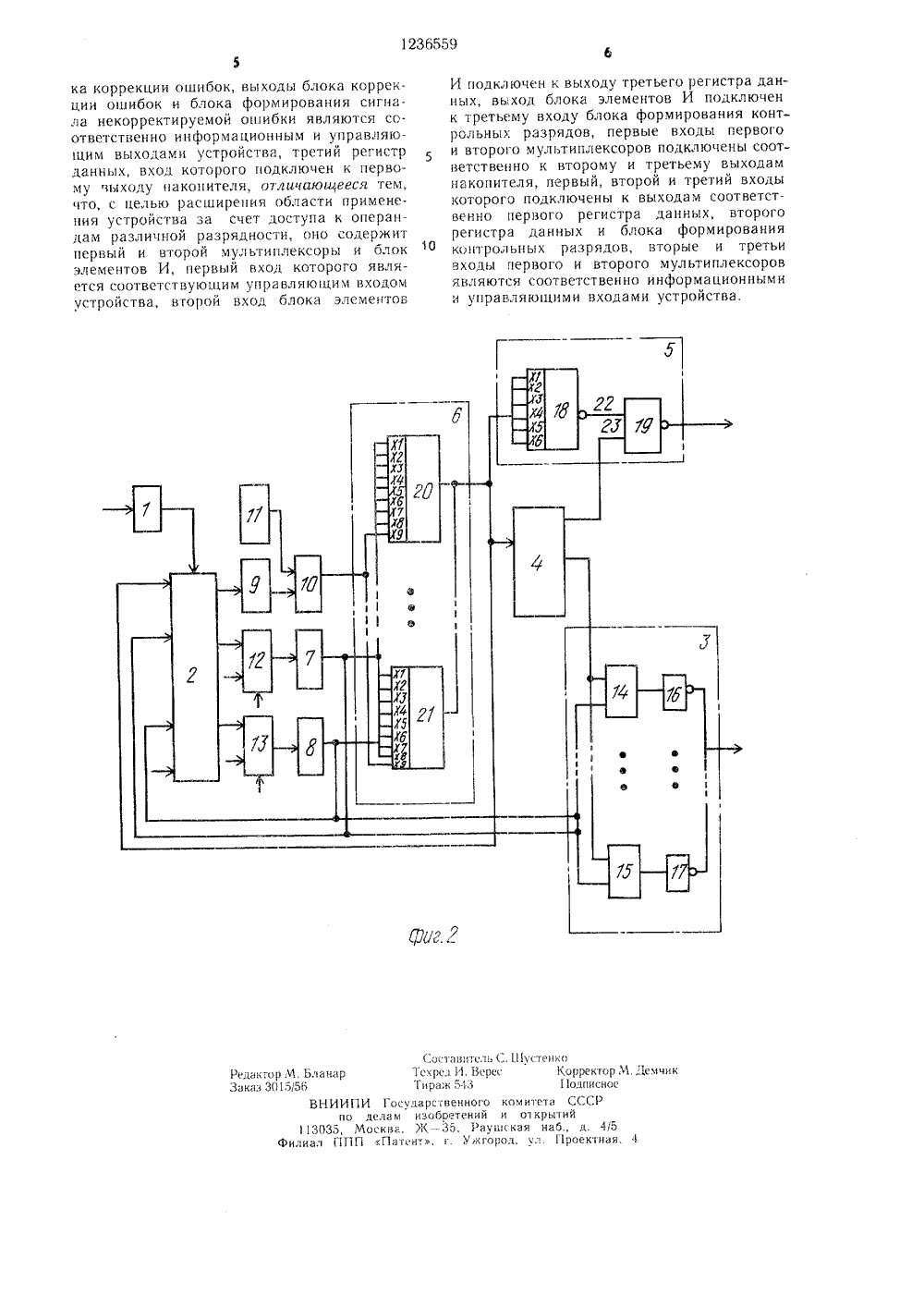

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 559 Я С 2900 ЕТЕ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ОПИСАНИЕ ИЗОБ К А ВТОРСКОМ,/ СВИДЕТЕЛЬСТ(57) Изобретение относится к вычислительной технике и может быть использовано при создании вычислительных систем с высокой степенью надежности. Целью изобретения является расширение области применения устройства за счет осуществления доступа к операндам различной разрядности. Устрой ство содержит регистр 1 адреса, накопитель 2, блок 3 коррекции ошибок, дешифратор 4, блок 5 формирования сигнала некорректируемой ошибки, блок 6 формирования контрольных разрядов, регистры 7 - 9 данных блок О элементов И, формирователь 11 сигналов управления, мультиплексоры 12 и 3. Цель изобретения достигается введением мультиплексоров и блока элементов И с соответствующими функциональными связями, 2 ил, 2 таблИзобретение относится к вычислительной технике и может быть использовано при создании вычислительных систем с высокой степенью надежности.Цель изобретения - расширение области применения устройства за счет доступа коперандам различной разрядности.На фиг. 1 изображена функциональная схема; на фиг. 2 - реализация запоминающего устройства с исправлением ошибок.Запоминающее устройство с исправлением ошибок содержит регистр 1 адреса, накопитель 2, блок 3 коррекции ошибок, дешифратор 4, блок 5 формирования сигнала некорректируемой ошибки, блок 6 формирования контрольных разрядов, регистры 7 - -9 данных,1 2 блок 10 элементов И, формирователь1 с игналов управления, мультиплексоры 12 и3.Блок 3 коррекции ошибок содержит логические элементы исключающие ИЛИ 14 и5 и элементы НЕ 16 и 17, а блок 5 формирования сигнала некорректируемой ошибки со держит блок 8 контроля четности и соединенный с ним элемент И - -НЕ 19. Блок б формирования контрольных разрядов имеет в своем составе блоки 20 и 21 контроля четности.Запоминающее устройство с исправле. нием ошибок работает следующим образом,При записи слова информационные разряды с вторых входов мультиплексоров 12 (младший байт), 13 (старший байт) заносят в регистры данных 7 (младший байт) и 8 (старший байт). С выходов регистров 7 и 8 данные поступают на вход накопителя 2 и вход блока 6 формирования контрольных разрядов.Во время операции записи формирователь 11 сигналов управления подает на вторые входь 1 блока 10 низний уровень, блокируя таким образом выход регистра 9, содержащий контрольные разряды. В это время на выходе блока 6 формируются контрольные разряды Хэмминга, соответствующие кодовому слову в регистрах 7 и 8, После 40 этого контрольные биты и биты данных за писывают в накопитель 2 по адресу, определяемому регистром 1 адреса.Запись байта отличается от записи слова тем, что записываемый байт данных черех второй вход соответствующего мультиплексора 12(13) заносят в регистр данных 7(8), второй байт в это время считывают из ячейки накопителя 2 по адресу, хранящемуся в регистре 1 адреса, и через первый вход другого мультиплексора 13(12) поступает в регистр 8(7) данных. Дальнейшее прохождение информации такое же как и при записи слова.В режиме считывания кодовое слово из накопителя 2, через одни входы мультиплексоров 12 и 13 заносят в регистры 7 и 8 данных, а контрольные разряды в регистр 9. Во время операции чтения формирователь 11 сигналов управления подает на вход блока 10 единичный уровень, подключая таким образом на вход блока 6 формирования контрольных разрядов выход регистра 9. Блок 6 производит формирование новых контрольных разрядов для данных фактически считанных из памяти. Однако на этот раз на вход блока 6 : регистра 9 поступают также контрольные разряды, .формированные во время операции записи. Старые контрольные биты складываются по модулю 2 с вновь сформированными контрольными битами, образуя таким образом биты синдрома, которые поступают на дешифратор 4, определяющий однократную ошибку, и на вход блока 5 формирования сигнала некорректируемой ошибки. Дешифратор 4 производит преобразование битов синдрома в биты состояния. При появлении однократной ошибки на линии одного из битов состояния появляется низкий уровень, обозначающий ошибку, бита,Биты состояния поступают на первые входы логических элементов исключающее ИЛИ 14 и 15. На вторые входы этих элементов поступают соответствующие биты дан ных, хранящиеся в регистрах данных 7 и 8. За элементами 14 и 15 следуют элементы НЕ 16 и 17, тем самым обеспечивается исправление ошибки. Если ошибки нет, то бит, хранящийся в регистре 7(8) данных, передается через логические элементы исключающее ИЛИ 14 и 15 и элементы НЕ 16 и 17 без изменения. При появлении двукратной ошибки на выходе блока 5 формирования сигнала некорректируемой ошибки появляется активный уровень, который свидетельствует о том, что происходит неисправимая ошибка. Преобразование информационного слова в блоке 6 производится в соответствии с модифицированным кодом Хэмминга.В табл. 1 показан алгоритм образова.ния контрольных разрядов. Звездочками (Х) отмечены те биты данных, которые участвуют в формировании соответствующего контрольного разряда. В устройстве используются шесть контрольных разрядов.Пять разрядов необходимы для исправления однократной ошибки, а шестой служит для обнаружения двукратных ошибок.1236559 Таблица 1 Бит данных Контрольныйбит 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 Х Х Х Х Х Х Х Х Х Х Х Х Х Х Х Х Х Х Х Х Х Х Х Х Х Х Х Х Х Х Х Х Таблица 2 В режиме записи на блоки 20 и 21 контроля четности поступают разряды данныхсогласно табл. 1 для формирования контрольного кода. При этом на девятый вход Состояниеблоков 20 и 21 поступает нулевой уровень,так как формирователь 11 низким уровнем сигнала на входе блока 10 блокируетвыходные линии регистра 9. В этом случаена выходе блока 6 сформированы контрольные разряды для записываемого слова данных,игна 2 23 апрещениое состояние Ошибка отсутствуе О Однобитовая ошиб ухбитовая ошибка ормула изобретения В режиме считывания на входы блоков 20 и 21 контроля четности, кроме соответ ствующих разрядов данных, через блок О поступает еще и контрольный разряд, который сформирован в режиме записи (сигнал с выхода формирователя 11 имеет в этот момент единичный уровень). При этом 45 на выходе блока 6 сформирован код синдрома ошибки, который поступает на вход дешифратора 4 однократной ошибки и вход блока 5 формирования сигнала некорректируемой ошибки (фиг. 2). Блок 18 контроля четности выполняет суммирование по моду 50 лю два всех битов синдрома. С выхода бло.ка 18 сигнал 21 ошибки поступает на первый вход элемента И - НЕ 19, второй вход которого соединен с первым выходом 23 дешифратора 4. Нулевой уровень на выходе 19 сигнализирует о появлении неустранимой 55 ошибки. Различные сочетания сигналов 22 и 23 показаны в табл. 2. Запоминающее устроиство с исправлением ошибок, содержащее накопитель, адресные входы которого подключены к выходам регистра адреса, блок формирования контрольных разрядов, первый и второй входы которого подключены к выходам соответственно первого и второго регистров данных, выход блока формирования контрольных разрядов подключен к входам блока формирования сигнала некорректируемой ошибки и дешифратора, первый выход дешифратора подключен к первому входу бло1236559 Составители С. 114 стенко Редактор М. планар Тсхрел И. Верее Корректор М. 1 емчик Заказ 3015,56 паз одписное ВНИИПИ Государственного комитета СССР по делам изобретений и от крытий 13035, Москва, Ж - 35, Раунккаи наб., д. 4/5 Фила ППП Патент, и. У;ксОрод, мл Проектнаи, 4ка коррекции ошибок, выходы блока коррекции ошибок и блока формирования сигнала некорректирусмой ошибки являются со. ответственно информационным и управляющим выходами устройства, третий регистр данных, вход которого подключен к первому выходу накопителя, отличаюцггся тем, что, с целью расширения области применения устройства за счет доступа к операндам различной разрядности, оно содержит первый и второй мультиплексоры и блок элементов И, первый вход которого является соответствующим управляющим входом устройства, второй вход блока элементов И подключен к выходу третьего регистра данных, выход блока элементов И подключен к третьему входу блока формирования контрсльных разрядов, первые входы первого и второго мультиплексоров подключены соответственно к второму и третьему выходам накопителя, первый, второй и третий входы которого подключены к выходам соответственно первого регистра данных, второго регистра данных и блока формирования коп 1 рольных разрядов, вторые и третьи входы первого и второго мультиплексоров являются соответственно информационными и управлянэщими входами устройства.

СмотретьЗаявка

3796028, 28.09.1984

ПРЕДПРИЯТИЕ ПЯ Р-6024

ДЕЛЕНДИК ИВАН НИКОЛАЕВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: запоминающее, исправлением, ошибок

Опубликовано: 07.06.1986

Код ссылки

<a href="https://patents.su/4-1236559-zapominayushhee-ustrojjstvo-s-ispravleniem-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство с исправлением ошибок</a>

Предыдущий патент: Устройство для контроля памяти

Следующий патент: Запоминающее устройство

Случайный патент: Устройство для вывода информации